Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ahj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                               | Description                                                                                                                                                                                 | Page<br>No.                                                |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Dec<br>2012 | 27                | Port Alternate Function Map-<br>ping (Non 8-Pin Parts), Port<br>Alternate Function Mapping (8-<br>Pin Parts)                  | Added missing Port D data to Table 15; cor-<br>rected active Low status (set overlines) for<br>PA0 (T0OUT), PA2 (RESET) and PA5<br>(T1OUT) in Table 16.                                     | <u>40, 43</u>                                              |

| Sep<br>2011 | 26                | LED Drive Enable Register                                                                                                     | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Flash Sector Protect Regis-<br>ter description; revised Packaging chapter. | <u>53,</u><br><u>157,</u><br>245                           |

| Sep<br>2008 | 25                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Added references to F042A Series back in Table 1, Table 5, Table 7 and Table 14.                                                                                                            | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| May<br>2008 | 24                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Changed title to Z8 Encore! XP F082A Series<br>and removed references to F042A Series in<br>Table 1, Table 5, Table 7 and Table 14.                                                         | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| Dec<br>2007 | 23                | Pin Description, General-Pur-<br>pose Input/Output, Watchdog<br>Timer                                                         | Updated Figure 3, Table 15, Tables 60 through 62.                                                                                                                                           | <u>9, 40,</u><br><u>97</u>                                 |

| Jul<br>2007 | 22                | Electrical Characteristics                                                                                                    | Updated Tables 16 and 132; power con-<br>sumption data.                                                                                                                                     | <u>43,</u><br>229                                          |

| Jun<br>2007 | 21                | n/a                                                                                                                           | Revision number update.                                                                                                                                                                     | All                                                        |

iii

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Figure 25   | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface;                                  |

|-------------|-------------------------------------------------------------------------------------------------------|

| 1 15010 201 | #2 of 2                                                                                               |

| Figure 26.  | OCD Data Format                                                                                       |

| Figure 27.  | Recommended 20MHz Crystal Oscillator Configuration 199                                                |

| Figure 28.  | Connecting the On-Chip Oscillator to an External RC Network 201                                       |

| Figure 29.  | Typical RC Oscillator Frequency as a Function of the External Capacitance with a $45k\Omega$ Resistor |

| Figure 30.  | Opcode Map Cell Description 222                                                                       |

| Figure 31.  | First Opcode Map                                                                                      |

| Figure 32.  | Second Opcode Map after 1FH 225                                                                       |

| Figure 33.  | Typical Active Mode IDD Versus System Clock Frequency 231                                             |

| Figure 34.  | Port Input Sample Timing 240                                                                          |

| Figure 35.  | GPIO Port Output Timing 241                                                                           |

| Figure 36.  | On-Chip Debugger Timing                                                                               |

| Figure 37.  | UART Timing With CTS 243                                                                              |

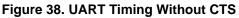

| Figure 38.  | UART Timing Without CTS 244                                                                           |

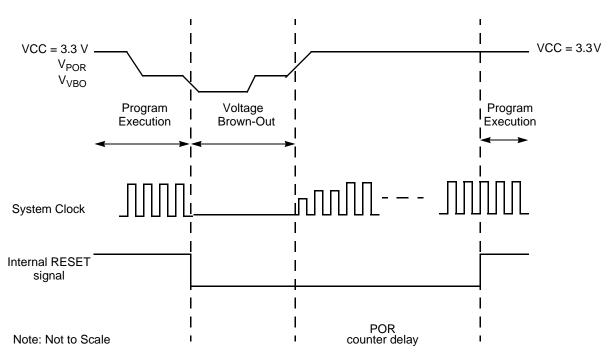

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

### Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

### Table 12. Reset and Stop Mode Recovery Bit Descriptions

**Note:** Asserting any power control bit disables the targeted block regardless of any enable bits contained in the target block's control registers.

>

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See **the** <u>Timers</u> **chapter on page 70** for more details.

**Caution:** For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF subregister. As a result, spurious transitions through unwanted alternate function modes will be prevented.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) Register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See **the** <u>Electrical Characteristics</u> chapter on page 226 for the maximum total current for the applicable package.

# **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/open-drain output reset until the software reconfigures it. The PD0 pin is an output-only open drain when in GPIO mode. There are no pull-up, High Drive, or Stop Mode Recovery source features associated with the PD0 pin.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its **RESET** alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>RFF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit          | 7                                                                                                                                                                                                       | 6                                                                                                                                                                                         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| Field        | PA7VS                                                                                                                                                                                                   | PA6CS Reserved                                                                                                                                                                            |     |     |     |     |     |     |  |  |

| RESET        | 0                                                                                                                                                                                                       | 0                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W          | R/W                                                                                                                                                                                                     | R/W                                                                                                                                                                                       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address      |                                                                                                                                                                                                         |                                                                                                                                                                                           |     | FC  | EH  |     |     |     |  |  |

| Bit          | Description                                                                                                                                                                                             |                                                                                                                                                                                           |     |     |     |     |     |     |  |  |

| [7]<br>PA7VS | 0 = PA7 is u                                                                                                                                                                                            | <ul> <li>PA7/LVD Selection</li> <li>0 = PA7 is used for the interrupt for PA7VS interrupt request.</li> <li>1 = The LVD is used for the interrupt for PA7VS interrupt request.</li> </ul> |     |     |     |     |     |     |  |  |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator is used for the interrupt for PA6CS interrupt request.</li> </ul> |                                                                                                                                                                                           |     |     |     |     |     |     |  |  |

| [5:0]        | Reserved                                                                                                                                                                                                |                                                                                                                                                                                           |     |     |     |     |     |     |  |  |

#### Table 48. Shared Interrupt Select Register (IRQSS)

These bits are reserved and must be programmed to 000000.

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7   | 6          | 5          | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------|------------|-----|-----|-----|-----|-----|--|

| Field   | TEN | TPOL       | PRES TMODE |     |     |     |     |     |  |

| RESET   | 0   | 0          | 0          | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W        | R/W        | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F07H, F0FH |            |     |     |     |     |     |  |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

### **WDT Reset in Normal Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1. For more information about system reset, see the <u>Reset, Stop Mode</u> <u>Recovery and Low Voltage Detection</u> chapter on page 22.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following WDT time-out in STOP Mode.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. Observe the following steps to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU) with the appropriate time-out value.

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH) with the appropriate time-out value.

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL) with the appropriate time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page; see Tables 100 and 101 on page 173 for details. Loading these values

PRELIMINARY

### **Output Data**

The output format of the corrected ADC value is shown below.

| MSB |   |   |   |   |   |   |   |   | Г | SB |   |   |   |   |   |

|-----|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|

| S   | v | b | а | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | _ | - |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary flag. For a normal (nonoverflow) sample, the sign and the overflow bit match. If the sign bit and overflow bit do not match, a computational overflow has occurred.

# **Input Buffer Stage**

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See <u>Table 139</u> on page 236 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

# **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register 0 (ADCCTL0): see page 134

ADC Control/Status Register 1 (ADCCTL1): see page 136

ADC Data High Byte Register (ADCD\_H): see page 137

ADC Data Low Byte Register (ADCD L): see page 137

| Bit    | Description (Continued)                                                                     |

|--------|---------------------------------------------------------------------------------------------|

| [5:2]  | Internal Reference Voltage Level                                                            |

| REFLVL | This reference is independent of the ADC voltage reference. Note: 8-pin devices contain two |

|        | additional LSBs for increased resolution.                                                   |

|        | For 20-/28-pin devices:                                                                     |

|        | 0000 = 0.0 V                                                                                |

|        | 0001 = 0.2 V                                                                                |

|        | 0010 = 0.4 V                                                                                |

|        | 0011 = 0.6 V                                                                                |

|        | 0100 = 0.8 V                                                                                |

|        | 0101 = 1.0 V (Default)                                                                      |

|        | 0110 = 1.2 V                                                                                |

|        | 0111 = 1.4 V                                                                                |

|        | 1000 = 1.6 V                                                                                |

|        | 1001 = 1.8 V                                                                                |

|        | 1010–1111 = Reserved                                                                        |

### 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7                             | 6            | 5              | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------|--------------|----------------|-----|-----|-----|-----|-----|

| Field     | WDTCALL                       |              |                |     |     |     |     |     |

| RESET     | U                             | U            | U              | U   | U   | U   | U   | U   |

| R/W       | R/W                           | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 007FH |              |                |     |     |     |     |     |

| Note: U = | Unchanged b                   | y Reset. R/W | / = Read/Write | Э.  |     |     |     |     |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

# **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field     | S_NUM                                           |     |     |     |     |     |     |     |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address   | Information Page Memory 001C-001F               |     |     |     |     |     |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251 \mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

| Bit              | 7        | 6 | 5 | 4    | 3  | 2   | 1   | 0 |

|------------------|----------|---|---|------|----|-----|-----|---|

| Field            | Reserved |   |   | RCPY | PF | AWE | DWE |   |

| Default<br>Value | 0        | 0 | 0 | 0    | 0  | 0   | 0   | 0 |

#### Table 106. Write Status Byte

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved<br>These bits are reserved and must be programmed to 0000.                                         |

| [3]   | <b>Recopy Subroutine Executed</b>                                                                           |

| RCPY  | A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]   | <b>Power Failure Indicator</b>                                                                              |

| PF    | A power failure or system reset occurred during the most recent attempted write to the NVDS array.          |

| [1]   | Address Write Error                                                                                         |

| AWE   | An address byte failure occurred during the most recent attempted write to the NVDS array.                  |

| [0]   | Data Write Error                                                                                            |

| DWE   | A data byte failure occurred during the most recent attempted write to the NVDS array.                      |

in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP F082A Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

| Bit   | 7       | 6     | 5      | 4 | 3        | 2 | 1 | 0   |

|-------|---------|-------|--------|---|----------|---|---|-----|

| Field | DBGMODE | BRKEN | DBGACK |   | Reserved |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0        | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R        | R | R | R/W |

Table 110. OCD Control Register (OCDCTL)

#### Bit Description

#### [7] **DEBUG Mode** DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0. 0 = The Z8 Encore! XP F082A Series device is operating in NORMAL Mode. 1 = The Z8 Encore! XP F082A Series device is in DEBUG Mode. [6] **Breakpoint Enable** BRKEN This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL Register is automatically set to 1. 0 = Breakpoints are disabled. 1 = Breakpoints are enabled.

### Table 123. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

#### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | SIC         | Push using Extended Addressing                                          |

#### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

|                          |                                                                | V <sub>DD</sub> = 3.0 V to 3.6 V<br>T <sub>A</sub> = 0°C to +70°C<br>(unless otherwise stated) |              |            |                                |                                                                                                |  |

|--------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------|------------|--------------------------------|------------------------------------------------------------------------------------------------|--|

| Symbol                   | Parameter                                                      | Minimum                                                                                        | Typical      | Maximum    | Units                          | Conditions                                                                                     |  |

|                          | Resolution                                                     | 10                                                                                             |              | _          | bits                           |                                                                                                |  |

|                          | Differential Nonlinearity (DNL)                                | -1.0                                                                                           | -            | 1.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$               |  |

|                          | Integral Nonlinearity (INL)                                    | -3.0                                                                                           | -            | 3.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$               |  |

|                          | Offset Error with Calibra-<br>tion                             |                                                                                                | <u>+</u> 1   |            | LSB <sup>3</sup>               |                                                                                                |  |

|                          | Absolute Accuracy with Calibration                             |                                                                                                | <u>+</u> 3   |            | LSB <sup>3</sup>               |                                                                                                |  |

| V <sub>REF</sub>         | Internal Reference Volt-<br>age                                | 1.0<br>2.0                                                                                     | 1.1<br>2.2   | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                                         |  |

| V <sub>REF</sub>         | Internal Reference Varia-<br>tion with Temperature             |                                                                                                | <u>+</u> 1.0 |            | %                              | Temperature variation with $V_{DD} = 3.0$                                                      |  |

| V <sub>REF</sub>         | Internal Reference Volt-<br>age Variation with V <sub>DD</sub> |                                                                                                | <u>+</u> 0.5 |            | %                              | Supply voltage varia-<br>tion with $T_A = 30^{\circ}C$                                         |  |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output<br>Impedance                           |                                                                                                | 850          |            | W                              | When the internal ref-<br>erence is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                          | Single-Shot Conversion<br>Time                                 | -                                                                                              | 5129         | _          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |

|                          |                                                                |                                                                                                | 10258        |            |                                | Temperature sensor measurement                                                                 |  |

#### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

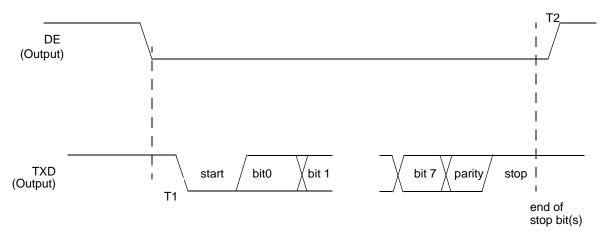

Figure 38 and Table 147 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 147 | UART T | imina Wit   | hout CTS |

|-----------|--------|-------------|----------|

|           |        | mining with |          |

|                |                                                                        | Delay (ns)                 |            |  |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                        |            |  |  |  |  |

| Part Number                                                                     | Flash | RAM   | NVDS | // Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------------------------------|-------|-------|------|----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A Series with 2 KB Flash<br>Standard Temperature: 0°C to 70°C |       |       |      |          |            |                     |                     |                |            |                    |                     |

| Z8F021APB020SG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F021AQB020SG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F021ASB020SG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F021ASH020SG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F021AHH020SG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F021APH020SG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F021ASJ020SG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F021AHJ020SG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F021APJ020SG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C                                            |       |       |      |          |            |                     |                     |                |            |                    |                     |

| Z8F021APB020EG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F021AQB020EG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F021ASB020EG                                                                  | 2 KB  | 512 B | 64 B | 6        | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F021ASH020EG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F021AHH020EG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F021APH020EG                                                                  | 2 KB  | 512 B | 64 B | 17       | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F021ASJ020EG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F021AHJ020EG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F021APJ020EG                                                                  | 2 KB  | 512 B | 64 B | 25       | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

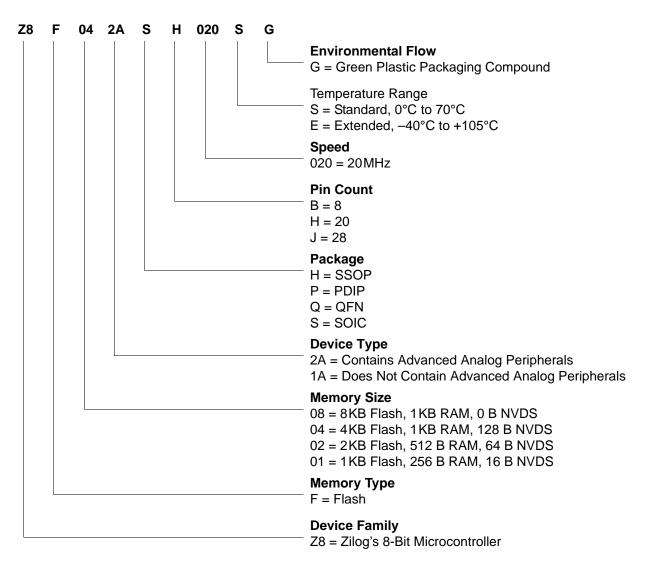

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.