Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041aph020eg |

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (UM0128), which is available for download on www.zilog.com.

# 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

# Low-Power Operational Amplifier

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

Table 7. Register File Address Map (Continued)

| Address (Hex)    | Register Description    | Mnemonic | Reset (Hex) | Page       |  |

|------------------|-------------------------|----------|-------------|------------|--|

| F85              | Reserved                | _        | XX          |            |  |

| Oscillator Contr | ol                      |          |             |            |  |

| F86              | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |  |

| F87–F8F          | Reserved                | _        | XX          |            |  |

| Comparator 0     |                         |          |             |            |  |

| F90              | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |  |

| F91–FBF          | Reserved                | _        | XX          |            |  |

| Interrupt Contro | oller                   |          |             |            |  |

| FC0              | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |  |

| FC1              | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |  |

| FC2              | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |  |

| FC3              | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |  |

| FC4              | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |  |

| FC5              | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |  |

| FC6              | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |  |

| FC7              | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |  |

| FC8              | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |  |

| FC9-FCC          | Reserved                | _        | XX          |            |  |

| FCD              | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |  |

| FCE              | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |  |

| FCF              | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |  |

| GPIO Port A      |                         |          |             |            |  |

| FD0              | Port A Address          | PAADDR   | 00          | <u>44</u>  |  |

| FD1              | Port A Control          | PACTL    | 00          | <u>46</u>  |  |

| FD2              | Port A Input Data       | PAIN     | XX          | <u>46</u>  |  |

| FD3              | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |  |

| GPIO Port B      |                         |          |             |            |  |

| FD4              | Port B Address          | PBADDR   | 00          | <u>44</u>  |  |

| FD5              | Port B Control          | PBCTL    | 00          | <u>46</u>  |  |

| FD6              | Port B Input Data       | PBIN     | XX          | <u>46</u>  |  |

| FD7              | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |  |

| GPIO Port C      |                         |          |             |            |  |

| FD8              | Port C Address          | PCADDR   | 00          | <u>44</u>  |  |

| Notos            |                         |          |             |            |  |

#### Notes:

- 1. XX = Undefined.

- 2. Refer to the eZ8 CPU Core User Manual (UM0128).

#### **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

Table 48. Shared Interrupt Select Register (IRQSS)

| Bit     | 7     | 6     | 5   | 4   | 3    | 2     | 1   | 0   |

|---------|-------|-------|-----|-----|------|-------|-----|-----|

| Field   | PA7VS | PA6CS |     |     | Rese | erved |     |     |

| RESET   | 0     | 0     | 0   | 0   | 0    | 0     | 0   | 0   |

| R/W     | R/W   | R/W   | R/W | R/W | R/W  | R/W   | R/W | R/W |

| Address |       |       |     | FC  | EH   |       |     |     |

| Bit          | Description                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VS | PA7/LVD Selection 0 = PA7 is used for the interrupt for PA7VS interrupt request. 1 = The LVD is used for the interrupt for PA7VS interrupt request.               |

| [6]<br>PA6CS | PA6/Comparator Selection 0 = PA6 is used for the interrupt for PA6CS interrupt request. 1 = The Comparator is used for the interrupt for PA6CS interrupt request. |

| [5:0]        | Reserved These bits are reserved and must be programmed to 000000.                                                                                                |

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{\text{(Capture Value - Start Value)} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode by writing the TMODE bits in the TxCTL1 Register and the TMODEHI bit in TxCTL0 Register

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults and other system-level problems which may place the Z8 Encore! XP F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# **Operation**

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =

$$\frac{\text{WDT Reload Value}}{10}$$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

Table 58. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value _ | Approximate Time-Out Delay (with 10kHz typical WDT oscillator frequency) |                        |  |

|------------------|--------------------|--------------------------------------------------------------------------|------------------------|--|

| (Hex)            | (Decimal)          | Typical                                                                  | Description            |  |

| 000004           | 4                  | 400 μs                                                                   | Minimum time-out delay |  |

| FFFFF            | 16,777,215         | 28 minutes                                                               | Maximum time-out delay |  |

#### Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the Z8 Encore! XP F082A Series devices are operating in DEBUG Mode (using the on-chip debugger), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

#### **Watchdog Timer Time-Out Response**

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. For information about programming the WDT\_RES Flash option bit, see the <u>Flash Option Bits</u> chapter on page 159.

#### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Reset Status (RSTSTAT) Register; see the Reset Status Register on page 29. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its reload value.

The Reset Status (RSTSTAT) Register must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts from immediately occurring.

#### **WDT Interrupt in STOP Mode**

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! XP F082A Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see the Reset, Stop Mode Recovery and Low Voltage Detection chapter on page 22.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

| #3 | #3 | #3 | #3 |

|----|----|----|----|

4. Round the result and discard the least significant two bytes (equivalent to dividing by  $2^{16}$ ).

| #3     | #3 #3  |      | #3   |

|--------|--------|------|------|

| _      |        |      |      |

| 0.00   | 0.00   | 0.00 | 0.00 |

| 0x00   | 0x00   | 0x80 | 0x00 |

| =      |        |      |      |

| #4 MSB | #4 LSB |      |      |

5. Determine the sign of the gain correction factor using the sign bits from Step 2. If the offset-corrected ADC value *and* the gain correction word both have the same sign, then the factor is positive and remains unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

| #5 MSB | #5 LSB |

|--------|--------|

|--------|--------|

6. Add the gain correction factor to the original offset corrected value.

| #5 MSB | #5 LSB |

|--------|--------|

| +      |        |

|        |        |

| #1 MSB | #1 LSB |

|        |        |

| =      |        |

| #6 MSB | #6 LSB |

| 1      |        |

7. Shift the result to the right, using the sign bit determined in <u>Step 1</u>, to allow for the detection of computational overflow.

| $S \rightarrow $ #6 MSB #6 LSB |  |

|--------------------------------|--|

|--------------------------------|--|

## **ADC Control Register 0**

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 73. ADC Control Register 0 (ADCCTL0)

| Bit     | 7   | 6       | 5      | 4    | 3   | 2    | 1      | 0   |

|---------|-----|---------|--------|------|-----|------|--------|-----|

| Field   | CEN | REFSELL | REFOUT | CONT |     | ANAI | N[3:0] |     |

| RESET   | 0   | 0       | 0      | 0    | 0   | 0    | 0      | 0   |

| R/W     | R/W | R/W     | R/W    | R/W  | R/W | R/W  | R/W    | R/W |

| Address |     |         |        | F7   | 0H  |      |        |     |

| Bit                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>CEN          | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                                                                                                       |

| [6]<br>REFSELL      | Voltage Reference Level Select Low Bit In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.  00 = Internal Reference Disabled, reference comes from external pin.  01 = Internal Reference set to 1.0 V.  10 = Internal Reference set to 2.0 V (default).  11 = Reserved. |

| [5]<br>REFOUT       | Internal Reference Output Enable  0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions.  1 = The internal ADC reference is buffered and driven out to the V <sub>REF</sub> pin.  Caution: When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.                                                                                                                                                           |

| [4]<br>CONT         | <ul> <li>Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long).</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long).</li> </ul>                                                                              |

| [3:0]<br>ANAIN[3:0] | Analog Input Select These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP F082A Series. For information about port pins available with each package style, see the Pin Description chapter on page 8. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.                                                           |

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$$

Caution: Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

# Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

Table 80. Flash Control Register (FCTL)

| Bit     | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|------|---|---|---|---|---|---|

| Field   |   | FCMD |   |   |   |   |   |   |

| RESET   | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W     | W | W    | W | W | W | W | W | W |

| Address |   | FF8H |   |   |   |   |   |   |

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| [7:0] | Flash Command                                                                        |

| FCMD  | 73H = First unlock command.                                                          |

|       | 8CH = Second unlock command.                                                         |

|       | 95H = Page Erase command (must be third command in sequence to initiate Page Erase). |

|       | 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase). |

|       | 5EH = Enable Flash Sector Protect Register Access                                    |

# Flash Status Register

The Flash Status (FSTAT) Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

Table 81. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|-------|---|---|---|---|---|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |

| RESET   | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R    | R     | R     | R | R | R | R | R |

| Address | FF8H |       |       |   |   |   |   |   |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                     |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [7:6]          | These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                                                           |  |

| [5:0]<br>FSTAT | Flash Controller Status  000000 = Flash Controller locked.  000001 = First unlock command received (73H written).  000010 = Second unlock command received (8CH written).  000011 = Flash Controller unlocked.  000100 = Sector protect register selected.  001xxx = Program operation in progress.  010xxx = Page erase operation in progress. |  |

#### **Temperature Sensor Calibration Data**

Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit                                             | 7                            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | TSCALH                       |     |     |     |     |     |     |     |

| RESET                                           | U                            | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 003A |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                              |     |     |     |     |     |     |     |

Bit Description

[7:0] Temperature Sensor Calibration High Byte

TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibration value. For more details, see Temperature Sensor Operation on page 139.

Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit                                             | 7                            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | TSCALL                       |     |     |     |     |     |     |     |

| RESET                                           | U                            | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 003B |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                              |     |     |     |     |     |     |     |

| Bit    | Description                                                                                     |

|--------|-------------------------------------------------------------------------------------------------|

| [7:0]  | Temperature Sensor Calibration Low Byte                                                         |

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-       |

|        | tion value. For usage details, see the <u>Temperature Sensor Operation</u> section on page 144. |

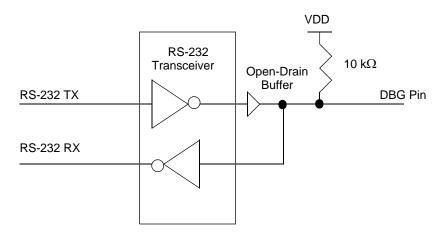

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

#### **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

Note: Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the OCD Auto-Baud Detector/Generator section on page 183).

Table 109. Debug Command Enable/Disable (Continued)

| Debug Command           | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                     |

|-------------------------|-----------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter   | 06H             | _                                     | Disabled.                                                                                                                                                        |

| Read Program Counter    | 07H             | _                                     | Disabled.                                                                                                                                                        |

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control registers are allowed. Additionally, only the Mass Erase command is allowed to be written to the Flash Control Register. |

| Read Register           | 09H             | _                                     | Disabled.                                                                                                                                                        |

| Write Program Memory    | 0AH             | _                                     | Disabled.                                                                                                                                                        |

| Read Program Memory     | 0BH             | _                                     | Disabled.                                                                                                                                                        |

| Write Data Memory       | 0CH             | _                                     | Yes.                                                                                                                                                             |

| Read Data Memory        | 0DH             | _                                     | _                                                                                                                                                                |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                |

| Reserved                | 0FH             | _                                     | _                                                                                                                                                                |

| Step Instruction        | 10H             | _                                     | Disabled.                                                                                                                                                        |

| Stuff Instruction       | 11H             | _                                     | Disabled.                                                                                                                                                        |

| Execute Instruction     | 12H             | _                                     | Disabled.                                                                                                                                                        |

| Reserved                | 13H–FFH         | _                                     | _                                                                                                                                                                |

In the list of OCD commands that follows, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

Read Runtime Counter (03H). The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory,

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 120 through 127 list the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

**Table 120. Arithmetic Instructions**

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 123. CPU Control Instructions (Continued)**

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| RCF      | _        | Reset Carry Flag       |

| SCF      | _        | Set Carry Flag         |

| SRP      | src      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

**Table 124. Load Instructions**

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

**Table 125. Logical Instructions**

| lst, src | Logical AND                                    |

|----------|------------------------------------------------|

| lst, src | Logical AND using Extended Addressing          |

| lst      | Complement                                     |

| lst, src | Logical OR                                     |

| lst, src | Logical OR using Extended Addressing           |

| lst, src | Logical Exclusive OR                           |

| lst, src | Logical Exclusive OR using Extended Addressing |

| k        | st, src<br>st<br>st, src<br>st, src<br>st, src |

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly     | Symbolic Operation            | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |   |

|--------------|-------------------------------|-----------------|-----|-------------|-------|---|---|---|---|----------------|-----------------|---|

| Mnemonic     |                               | dst             | src | (Hex)       |       | Z | S | ٧ | D | Н              | S               | S |

| ORX dst, src | dst ← dst OR src              | ER              | ER  | 48          | _     | * | * | 0 | _ | -              | 4               | 3 |

|              |                               | ER              | IM  | 49          | -     |   |   |   |   |                | 4               | 3 |

| POP dst      | dst ← @SP<br>SP ← SP + 1      | R               |     | 50          | -     | _ | - | - | _ | -              | 2               | 2 |

|              |                               | IR              |     | 51          | -     |   |   |   |   |                | 2               | 3 |

| POPX dst     | dst ← @SP<br>SP ← SP + 1      | ER              |     | D8          | -     | - | _ | - | - | -              | 3               | 2 |

| PUSH src     | SP ← SP − 1<br>@SP ← src      | R               |     | 70          | -     | - | _ | - | - | -              | 2               | 2 |

|              |                               | IR              |     | 71          | =     |   |   |   |   |                | 2               | 3 |

|              | -                             | IM              |     | IF70        | -     |   |   |   |   |                | 3               | 2 |

| PUSHX src    | SP ← SP − 1<br>@SP ← src      | ER              |     | C8          | -     | - | - | - | - | _              | 3               | 2 |

| RCF          | C ← 0                         |                 |     | CF          | 0     | _ | _ | _ | _ | _              | 1               | 2 |

| RET          | PC ← @SP<br>SP ← SP + 2       |                 |     | AF          | -     | - | _ | _ | - | _              | 1               | 4 |

| RL dst       | C D7D6D5D4D3D2D1D0            | R               |     | 90          | *     | * | * | * | _ | _              | 2               | 2 |

|              |                               | IR              |     | 91          | =     |   |   |   |   |                | 2               | 3 |

| RLC dst      | C D7 D6 D5 D4 D3 D2 D1 D0 dst | R               |     | 10          | *     | * | * | * | _ | _              | 2               | 2 |

|              |                               | IR              |     | 11          | -     |   |   |   |   |                | 2               | 3 |

| RR dst       |                               | R               |     | E0          | *     | * | * | * | _ | _              | 2               | 2 |

|              | D7 D6 D5 D4 D3 D2 D1 D0 dst   | IR              |     | E1          | -     |   |   |   |   |                | 2               | 3 |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing

$V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$   $T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ (unless otherwise stated)

|                          |                                                           | (************************************** |                     |            |                                |                                                                                     |  |  |  |

|--------------------------|-----------------------------------------------------------|-----------------------------------------|---------------------|------------|--------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Symbol                   | Parameter                                                 | Minimum                                 | num Typical Maximur |            | Units                          | Conditions                                                                          |  |  |  |

|                          | Resolution                                                | 10                                      |                     | _          | bits                           |                                                                                     |  |  |  |

|                          | Differential Nonlinearity (DNL)                           | -1.0                                    | -                   | 1.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |  |  |  |

|                          | Integral Nonlinearity (INL)                               | -3.0                                    | -                   | 3.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |  |  |  |

|                          | Offset Error with Calibration                             |                                         | <u>+</u> 1          |            | LSB <sup>3</sup>               |                                                                                     |  |  |  |

|                          | Absolute Accuracy with Calibration                        |                                         | <u>+</u> 3          |            | LSB <sup>3</sup>               |                                                                                     |  |  |  |

| V <sub>REF</sub>         | Internal Reference Voltage                                | 1.0<br>2.0                              | 1.1<br>2.2          | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                              |  |  |  |

| V <sub>REF</sub>         | Internal Reference Variation with Temperature             |                                         | <u>+</u> 1.0        |            | %                              | Temperature variation with V <sub>DD</sub> = 3.0                                    |  |  |  |

| V <sub>REF</sub>         | Internal Reference Voltage Variation with V <sub>DD</sub> |                                         | <u>+</u> 0.5        |            | %                              | Supply voltage variation with T <sub>A</sub> = 30°C                                 |  |  |  |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output Impedance                         |                                         | 850                 |            | W                              | When the internal reference is buffered and driven out to the VREF pin (REFOUT = 1) |  |  |  |

|                          | Single-Shot Conversion<br>Time                            | -                                       | 5129                | -          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                             |  |  |  |

|                          |                                                           |                                         | 10258               |            |                                | Temperature sensor measurement                                                      |  |  |  |

#### Notes:

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD} = 3.3 \,\text{V}$  and  $T_A = +30 \,^{\circ}\text{C}$ , so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

# **Packaging**

Zilog's Product Line of MCUs includes the Z8F011A, Z8F012A, Z8F021A, Z8F022A, Z8F041A, Z8F042A, Z8F042A devices, which are available in the following packages:

- 8-pin Plastic Dual-Inline Package (PDIP)

- 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S<sup>1</sup>

- 8-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 20-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

<sup>1.</sup> The footprint of the QFN)/MLF-S package is identical to that of the 8-pin SOIC package, but with a lower profile.