Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041apj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers64                 |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

#### vi

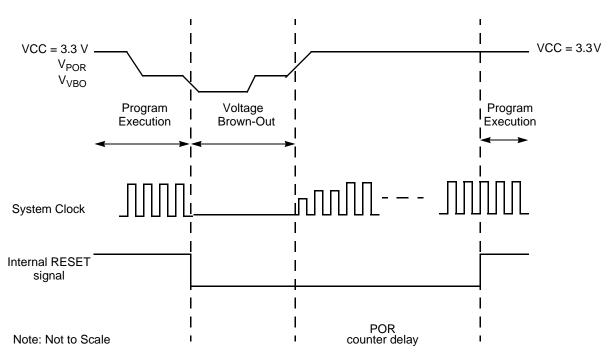

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F082A Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see <u>Table 20 on page 46</u>), the <u>RESET</u> pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) Register is set.

## Stop Mode Recovery

STOP Mode is entered by execution of a STOP instruction by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 32 for detailed STOP Mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see <u>Table 135</u> on page 233)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vec-

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

### Table 12. Reset and Stop Mode Recovery Bit Descriptions

|          | Program        |                                                                                                                        |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------|

|          | Memory         |                                                                                                                        |

| Priority | Vector Address |                                                                                                                        |

| Highest  | 0002H          | Reset (not an interrupt)                                                                                               |

|          | 0004H          | Watchdog Timer (see Watchdog Timer)                                                                                    |

|          | 003AH          | Primary Oscillator Fail Trap (not an interrupt)                                                                        |

|          | 003CH          | Watchdog Oscillator Fail Trap (not an interrupt)                                                                       |

|          | 0006H          | Illegal Instruction Trap (not an interrupt)                                                                            |

| _        | 0008H          | Reserved                                                                                                               |

|          | 000AH          | Timer 1                                                                                                                |

|          | 000CH          | Timer 0                                                                                                                |

|          | 000EH          | UART 0 receiver                                                                                                        |

|          | 0010H          | UART 0 transmitter                                                                                                     |

|          | 0012H          | Reserved                                                                                                               |

|          | 0014H          | Reserved                                                                                                               |

|          | 0016H          | ADC                                                                                                                    |

|          | 0018H          | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery and Low Voltage Detection) |

| -        | 001AH          | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                             |

|          | 001CH          | Port A Pin 5, selectable rising or falling input edge                                                                  |

|          | 001EH          | Port A Pin 4, selectable rising or falling input edge                                                                  |

|          | 0020H          | Port A Pin 3, selectable rising or falling input edge                                                                  |

|          | 0022H          | Port A Pin 2, selectable rising or falling input edge                                                                  |

|          | 0024H          | Port A Pin 1, selectable rising or falling input edge                                                                  |

| -        | 0026H          | Port A Pin 0, selectable rising or falling input edge                                                                  |

|          | 0028H          | Reserved                                                                                                               |

|          | 002AH          | Reserved                                                                                                               |

|          | 002CH          | Reserved                                                                                                               |

|          | 002EH          | Reserved                                                                                                               |

|          | 0030H          | Port C Pin 3, both input edges                                                                                         |

|          | 0032H          | Port C Pin 2, both input edges                                                                                         |

|          | 0034H          | Port C Pin 1, both input edges                                                                                         |

| Lowest   | 0036H          | Port C Pin 0, both input edges                                                                                         |

|          | 0038H          | Reserved                                                                                                               |

|          |                |                                                                                                                        |

#### Table 34. Trap and Interrupt Vectors in Order of Priority

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit     | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|------|------|-------|-----|------|------|------|------|

| Field   |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H |      |       |     |      |      |      |      |

| Table 37. | Interrupt | Request 2 | Register | (IRQ2) |

|-----------|-----------|-----------|----------|--------|

|-----------|-----------|-----------|----------|--------|

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [7:4]   | Reserved                                                             |  |

|         | These bits are reserved and must be programmed to 0000.              |  |

| [3:0]   | Port C Pin <i>x</i> Interrupt Request                                |  |

| PCxI    | 0 = No interrupt request is pending for GPIO Port C pin $x$ .        |  |

|         | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: x | c indicates the specific GPIO Port C pin number (0–3).               |  |

## **IRQ0 Enable High and Low Bit Registers**

Table 38 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register.

| IRQ0ENH[x]                           | IRQ0ENL[x] | Priority | Description |  |

|--------------------------------------|------------|----------|-------------|--|

| 0                                    | 0          | Disabled | Disabled    |  |

| 0                                    | 1          | Level 1  | Low         |  |

| 1                                    | 0          | Level 2  | Medium      |  |

| 1                                    | 1          | Level 3  | High        |  |

| Note: x indicates register bits 0–7. |            |          |             |  |

Table 38. IRQ0 Enable and Priority Encoding

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:3]<br>PRES  | Prescale value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the Timer is disabled. This reset ensures proper clock division each time the<br>Timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                                                                                                                                                                                                |

| [2:0]<br>TMODE | Timer Mode<br>This field, along with the TMODEHI bit in the TxCTL0 Register, determines the operating mode<br>of the timer. TMODEHI is the most significant bit of the Timer mode selection value. The entire<br>operating mode bits are expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the<br>TxCTL0 Register while TMODE[2:0] is the lower 3 bits of the TxCTL1 Register.<br>0000 = ONE-SHOT Mode.<br>0001 = CONTINUOUS Mode.<br>0010 = COUNTER Mode.<br>0011 = PWM SINGLE OUTPUT Mode.<br>0100 = CAPTURE Mode.<br>0101 = COMPARE Mode.<br>0111 = CAPTURE/COMPARE Mode.<br>1000 = PWM DUAL OUTPUT Mode.<br>1001 = CAPTURE RESTART Mode.<br>1010 = COMPARATOR COUNTER Mode. |

## Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 52 and 53, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from TxL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value. 89

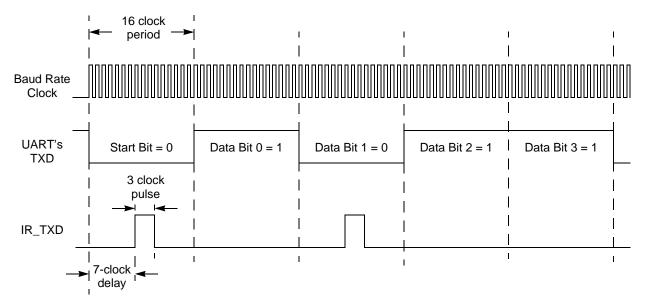

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

## **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

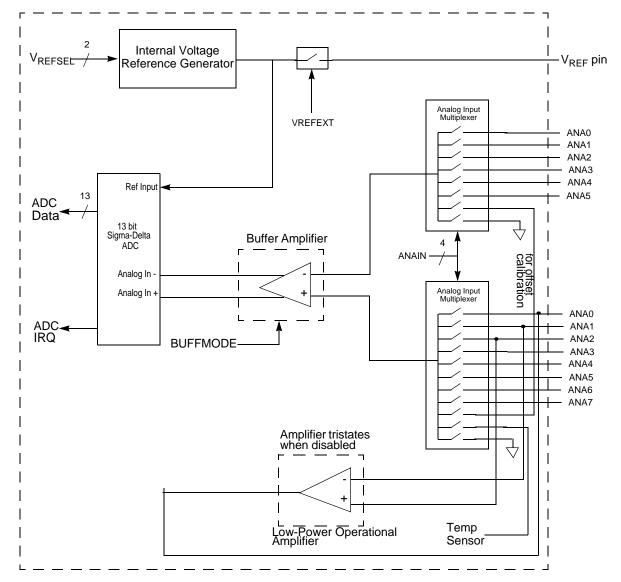

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

#### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

#### **Compensation Steps:**

1. Correct for Offset:

| ADC MSB    | ADC LSB    |

|------------|------------|

| _          |            |

| Offset MSB | Offset LSB |

| =          |            |

| #1 MSB     | #1 LSB     |

|            |            |

2. Compute the absolute value of the offset-corrected ADC value *if negative*; the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB | #2 LSB |

|--------|--------|

|--------|--------|

Also compute the absolute value of the gain correction word, if negative.

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by the Gain Correction Word. If operating in DIFFERENTIAL Mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Use the appropriate Gain Correction Word based on the sign computed by byte #2.

| #2 MSB | #2 LSB |

|--------|--------|

|        |        |

| AGain MSB | AGain LSB |

|-----------|-----------|

| -         |           |

=

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

#### 150

#### Table 79. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Mem-<br>ory. In user code programming, Page Erase and Mass Erase are all<br>disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                   |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the target page. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. See Figure 22 on page 148 for details.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F082A Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 78</u> on page 146.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Regis-

| Info Page | Memory  |                         |                          |                |

|-----------|---------|-------------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage      | ADC Mode                 | Reference Type |

| 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 72        | FE72    | Offset                  | Differential Unbuffered  | Internal 1.0 V |

| 14        | FE14    | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 15        | FE15    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 32        | FE32    | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 33        | FE33    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 75        | FE75    | Offset                  | Differential Unbuffered  | External 2.0 V |

| 16        | FE16    | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 17        | FE17    | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 34        | FE34    | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 35        | FE35    | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 78        | FE78    | Offset                  | Differential 1x Buffered | Internal 2.0 V |

| 18        | FE18    | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 19        | FE19    | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 36        | FE36    | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 37        | FE37    | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 7B        | FE7B    | Offset                  | Differential 1x Buffered | External 2.0 V |

| 1A        | FE1A    | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 1B        | FE1B    | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

| 38        | FE38    | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 39        | FE39    | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

### Table 97. ADC Calibration Data Location (Continued)

## **Temperature Sensor Calibration Data**

#### Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit                                             | 7                            | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|------------------------------|-----------------|-----|-----|-----|-----|-----|-----|

| Field                                           | TSCALH                       |                 |     |     |     |     |     |     |

| RESET                                           | U                            | U U U U U U U U |     |     |     |     |     |     |

| R/W                                             | R/W                          | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 003A |                 |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                              |                 |     |     |     |     |     |     |

#### Bit Description [7:0] **Temperature Sensor Calibration High Byte** TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-

tion value. For more details, see Temperature Sensor Operation on page 139.

#### Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit                                             | 7                            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | TSCALL                       |     |     |     |     |     |     |     |

| RESET                                           | U                            | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 003B |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                              |     |     |     |     |     |     |     |

#### Bit Description

| [7:0]  | Temperature Sensor Calibration Low Byte                                                   |

|--------|-------------------------------------------------------------------------------------------|

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra- |

|        | tion value. For usage details, see the Temperature Sensor Operation section on page 144.  |

## 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field     | WDTCALL                                         |     |     |     |     |     |     |     |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 007FH                   |     |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

## **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit                                             | 7                                 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | S_NUM                             |     |     |     |     |     |     |     |

| RESET                                           | U                                 | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                               | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 001C-001F |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                   |     |     |     |     |     |     |     |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

#### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

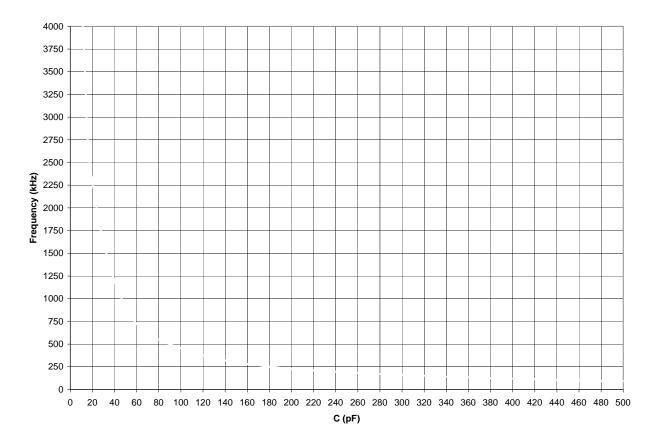

Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45k\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

202

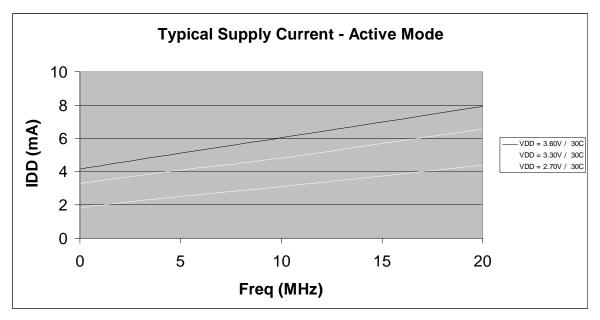

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode  $I_{\text{DD}}$  Versus System Clock Frequency

## **UART** Timing

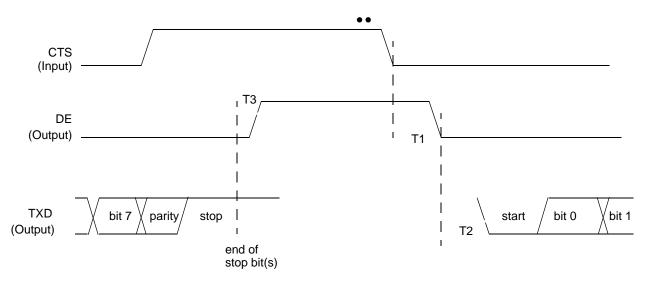

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

| Figure 37. | UART | Timing | With C | ٢S |

|------------|------|--------|--------|----|

|------------|------|--------|--------|----|

|                |                                                    | Delay (ns)                 |                                            |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |

| UART           |                                                    |                            |                                            |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | - 5                                        |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |

| Table 146. | IIART | Timina | With   | <b>CTS</b> |

|------------|-------|--------|--------|------------|

| Table 140. |       | runng  | VVILII | 613        |

CONTINUOUS mode 72, 87 COUNTER mode 73, 74 **COUNTER** modes 87 GATED mode 82, 88 ONE-SHOT mode 71, 87 operating mode 71 PWM mode 76, 77, 87, 88 reading the timer count values 84 reload high and low byte registers 91 timer control register definitions 85 timer output signal operation 84 timers 0-3 control registers 85, 86 high and low byte registers 89, 92 TM 209 TMX 209 transmit IrDA data 121 transmitting UART data-polled method 101 transmitting UART dat-interrupt-driven method 102 **TRAP 211**

## U

UART 6 architecture 99 baud rate generator 110 baud rates table 118 control register definitions 110 controller signals 10 interrupts 108 multiprocessor mode 105 receiving data using interrupt-driven method 104 receiving data using the polled method 103 transmitting data usin the interrupt-driven method 102 transmitting data using the polled method 101 x baud rate high and low registers 117 x control 0 and control 1 registers 110 x status 0 and status 1 registers 114, 115 UxBRH register 117 UxBRL register 117

UxCTL0 register 111, 117 UxCTL1 register 112 UxRXD register 116 UxSTAT0 register 114 UxSTAT1 register 115 UxTXD register 116

## V

vector 207 Voltage Brownout reset (VBR) 25

## W

Watchdog Timer approximate time-out delay 93 approximate time-out delays 140 CNTL 25 control register 96 electrical characteristics and timing 235, 238 interrupt in normal operation 94 interrupt in STOP mode 94 operation 140 refresh 94, 210 reload unlock sequence 95 reload upper, high and low registers 97 reset 26 reset in normal operation 95 reset in STOP mode 95 time-out response 94 WDTCTL register 30, 96, 141, 196 WDTH register 97 WDTL register 98 working register 206 working register pair 206 WTDU register 97

## Χ

X 207 XOR 210 XORX 210 263