Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041apj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers64                 |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

#### vi

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

### Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

### **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

**Note:** Asserting any power control bit disables the targeted block regardless of any enable bits contained in the target block's control registers.

>

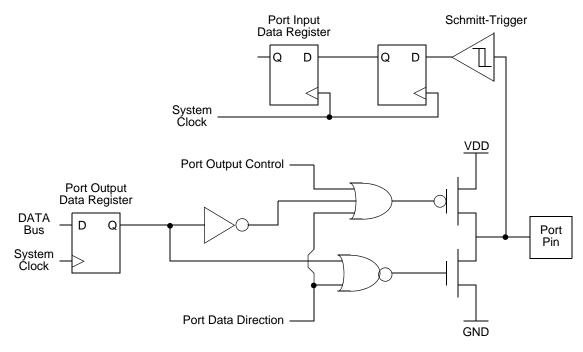

### Architecture

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

### **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either General-Purpose I/O or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. <u>Table 15</u> on page 40 lists the alternate functions possible with each port pin. For those pins with more one alternate function, the alternate function is defined through Alternate Function Sets subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer Reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This

#### **WDT Reset in Normal Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1. For more information about system reset, see the <u>Reset, Stop Mode</u> <u>Recovery and Low Voltage Detection</u> chapter on page 22.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following WDT time-out in STOP Mode.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. Observe the following steps to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU) with the appropriate time-out value.

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH) with the appropriate time-out value.

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL) with the appropriate time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

### Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page; see Tables 100 and 101 on page 173 for details. Loading these values

PRELIMINARY

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                           | 6                                                   | 5                        | 4    | 3     | 2      | 1      | 0            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------|--------------------------|------|-------|--------|--------|--------------|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MPMD[1]                     | MPEN                                                | MPMD[0]                  | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN         |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                           | 0                                                   | 0                        | 0    | 0     | 0      | 0      | 0            |  |  |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W                         | R/W                                                 | R/W                      | R/W  | R/W   | R/W    | R/W    | R/W          |  |  |

| Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | F43H                                                |                          |      |       |        |        |              |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                 |                                                     |                          |      |       |        |        |              |  |  |

| [6]<br>MPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |                                                     |                          |      |       |        |        |              |  |  |

| <ul> <li>1 = Enable MULTIPROCESSOR (9-bit) Mode.</li> <li>[4] Multiprocessor Bit Transmit</li> <li>MPBT This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit i used by the receiving device to determine if the data byte contains address or data inform tion.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).</li> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> </ul> |                             |                                                     |                          |      |       |        |        | ata informa- |  |  |

| [3]<br>DEPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Driver E</b><br>0 = DE s | <b>nable Pola</b><br>ignal is Acti<br>ignal is Acti | r <b>ity</b><br>ve High. |      |       | X      |        |              |  |  |

#### Table 64. UART Control 1 Register (U0CTL1)

| Bit     | 7     | 6      | 5   | 4    | 3     | 2   | 1   | 0   |

|---------|-------|--------|-----|------|-------|-----|-----|-----|

| Field   |       |        |     | COMP | _ADDR |     |     |     |

| RESET   | 0     | 0      | 0   | 0    | 0     | 0   | 0   | 0   |

| R/W     | R/W   | R/W    | R/W | R/W  | R/W   | R/W | R/W | R/W |

| Address |       |        |     | F4   | 5H    |     |     |     |

| Bit     | Deere | intion |     |      |       |     |     |     |

#### Table 69. UART Address Compare Register (U0ADDR)

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

### **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High (UxBRH) and Low Byte (UxBRL) registers, shown in Tables 70 and 71, combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |      | BRH |     |     |     |     |     |     |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F46H |     |     |     |     |     |     |     |  |

#### Bit Description

| [7:0] | UART Baud Rate High Byte |

|-------|--------------------------|

| BRH   |                          |

#### Table 71. UART Baud Rate Low Byte Register (U0BRL)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | BRL  |     |     |     |     |     |     |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F47H |     |     |     |     |     |     |  |  |

| Bit          | Description             |

|--------------|-------------------------|

| [7:0]<br>BRL | UART Baud Rate Low Byte |

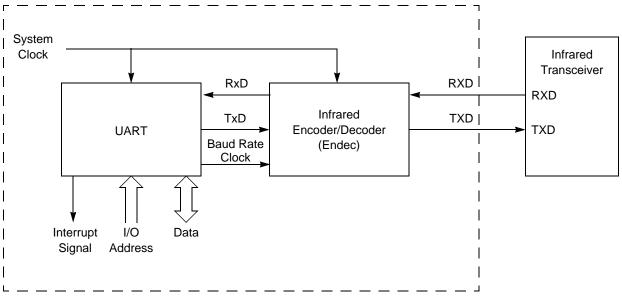

# Infrared Encoder/Decoder

Z8 Encore! XP F082A Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (endec). The infrared endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! XP MCU and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

### Architecture

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

### Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

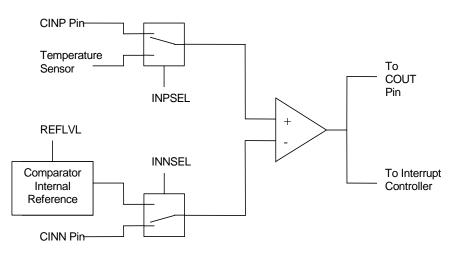

# Comparator

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

## Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251 \mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

| Bit              | 7        | 6 | 5 | 4 | 3    | 2  | 1   | 0   |

|------------------|----------|---|---|---|------|----|-----|-----|

| Field            | Reserved |   |   |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0        | 0 | 0 | 0 | 0    | 0  | 0   | 0   |

#### Table 106. Write Status Byte

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:4] | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                                  |

| [3]   | <b>Recopy Subroutine Executed</b>                                                                           |

| RCPY  | A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]   | <b>Power Failure Indicator</b>                                                                              |

| PF    | A power failure or system reset occurred during the most recent attempted write to the NVDS array.          |

| [1]   | Address Write Error                                                                                         |

| AWE   | An address byte failure occurred during the most recent attempted write to the NVDS array.                  |

| [0]   | Data Write Error                                                                                            |

| DWE   | A data byte failure occurred during the most recent attempted write to the NVDS array.                      |

DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

**Step Instruction (10H).** The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

**Stuff Instruction (11H).** The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 11H DBG ← opcode[7:0]

**Execute Instruction (12H).** The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not

205

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

### Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1.** If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2.** In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

| Assembly         | Symbolic Operation                                                                        | Address<br>Mode |     | _ Opcode(s) | Flags |     |   |   | Fetch | Instr.<br>Cycle |            |   |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----|-------------|-------|-----|---|---|-------|-----------------|------------|---|

| Mnemonic         |                                                                                           | dst             | src | (Hex)       | С     | Ζ   | S | V | D     | Н               | Cycle<br>s | S |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r               | r   | 52          | _     | *   | * | 0 | _     | _               | 2          | 3 |

|                  |                                                                                           | r               | Ir  | 53          |       |     |   |   |       |                 | 2          | 4 |

|                  |                                                                                           | R               | R   | 54          |       |     |   |   |       |                 | 3          | 3 |

|                  |                                                                                           | R               | IR  | 55          |       |     |   |   |       |                 | 3          | 4 |

|                  |                                                                                           | R               | IM  | 56          |       |     |   |   |       |                 | 3          | 3 |

|                  |                                                                                           | IR              | IM  | 57          |       |     |   |   |       |                 | 3          | 4 |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER              | ER  | 58          | -     | _ * | * | 0 | -     | -               | 4          | 3 |

|                  |                                                                                           | ER              | IM  | 59          |       |     |   |   |       |                 | 4          | 3 |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |                 |     | 2F          | -     | -   | _ | _ | _     | _               | 1          | 2 |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |     | E2          | -     | _   | _ | _ | _     | _               | 2          | 2 |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |     | E2          | -     | _   | - | - | _     | -               | 2          | 2 |

| BRK              | Debugger Break                                                                            |                 |     | 00          | -     | _   | - | - | _     | -               | 1          | 1 |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |     | E2          | -     | _   | - | - | _     | -               | 2          | 2 |

| BSWAP dst        | $dst[7:0] \leftarrow dst[0:7]$                                                            | R               |     | D5          | Х     | *   | * | 0 | _     | -               | 2          | 2 |

| BTJ p, bit, src, | if src[bit] = p<br>PC $\leftarrow$ PC + X                                                 |                 | r   | F6          | -     | _   | - | - | _     | -               | 3          | 3 |

| dst              |                                                                                           |                 | lr  | F7          |       |     |   |   |       |                 | 3          | 4 |

| BTJNZ bit, src,  | if src[bit] = 1<br>PC $\leftarrow$ PC + X                                                 |                 | r   | F6          |       | _   | - | - | -     | _               | 3          | 3 |

| dst              |                                                                                           |                 | lr  | F7          |       |     |   |   |       |                 | 3          | 4 |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r   | F6          | -     | _   |   | _ | -     | _               | 3          | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7          |       |     |   |   |       |                 | 3          | 4 |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

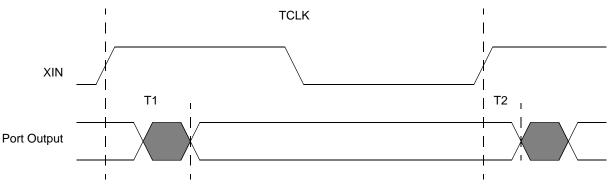

### General Purpose I/O Port Output Timing

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Dela    | y (ns)  |  |  |  |  |

|----------------|-------------------------------------------------|---------|---------|--|--|--|--|

| Parameter      | Abbreviation                                    | Minimum | Maximum |  |  |  |  |

| GPIO port pins |                                                 |         |         |  |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -       | 15      |  |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2       | _       |  |  |  |  |

#### Table 144. GPIO Port Output Timing

compare with carry - extended addressing 208 complement 210 complement carry flag 209 condition code 206 continuous conversion (ADC) 127 **CONTINUOUS** mode 87 control register definition, UART 110 Control Registers 15, 18 **COUNTER modes 87** CP 208 **CPC 208 CPCX 208** CPU and peripheral overview 4 CPU control instructions 209 **CPX 208** Customer Feedback Form 265

### D

DA 206, 208 data memory 17 DC characteristics 227 debugger, on-chip 180 **DEC 208** decimal adjust 208 decrement 208 decrement and jump non-zero 211 decrement word 208 **DECW 208** destination operand 207 device, port availability 36 DI 209 direct address 206 disable interrupts 209 DJNZ 211 dst 207

### Ε

EI 209 electrical characteristics 226 ADC 236 flash memory and timing 234 GPIO input data sample timing 240 Watchdog Timer 235, 238 enable interrupt 209 ER 206 extended addressing register 206 external pin reset 26 eZ8 CPU features 4 eZ8 CPU instruction classes 207 eZ8 CPU instruction notation 206 eZ8 CPU instruction set 204 eZ8 CPU instruction summary 212

### F

FCTL register 155, 161, 162 features, Z8 Encore! 1 first opcode map 224 FLAGS 207 flags register 207 flash controller 6 option bit address space 162 option bit configuration - reset 159 program memory address 0000H 162 program memory address 0001H 164 flash memory 146 arrangement 147 byte programming 151 code protection 149 configurations 146 control register definitions 153, 161 controller bypass 152 electrical characteristics and timing 234 flash control register 155, 161, 162 flash option bits 150 flash status register 155 flow chart 148 frequency high and low byte registers 157 mass erase 152 operation 147 operation timing 149 page erase 152 page select register 156, 157 FPS register 156, 157 FSTAT register 155

CONTINUOUS mode 72, 87 COUNTER mode 73, 74 **COUNTER** modes 87 GATED mode 82, 88 ONE-SHOT mode 71, 87 operating mode 71 PWM mode 76, 77, 87, 88 reading the timer count values 84 reload high and low byte registers 91 timer control register definitions 85 timer output signal operation 84 timers 0-3 control registers 85, 86 high and low byte registers 89, 92 TM 209 TMX 209 transmit IrDA data 121 transmitting UART data-polled method 101 transmitting UART dat-interrupt-driven method 102 **TRAP 211**

### U

UART 6 architecture 99 baud rate generator 110 baud rates table 118 control register definitions 110 controller signals 10 interrupts 108 multiprocessor mode 105 receiving data using interrupt-driven method 104 receiving data using the polled method 103 transmitting data usin the interrupt-driven method 102 transmitting data using the polled method 101 x baud rate high and low registers 117 x control 0 and control 1 registers 110 x status 0 and status 1 registers 114, 115 UxBRH register 117 UxBRL register 117

UxCTL0 register 111, 117 UxCTL1 register 112 UxRXD register 116 UxSTAT0 register 114 UxSTAT1 register 115 UxTXD register 116

### V

vector 207 Voltage Brownout reset (VBR) 25

### W

Watchdog Timer approximate time-out delay 93 approximate time-out delays 140 CNTL 25 control register 96 electrical characteristics and timing 235, 238 interrupt in normal operation 94 interrupt in STOP mode 94 operation 140 refresh 94, 210 reload unlock sequence 95 reload upper, high and low registers 97 reset 26 reset in normal operation 95 reset in STOP mode 95 time-out response 94 WDTCTL register 30, 96, 141, 196 WDTH register 97 WDTL register 98 working register 206 working register pair 206 WTDU register 97

### Χ

X 207 XOR 210 XORX 210 263