Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 4KB (4K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | 128 x 8                                                   |  |

| RAM Size                   | 1K x 8                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041asb020eg |  |

| Reset, Stop Mode Recovery and Low Voltage Detection | . 22 |

|-----------------------------------------------------|------|

| Reset Types                                         | . 22 |

| Reset Sources                                       | . 24 |

| Power-On Reset                                      | . 24 |

| Voltage Brown-Out Reset                             | . 25 |

| Watchdog Timer Reset                                | . 26 |

| External Reset Input                                | . 26 |

| External Reset Indicator                            | . 27 |

| On-Chip Debugger Initiated Reset                    | . 27 |

| Stop Mode Recovery                                  | . 27 |

| Stop Mode Recovery Using Watchdog Timer Time-Out    | . 28 |

| Stop Mode Recovery Using a GPIO Port Pin Transition | . 28 |

| Stop Mode Recovery Using the External RESET Pin     | . 29 |

| Low Voltage Detection                               | . 29 |

| Reset Register Definitions                          | . 29 |

| Low-Power Modes                                     | 32   |

| STOP Mode                                           |      |

| HALT Mode                                           | -    |

| Peripheral-Level Power Control                      |      |

| Power Control Register Definitions                  |      |

|                                                     |      |

| General-Purpose Input/Output                        |      |

| GPIO Port Availability By Device                    |      |

| Architecture                                        |      |

| GPIO Alternate Functions                            |      |

| Direct LED Drive                                    |      |

| Shared Reset Pin                                    |      |

| Shared Debug Pin                                    |      |

| Crystal Oscillator Override                         |      |

| 5V Tolerance                                        |      |

| External Clock Setup                                |      |

| GPIO Grand Braining Definition                      |      |

| GPIO Control Register Definitions                   |      |

| Port A–D Address Registers                          |      |

| Port A–D Control Registers                          |      |

| Port A–D Data Direction Subregisters                |      |

| Port A–D Alternate Function Subregisters            |      |

| Port A–C Input Data Registers                       |      |

| Port A–D Output Data Register                       |      |

| LED Drive Enable Register                           |      |

| LED Drive Level High Register                       | . 53 |

| Trim Bit Address 0000H                           | 165 |

|--------------------------------------------------|-----|

| Trim Bit Address 0001H                           | 165 |

| Trim Bit Address 0002H                           | 166 |

| Trim Bit Address 0003H                           | 166 |

| Trim Bit Address 0004H                           | 168 |

| Zilog Calibration Data                           | 168 |

| ADC Calibration Data                             | 169 |

| Temperature Sensor Calibration Data              | 171 |

| Watchdog Timer Calibration Data                  | 172 |

| Serialization Data                               | 173 |

| Randomized Lot Identifier                        | 174 |

| Nonvolatile Data Storage                         | 176 |

| Operation                                        |     |

| NVDS Code Interface                              |     |

| Byte Write                                       | 177 |

| Byte Read                                        | 178 |

| Power Failure Protection                         |     |

| Optimizing NVDS Memory Usage for Execution Speed | 178 |

| On-Chip Debugger                                 | 180 |

| Architecture                                     |     |

| Operation                                        |     |

| OCD Interface                                    |     |

| DEBUG Mode                                       |     |

| OCD Data Format                                  |     |

| OCD Auto-Baud Detector/Generator                 |     |

| OCD Serial Errors                                |     |

| OCD Unlock Sequence (8-Pin Devices Only)         |     |

| Breakpoints                                      |     |

| Runtime Counter                                  | 186 |

| On-Chip Debugger Commands                        | 186 |

| On-Chip Debugger Control Register Definitions    | 191 |

| OCD Control Register                             |     |

| OCD Status Register                              |     |

| Oscillator Control                               | 193 |

| Operation                                        |     |

| System Clock Selection                           |     |

| Clock Failure Detection and Recovery             |     |

| Oscillator Control Register Definitions          |     |

| Crystal Oscillator                               | 198 |

| VALVATOLA JASCALI (III UII                       | 190 |

| Table 89.  | Flash Options Bits at Program Memory Address 0001H                    | 164 |

|------------|-----------------------------------------------------------------------|-----|

| Table 90.  | Trim Options Bits at Address 0000H                                    | 165 |

| Table 91.  | Trim Option Bits at 0001H                                             | 165 |

| Table 92.  | Trim Option Bits at 0002H (TIPO)                                      | 166 |

| Table 93.  | Trim Option Bits at Address 0003H (TLVD)                              | 166 |

| Table 94.  | LVD Trim Values                                                       | 167 |

| Table 95.  | Trim Option Bits at 0004H                                             | 168 |

| Table 96.  | ADC Calibration Bits                                                  | 169 |

| Table 97.  | ADC Calibration Data Location                                         | 169 |

| Table 98.  | Temperature Sensor Calibration High Byte at 003A (TSCALH)             | 171 |

| Table 99.  | Temperature Sensor Calibration Low Byte at 003B (TSCALL)              | 171 |

| Table 100. | Watchdog Calibration High Byte at 007EH (WDTCALH)                     | 172 |

| Table 101. | Serial Number at 001C - 001F (S_NUM)                                  | 173 |

| Table 102. | Serialization Data Locations                                          | 173 |

| Table 103. | Watchdog Calibration Low Byte at 007FH (WDTCALL)                      | 173 |

| Table 104. | Lot Identification Number (RAND_LOT)                                  | 174 |

| Table 105. | Randomized Lot ID Locations                                           | 174 |

| Table 106. | Write Status Byte                                                     | 177 |

| Table 107. | NVDS Read Time                                                        | 179 |

| Table 108. | OCD Baud-Rate Limits                                                  | 184 |

| Table 109. | Debug Command Enable/Disable                                          | 186 |

| Table 110. | OCD Control Register (OCDCTL)                                         | 191 |

| Table 111. | OCD Status Register (OCDSTAT)                                         | 192 |

| Table 112. | Oscillator Configuration and Selection                                | 194 |

| Table 113. | Oscillator Control Register (OSCCTL)                                  | 196 |

| Table 114. | Recommended Crystal Oscillator Specifications                         | 200 |

| Table 115. | Transconductance Values for Low, Medium and High Gain Operating Modes | 200 |

| Table 116. | Assembly Language Syntax Example 1                                    | 205 |

| Table 117. | Assembly Language Syntax Example 2                                    | 205 |

| Table 118. | Notational Shorthand                                                  | 206 |

Table 8. Reset and Stop Mode Recovery Characteristics and Latency

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except WDT_CTL and OSC_CTL registers       | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4 µs to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deas-serted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

| Natae.              |     |                                    |                                           |                                         |

#### Notes:

- 1. Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <a href="Port-A-D Alternate Function Subregisters">Port-A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See the GPIO Mode Interrupt Controller chapter on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data. Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

**Table 17. GPIO Port Registers and Subregisters**

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register; selects subregisters.            |

| PxCTL                     | Port A–D Control Register; provides access to subregisters. |

| PxIN                      | Port A–D Input Data Register.                               |

| P <i>x</i> OUT            | Port A–D Output Data Register.                              |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction.                                             |

| PxAF                      | Alternate Function.                                         |

| PxOC                      | Output Control (Open-Drain).                                |

| PxHDE                     | High Drive Enable.                                          |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable.                           |

| P <i>x</i> PUE            | Pull-up Enable.                                             |

| PxAFS1                    | Alternate Function Set 1.                                   |

| PxAFS2                    | Alternate Function Set 2.                                   |

Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in Table 34 on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap and Illegal Instruction Trap always have highest (level 3) priority.

# Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

### **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

Table 48. Shared Interrupt Select Register (IRQSS)

| Bit     | 7     | 6     | 5   | 4   | 3    | 2     | 1   | 0   |

|---------|-------|-------|-----|-----|------|-------|-----|-----|

| Field   | PA7VS | PA6CS |     |     | Rese | erved |     |     |

| RESET   | 0     | 0     | 0   | 0   | 0    | 0     | 0   | 0   |

| R/W     | R/W   | R/W   | R/W | R/W | R/W  | R/W   | R/W | R/W |

| Address | FCEH  |       |     |     |      |       |     |     |

| Bit          | Description                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VS | PA7/LVD Selection 0 = PA7 is used for the interrupt for PA7VS interrupt request. 1 = The LVD is used for the interrupt for PA7VS interrupt request.               |

| [6]<br>PA6CS | PA6/Comparator Selection 0 = PA6 is used for the interrupt for PA6CS interrupt request. 1 = The Comparator is used for the interrupt for PA6CS interrupt request. |

| [5:0]        | Reserved These bits are reserved and must be programmed to 000000.                                                                                                |

## Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 56 and 57, control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 56. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | MH   |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F04H, | F0CH |     |     |     |

Table 57. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | /ML  |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F05H, | F0DH |     |     |     |

| Bit   | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| [7:0] | Pulse-Width Modulator High and Low Bytes                                                     |

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1) Register.                |

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

#### **Calibration and Compensation**

The Z8 Encore! XP F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL Mode operation.

#### **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 168.

#### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and nonlinearity; therefore Zilog recommends that this calibration be performed separately for each of the ADC input modes planned for use.

#### **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see <u>Table 139</u> on page 236). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION Mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in nonvolatile memory (see the <u>Nonvolatile Data Storage</u> chapter on page 176) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

#### Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$$\mathsf{ADC}_{comp} = (\mathsf{ADC}_{uncomp} - \mathsf{OFFCAL}) + ((\mathsf{ADC}_{uncomp} - \mathsf{OFFCAL}) \times \mathsf{GAINCAL}) / 2^{\mathsf{TT}} + (\mathsf{CAC}_{uncomp} - \mathsf{CAC}_{uncomp} - \mathsf{CAC}_{uncomp}) / 2^{\mathsf{TT}} + (\mathsf{CAC}_{uncomp} - \mathsf{CAC}_{uncomp} - \mathsf{CAC}_{uncomp}) / 2^{\mathsf{TT}} + (\mathsf{CAC}_{uncomp} - \mathsf{CAC}_{uncomp}) /$$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

| #3 | #3 | #3 | #3 |

|----|----|----|----|

4. Round the result and discard the least significant two bytes (equivalent to dividing by  $2^{16}$ ).

| #3     | #3 #3  |      | #3   |

|--------|--------|------|------|

| _      |        |      |      |

| 0.00   | 0.00   | 0.00 | 0.00 |

| 0x00   | 0x00   | 0x80 | 0x00 |

| =      |        |      |      |

| #4 MSB | #4 LSB |      |      |

5. Determine the sign of the gain correction factor using the sign bits from Step 2. If the offset-corrected ADC value *and* the gain correction word both have the same sign, then the factor is positive and remains unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

| #5 MSB | #5 LSB |

|--------|--------|

|--------|--------|

6. Add the gain correction factor to the original offset corrected value.

| #5 MSB | #5 LSB |

|--------|--------|

| +      |        |

|        |        |

| #1 MSB | #1 LSB |

|        |        |

| =      |        |

| #6 MSB | #6 LSB |

| 1      |        |

7. Shift the result to the right, using the sign bit determined in <u>Step 1</u>, to allow for the detection of computational overflow.

| $S \rightarrow $ #6 MSB #6 LSB |  |

|--------------------------------|--|

|--------------------------------|--|

# **ADC Control Register 0**

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

Table 73. ADC Control Register 0 (ADCCTL0)

| Bit     | 7    | 6       | 5      | 4    | 3          | 2   | 1   | 0   |

|---------|------|---------|--------|------|------------|-----|-----|-----|

| Field   | CEN  | REFSELL | REFOUT | CONT | ANAIN[3:0] |     |     |     |

| RESET   | 0    | 0       | 0      | 0    | 0          | 0   | 0   | 0   |

| R/W     | R/W  | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |

| Address | F70H |         |        |      |            |     |     |     |

| Bit                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>CEN          | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                                                                                                       |

| [6]<br>REFSELL      | Voltage Reference Level Select Low Bit In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; note that this reference is independent of the Comparator reference.  00 = Internal Reference Disabled, reference comes from external pin.  01 = Internal Reference set to 1.0 V.  10 = Internal Reference set to 2.0 V (default).  11 = Reserved. |

| [5]<br>REFOUT       | Internal Reference Output Enable  0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions.  1 = The internal ADC reference is buffered and driven out to the V <sub>REF</sub> pin.  Caution: When the ADC is used with an external reference ({REFSELH,REFSELL}=00), the REFOUT bit must be set to 0.                                                                                                                                                           |

| [4]<br>CONT         | <ul> <li>Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long).</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long).</li> </ul>                                                                              |

| [3:0]<br>ANAIN[3:0] | Analog Input Select These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP F082A Series. For information about port pins available with each package style, see the Pin Description chapter on page 8. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.                                                           |

Table 75. ADC Data High Byte Register (ADCD\_H)

| Bit       | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|--------------|---|---|---|---|---|---|---|

| Field     | ADCDH        |   |   |   |   |   |   |   |

| RESET     | Χ            | Х | Х | Х | Х | Х | Х | Х |

| R/W       | R            | R | R | R | R | R | R | R |

| Address   | F72H         |   |   |   |   |   |   |   |

| X = Undef | = Undefined. |   |   |   |   |   |   |   |

| Bit   | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| [7:0] | ADC Data High Byte                                                                                |

| ADCDH | This byte contains the upper eight bits of the ADC output. These bits are not valid during a sin- |

|       | gle-shot conversion. During a continuous conversion, the most recent conversion output is         |

|       | held in this register. These bits are undefined after a Reset.                                    |

## **ADC Data Low Byte Register**

The ADC Data Low Byte (ADCD\_L) Register contains the lower bits of the ADC output plus an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

Table 76. ADC Data Low Byte Register (ADCD\_L)

| Bit       | 7                  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|--------------------|---|---|---|---|---|---|---|

| Field     | ADCDL Reserved OVF |   |   |   |   |   |   |   |

| RESET     | Х                  | Х | Х | Х | Х | Х | Х | Х |

| R/W       | R                  | R | R | R | R | R | R | R |

| Address   | F73H               |   |   |   |   |   |   |   |

| X = Undef | efined.            |   |   |   |   |   |   |   |

| Bit            | Description                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]<br>ADCDL | ADC Data Low Bits  These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset. |

# Low Power Operational Amplifier

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the noninverting input.

# **Operation**

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared by turning it ON (for details, see the <u>Power Control Register 0</u> section on page 33). When making normal ADC measurements on ANA0 (i.e., measurements not involving the LPO output), the LPO bit must be turned OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Caution:** The LPO bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failing to perform this results in STOP Mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers. See the <u>Port A–D Alternate Function Subregisters</u> section on page 47 for details.

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

#### **Trim Bit Address 0002H**

Table 92. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                               | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|-------------------------------------------------|----------|---|---|---|---|---|---|--|

| Field     |                                                 | IPO_TRIM |   |   |   |   |   |   |  |

| RESET     |                                                 | U        |   |   |   |   |   |   |  |

| R/W       | R/W                                             |          |   |   |   |   |   |   |  |

| Address   | Information Page Memory 0022H                   |          |   |   |   |   |   |   |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |   |   |   |   |   |   |  |

### **Trim Bit Address 0003H**

**Note:** The LVD is available on 8-pin devices only.

#### Table 93. Trim Option Bits at Address 0003H (TLVD)

| Bit                                             | 7                             | 6        | 5   | 4        | 3   | 2   | 1   | 0   |  |  |  |  |

|-------------------------------------------------|-------------------------------|----------|-----|----------|-----|-----|-----|-----|--|--|--|--|

| Field                                           |                               | Reserved |     | LVD_TRIM |     |     |     |     |  |  |  |  |

| RESET                                           | U                             | U        | U   | U        | U   | U   |     |     |  |  |  |  |

| R/W                                             | R/W                           | R/W      | R/W | R/W      | R/W | R/W | R/W | R/W |  |  |  |  |

| Address                                         | Information Page Memory 0023H |          |     |          |     |     |     |     |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |     |          |     |     |     |     |  |  |  |  |

| Bit               | Description                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]             | Reserved These bits are reserved and must be programmed to 111.                                                                                                                                                                                               |

| [4:0]<br>LVD_TRIM | Low Voltage Detect Trimm  This trimming affects the low voltage detection threshold. Each LSB represents a 50mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation: |

|                   | $LVD_LVL = 3.6 V - LVD_TRIM \times 0.05 V$                                                                                                                                                                                                                    |

|                   | These values are tabulated in Table 94.                                                                                                                                                                                                                       |

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series device. When this option is enabled, several of the OCD commands are disabled. See Table 109.

<u>Table 110</u> on page 191 is a summary of the on-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 110 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

Table 109. Debug Command Enable/Disable

| Debug Command              | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | _                                            |

| Reserved                   | 01H             | _                                     | _                                            |

| Read OCD Status Register   | 02H             | Yes                                   | _                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                    |

| Read OCD Control Register  | 05H             | Yes                                   | _                                            |

# Oscillator Operation with an External RC Network

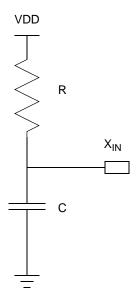

Figure 28 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45\,\mathrm{k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is  $40\,\mathrm{k}\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (R in  $\mathrm{k}\Omega$ ) and capacitor (C in pF) elements using the following equation:

Oscillator Frequency (kHz)

$$= \frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$$

Figure 29 displays the typical (3.3 V and 25°C) oscillator frequency as a function of the capacitor (C, in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator  $X_{IN}$  pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended.

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly      | Symbolic Operation                  | Address<br>Mode |     | _ Opcode(s) |   |   | Fla | ags | Fetch<br>Cycle | Instr.<br>Cycle |   |   |

|---------------|-------------------------------------|-----------------|-----|-------------|---|---|-----|-----|----------------|-----------------|---|---|

| Mnemonic      |                                     | dst             | src | (Hex)       | С | Z | S   | ٧   | D              | Н               | S | S |

| SUB dst, src  | dst ← dst – src                     | r               | r   | 22          | * | * | *   | *   | 1              | *               | 2 | 3 |

|               |                                     | r               | lr  | 23          | - |   |     |     |                |                 | 2 | 4 |

|               |                                     | R               | R   | 24          | - |   |     |     |                |                 | 3 | 3 |

|               |                                     | R               | IR  | 25          | - |   |     |     |                |                 | 3 | 4 |

|               |                                     | R               | IM  | 26          | - |   |     |     |                |                 | 3 | 3 |

|               |                                     | IR              | IM  | 27          | - |   |     |     |                |                 | 3 | 4 |

| SUBX dst, src | dst ← dst – src                     | ER              | ER  | 28          | * | * | *   | *   | 1              | *               | 4 | 3 |

|               |                                     | ER              | IM  | 29          | - |   |     |     |                |                 | 4 | 3 |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R               |     | F0          | Χ | * | *   | Χ   | -              | _               | 2 | 2 |

|               |                                     | IR              |     | F1          | - |   |     |     |                |                 | 2 | 3 |

| TCM dst, src  | (NOT dst) AND src                   | r               | r   | 62          | - | * | *   | 0   | -              | _               | 2 | 3 |

|               |                                     | r               | Ir  | 63          | • |   |     |     |                |                 | 2 | 4 |

|               |                                     | R               | R   | 64          | - |   |     |     |                |                 | 3 | 3 |

|               |                                     | R               | IR  | 65          | • |   |     |     |                |                 | 3 | 4 |

|               |                                     | R               | IM  | 66          | • |   |     |     |                |                 | 3 | 3 |

|               |                                     | IR              | IM  | 67          | • |   |     |     |                |                 | 3 | 4 |

| TCMX dst, src | (NOT dst) AND src                   | ER              | ER  | 68          | - | * | *   | 0   | -              | -               | 4 | 3 |

|               |                                     | ER              | IM  | 69          | - |   |     |     |                |                 | 4 | 3 |

| TM dst, src   | dst AND src                         | r               | r   | 72          | - | * | *   | 0   | -              | -               | 2 | 3 |

|               |                                     | r               | lr  | 73          | 5 |   |     |     |                |                 | 2 | 4 |

|               |                                     | R               | R   | 74          | 5 |   |     |     |                |                 | 3 | 3 |

|               |                                     | R               | IR  | 75          | 5 |   |     |     |                |                 | 3 | 4 |

|               |                                     | R               | IM  | 76          | 5 |   |     |     |                |                 | 3 | 3 |

|               |                                     | IR              | IM  | 77          | 5 |   |     |     |                |                 | 3 | 4 |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                                                                                                                              | Address<br>Mode |        | _ Opcode(s) |   |   | Fla | ags | Fetch<br>Cycle | Instr.<br>Cycle |   |   |

|---------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-------------|---|---|-----|-----|----------------|-----------------|---|---|

| Mnemonic      | Symbolic Operation                                                                                                           | dst             | src    | (Hex)       | С | Z | S   | ٧   | D              | Н               | S | S |

| TMX dst, src  | dst AND src                                                                                                                  | ER              | ER     | 78          | _ | * | *   | 0   | -              | -               | 4 | 3 |

|               |                                                                                                                              | ER              | IM     | 79          |   |   |     |     |                |                 | 4 | 3 |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>$@SP \leftarrow PC$<br>$SP \leftarrow SP - 1$<br>$@SP \leftarrow FLAGS$<br>$PC \leftarrow @Vector$ |                 | Vector | F2          | - | - | -   | -   | -              | -               | 2 | 6 |

| WDT           |                                                                                                                              |                 |        | 5F          | _ | _ | _   | _   | _              | _               | 1 | 2 |

| XOR dst, src  | dst ← dst XOR src                                                                                                            | r               | r      | B2          | _ | * | *   | 0   | _              | _               | 2 | 3 |

|               |                                                                                                                              | r               | lr     | В3          | • |   |     |     |                |                 | 2 | 4 |

|               |                                                                                                                              | R               | R      | B4          | • |   |     |     |                |                 | 3 | 3 |

|               |                                                                                                                              | R               | IR     | B5          | • |   |     |     |                |                 | 3 | 4 |

|               |                                                                                                                              | R               | IM     | В6          | • |   |     |     |                |                 | 3 | 3 |

|               |                                                                                                                              | IR              | IM     | В7          |   |   |     |     |                |                 | 3 | 4 |

| XORX dst, src | dst ← dst XOR src                                                                                                            | ER              | ER     | В8          | - | * | *   | 0   | _              | -               | 4 | 3 |

|               |                                                                                                                              | ER              | IM     | В9          | • |   |     |     |                |                 | 4 | 3 |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

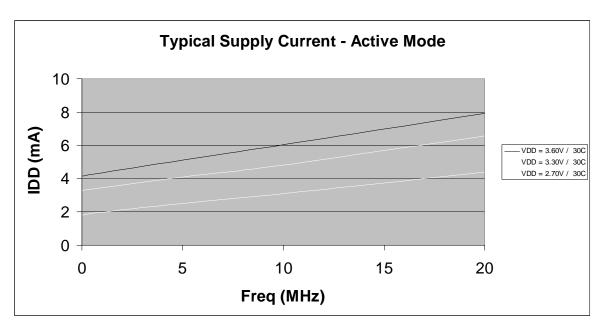

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode  $I_{DD}$  Versus System Clock Frequency