Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ahj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| Bit     | 7                                                                                     | 6                             | 5    | 4    | 3    | 2        | 1    | 0    |

|---------|---------------------------------------------------------------------------------------|-------------------------------|------|------|------|----------|------|------|

| Field   | POC7                                                                                  | POC6                          | POC5 | POC4 | POC3 | POC2     | POC1 | POC0 |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D) |      |      |      |          |      |      |

| R/W     | R/W                                                                                   | R/W                           | R/W  | R/W  | R/W  | R/W      | R/W  | R/W  |

| Address | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |                               |      |      |      | Register |      |      |

| D:4     | Decertation                                                                           |                               |      |      |      |          |      |      |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

## Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PHDE7     | PHDE6        | PHDE5       | PHDE4         | PHDE3        | PHDE2        | PHDE1        | PHDE0    |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | lf 04H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit        | Description                                                       |

|------------|-------------------------------------------------------------------|

| [7:0]      | Port High Drive Enabled                                           |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |

|            | 1 = The port pin is configured for high output current drive.     |

| Note: x in | dicates the specific GPIO port pin number (7–0).                  |

# **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit          | 7                                                                                                                                                                                                       | 6               | 5                               | 4   | 3    | 2     | 1   | 0   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|-----|------|-------|-----|-----|

| Field        | PA7VS                                                                                                                                                                                                   | PA6CS           |                                 |     | Rese | erved |     |     |

| RESET        | 0                                                                                                                                                                                                       | 0 0 0 0 0 0 0 0 |                                 |     |      |       |     |     |

| R/W          | R/W                                                                                                                                                                                                     | R/W             | R/W                             | R/W | R/W  | R/W   | R/W | R/W |

| Address      |                                                                                                                                                                                                         |                 |                                 | FC  | EH   |       |     |     |

| Bit          | Descriptio                                                                                                                                                                                              | Description     |                                 |     |      |       |     |     |

| [7]<br>PA7VS |                                                                                                                                                                                                         | used for the    | interrupt for<br>r the interrup |     |      |       |     |     |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator is used for the interrupt for PA6CS interrupt request.</li> </ul> |                 |                                 |     |      |       |     |     |

| [5:0]        | Reserved                                                                                                                                                                                                | Reserved        |                                 |     |      |       |     |     |

#### Table 48. Shared Interrupt Select Register (IRQSS)

These bits are reserved and must be programmed to 000000.

# Operation

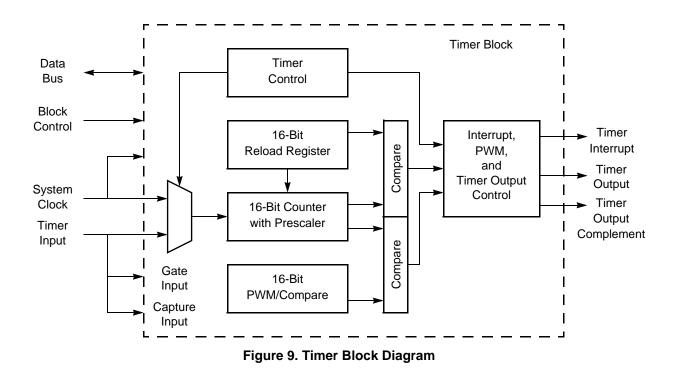

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If

71

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

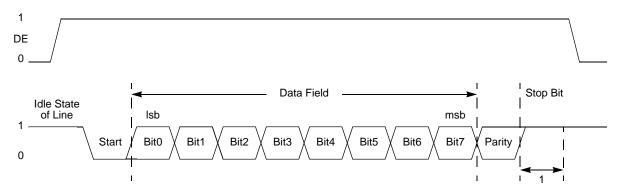

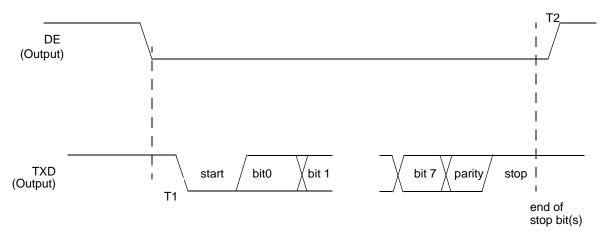

## **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, plus the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable-to-Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 72 provides information about the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

|                          | 10.0MHz Syste            | em Clock             |              | 5.                       | 5296MHz Sys              | tem Clock            |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

| 3 5                      | 705/5MH7 Sv              | stom Clock           | <u> </u>     | 1                        | 8/32MHz Sve              | tom Clock            |              |

#### Table 72. UART Baud Rates

3.579545 MHz System Clock

1.8432MHz System Clock

## **Receiving IrDA Data**

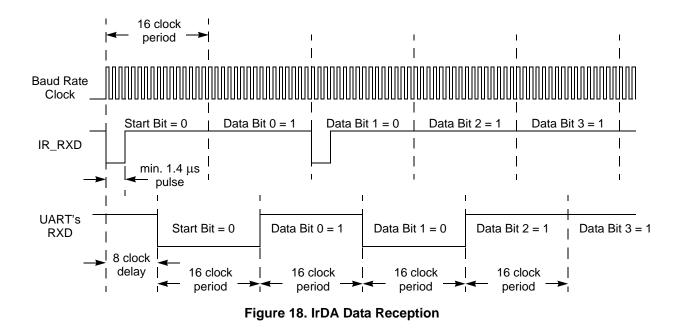

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_RXD signal is received through the RXD pin.

## **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

# **Calibration and Compensation**

The Z8 Encore! XP F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL Mode operation.

## **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 168.

### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and nonlinearity; therefore Zilog recommends that this calibration be performed separately for each of the ADC input modes planned for use.

## **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see <u>Table 139</u> on page 236). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION Mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in nonvolatile memory (see the <u>Nonvolatile Data Storage</u> chapter on page 176) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

## Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2$$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

# Low Power Operational Amplifier

The LPO is a general-purpose low power operational amplifier. Each of the three ports of the amplifier is accessible from the package pins. The LPO contains only one pin configuration: ANA0 is the output/feedback node, ANA1 is the inverting input and ANA2 is the noninverting input.

# Operation

To use the LPO, it must be enabled in the Power Control Register 0 (PWRCTL0). The default state of the LPO is OFF. To use the LPO, the LPO bit must be cleared by turning it ON (for details, see the <u>Power Control Register 0</u> section on page 33). When making normal ADC measurements on ANA0 (i.e., measurements not involving the LPO output), the LPO bit must be turned OFF. Turning the LPO bit ON interferes with normal ADC measurements.

**Caution:** The LPO bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failing to perform this results in STOP Mode currents higher than necessary.

As with other ADC measurements, any pins used for analog purposes must be configured as such in the GPIO registers. See the <u>Port A–D Alternate Function Subregisters</u> section on page 47 for details.

LPO output measurements are made on ANA0, as selected by the ANAIN[3:0] bits of ADC Control Register 0. It is also possible to make single-ended measurements on ANA1 and ANA2 while the amplifier is enabled, which is often useful for determining offset conditions. Differential measurements between ANA0 and ANA2 may be useful for noise cancellation purposes.

If the LPO output is routed to the ADC, then the BUFFMODE[2:0] bits of ADC Control/Status Register 1 must also be configured for unity-gain buffered operation. Sampling the LPO in an unbuffered mode is not recommended.

When either input is overdriven, the amplifier output saturates at the positive or negative supply voltage. No instability results.

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

## Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 90 through Table 95.

# Trim Bit Address 0000H

| Bit       | 7           | 6                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------|---------------------------------------|-----|-----|-----|-----|-----|-----|

| Field     |             | Reserved                              |     |     |     |     |     |     |

| RESET     | U           | U U U U U U U U                       |     |     |     |     |     | U   |

| R/W       | R/W         | R/W                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   |             | Information Page Memory 0020H         |     |     |     |     |     |     |

| Note: U = | Unchanged b | Inchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |

| Bit       | Descriptio  | n                                     |     |     |     |     |     |     |

| [7:0]     | Reserved    |                                       |     |     |     |     |     |     |

#### Table 90. Trim Options Bits at Address 0000H

These bits are reserved; altering this register may result in incorrect device operation.

# Trim Bit Address 0001H

#### Table 91. Trim Option Bits at 0001H

| Bit                                             | 7   | 6        | 5     | 4           | 3           | 2    | 1   | 0   |

|-------------------------------------------------|-----|----------|-------|-------------|-------------|------|-----|-----|

| Field                                           |     | Reserved |       |             |             |      |     |     |

| RESET                                           | U   | U        | U     | U           | U           | U    | U   | U   |

| R/W                                             | R/W | R/W      | R/W   | R/W         | R/W         | R/W  | R/W | R/W |

| Address                                         |     |          | Infor | mation Page | e Memory 00 | )21H |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |     |          |       |             |             |      |     |     |

# Bit Description [7:0] Reserved These bits are reserved; altering this register may result in incorrect device operation.

## **ADC Calibration Data**

#### Table 96. ADC Calibration Bits

| Bit        | 7             | 6           | 5             | 4          | 3          | 2       | 1   | 0   |

|------------|---------------|-------------|---------------|------------|------------|---------|-----|-----|

| Field      |               |             |               | ADC        | _CAL       |         |     |     |

| RESET      | U             | U           | U             | U          | U          | U       | U   | U   |

| R/W        | R/W           | R/W         | R/W           | R/W        | R/W        | R/W     | R/W | R/W |

| Address    |               |             | Informati     | on Page Me | mory 0060H | 1-007DH |     |     |

| Noto: II - | I Inchanged h | W Reset R/M | / - Road/Writ | ۰<br>۵     |            |         |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

# Bit Description

[7:0] Analog-to-Digital Converter Calibration Values

ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in the Software Compensation Procedure Using Factory Calibration Data section on page 129. The location of each calibration byte is provided in Table 97.

| Info Page | Memory  |                    |                          |                |

|-----------|---------|--------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage | ADC Mode                 | Reference Type |

| 60        | FE60    | Offset             | Single-Ended Unbuffered  | Internal 2.0 V |

| 08        | FE08    | Gain High Byte     | Single-Ended Unbuffered  | Internal 2.0 V |

| 09        | FE09    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 2.0 V |

| 63        | FE63    | Offset             | Single-Ended Unbuffered  | Internal 1.0 V |

| 0A        | FE0A    | Gain High Byte     | Single-Ended Unbuffered  | Internal 1.0 V |

| 0B        | FE0B    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 1.0 V |

| 66        | FE66    | Offset             | Single-Ended Unbuffered  | External 2.0 V |

| 0C        | FE0C    | Gain High Byte     | Single-Ended Unbuffered  | External 2.0 V |

| 0D        | FE0D    | Gain Low Byte      | Single-Ended Unbuffered  | External 2.0 V |

| 69        | FE69    | Offset             | Single-Ended 1x Buffered | Internal 2.0 V |

| 0E        | FE0E    | Gain High Byte     | Single-Ended 1x Buffered | Internal 2.0 V |

| 0F        | FE0F    | Gain Low Byte      | Single-Ended 1x Buffered | Internal 2.0 V |

| 6C        | FE6C    | Offset             | Single-Ended 1x Buffered | External 2.0 V |

| 10        | FE10    | Gain High Byte     | Single-Ended 1x Buffered | External 2.0 V |

| 11        | FE11    | Gain Low Byte      | Single-Ended 1x Buffered | External 2.0 V |

| 6F        | FE6F    | Offset             | Differential Unbuffered  | Internal 2.0 V |

#### Table 97. ADC Calibration Data Location

| Info Page<br>Address | Memory<br>Address | Usage                                         |

|----------------------|-------------------|-----------------------------------------------|

| 6A                   | FE6A              | Randomized Lot ID Byte 13.                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12.                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11.                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10.                    |

| 70                   | FE70              | Randomized Lot ID Byte 9.                     |

| 71                   | FE71              | Randomized Lot ID Byte 8.                     |

| 73                   | FE73              | Randomized Lot ID Byte 7.                     |

| 74                   | FE74              | Randomized Lot ID Byte 6.                     |

| 76                   | FE76              | Randomized Lot ID Byte 5.                     |

| 77                   | FE77              | Randomized Lot ID Byte 4.                     |

| 79                   | FE79              | Randomized Lot ID Byte 3.                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2.                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1.                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant). |

|                      |                   |                                               |

## Table 105. Randomized Lot ID Locations (Continued)

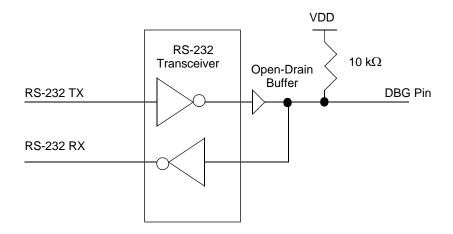

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

## **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the <u>OCD Auto-Baud Detector/Generator</u> section on page 183).

| Assembly      |                                         | Address<br>Mode |    | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|-----------------------------------------|-----------------|----|-------------|-------|---|---|---|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation                      | dst             |    |             |       | Ζ | S | V | D | Н | S              | S               |

| RRC dst       |                                         | R               |    | C0          | *     | * | * | * | _ | - | 2              | 2               |

|               | ► <u>D7D6D5D4D3D2D1D0</u> ►_C<br>dst    | IR              |    | C1          |       |   |   |   |   |   | 2              | 3               |

| SBC dst, src  | $dst \gets dst - src - C$               | r               | r  | 32          | *     | * | * | * | 1 | * | 2              | 3               |

|               | =                                       | r               | lr | 33          |       |   |   |   |   |   | 2              | 4               |

|               | -                                       | R               | R  | 34          |       |   |   |   |   |   | 3              | 3               |

|               | -                                       | R               | IR | 35          |       |   |   |   |   |   | 3              | 4               |

|               | -                                       | R               | IM | 36          |       |   |   |   |   |   | 3              | 3               |

|               | -                                       | IR              | IM | 37          |       |   |   |   |   |   | 3              | 4               |

| SBCX dst, src | $dst \gets dst - src - C$               | ER              | ER | 38          | *     | * | * | * | 1 | * | 4              | 3               |

|               | -                                       | ER              | IM | 39          |       |   |   |   |   |   | 4              | 3               |

| SCF           | C ← 1                                   |                 |    | DF          | 1     | - | _ | _ | _ | - | 1              | 2               |

| SRA dst       |                                         | R               |    | D0          | *     | * | * | 0 | _ | - | 2              | 2               |

|               | $- D7 D6 D5 D4 D3 D2 D1 D0 - C^{-}$ dst | IR              |    | D1          |       |   |   |   |   |   | 2              | 3               |

| SRL dst       | 0 - D7D6D5D4D3D2D1D0 - C                | R               |    | 1F C0       | *     | * | 0 | * | _ | _ | 3              | 2               |

|               | dst                                     | IR              |    | 1F C1       |       |   |   |   |   |   | 3              | 3               |

| SRP src       | RP ← src                                |                 | IM | 01          | _     | _ | _ | _ | _ | _ | 2              | 2               |

| STOP          | STOP Mode                               |                 |    | 6F          | _     | _ | _ | _ | _ | _ | 1              | 2               |

## Table 128. eZ8 CPU Instruction Summary (Continued)

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

219

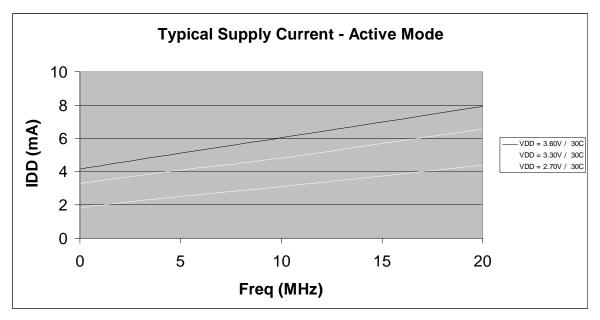

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode  $I_{\text{DD}}$  Versus System Clock Frequency

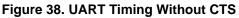

Figure 38 and Table 147 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 147 | UART T | imina Wit   | hout CTS |

|-----------|--------|-------------|----------|

|           |        | mining with |          |

|                |                                                                        | Delay (ns)                 |            |  |  |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                        |            |  |  |  |  |  |

| Z8 Encore! XP F082A | Lash<br>Series | Wey<br>with 2 | SO<br>AN<br>KB Flas | b. 10 Lines | Hiterrupts | and the second sec | 10-Bit A/D Channels | UART with IrDA | E Comparator | Temperature Sensor | Description         |

|---------------------|----------------|---------------|---------------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|--------------|--------------------|---------------------|

| Standard Temperatu  |                |               |                     |             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                   |                |              |                    |                     |

| Z8F022APB020SG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | PDIP 8-pin package  |

| Z8F022AQB020SG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | QFN 8-pin package   |

| Z8F022ASB020SG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | SOIC 8-pin package  |

| Z8F022ASH020SG      | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | SOIC 20-pin package |

| Z8F022AHH020SG      | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | SSOP 20-pin package |

| Z8F022APH020SG      | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | PDIP 20-pin package |

| Z8F022ASJ020SG      | 2 KB           | 512 B         | 64 B                | 23          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                   | 1              | 1            | 1                  | SOIC 28-pin package |

| Z8F022AHJ020SG      | 2 KB           | 512 B         | 64 B                | 23          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                   | 1              | 1            | 1                  | SSOP 28-pin package |

| Z8F022APJ020SG      | 2 KB           | 512 B         | 64 B                | 23          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                   | 1              | 1            | 1                  | PDIP 28-pin package |

| Extended Temperatu  | re: -40°       | °C to 10      | 5°C                 |             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                |              |                    |                     |

| Z8F022APB020EG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | PDIP 8-pin package  |

| Z8F022AQB020EG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | QFN 8-pin package   |

| Z8F022ASB020EG      | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | SOIC 8-pin package  |

| Z8F022ASH020EG      | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | SOIC 20-pin package |

| Z8F022AHH020EG      | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | SSOP 20-pin package |