#### Zilog - Z8F042AQB020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 000                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 x 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-VDFN Exposed Pad                                           |

| Supplier Device Package    | 8-QFN (5x6)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042aqb020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

| Address (Hex)  | Register Description              | Mnemonic | Reset (Hex) | Page      |

|----------------|-----------------------------------|----------|-------------|-----------|

| General-Purpos | e RAM                             |          |             |           |

| Z8F082A/Z8F08  | 1A Devices                        |          |             |           |

| 000–3FF        | General-Purpose Register File RAM | —        | XX          |           |

| 400–EFF        | Reserved                          | —        | XX          |           |

| Z8F042A/Z8F04  | 1A Devices                        |          |             |           |

| 000–3FF        | General-Purpose Register File RAM | —        | XX          |           |

| 400–EFF        | Reserved                          | —        | XX          |           |

| Z8F022A/Z8F02  | 1A Devices                        |          |             |           |

| 000–1FF        | General-Purpose Register File RAM | —        | XX          |           |

| 200–EFF        | Reserved                          | —        | XX          |           |

| Z8F012A/Z8F01  | 1A Devices                        |          |             |           |

| 000–0FF        | General-Purpose Register File RAM | _        | XX          |           |

| 100-EFF        | Reserved                          | —        | XX          |           |

| Timer 0        |                                   |          |             |           |

| F00            | Timer 0 High Byte                 | T0H      | 00          | <u>90</u> |

| F01            | Timer 0 Low Byte                  | TOL      | 01          | <u>90</u> |

| F02            | Timer 0 Reload High Byte          | TORH     | FF          | <u>91</u> |

| F03            | Timer 0 Reload Low Byte           | TORL     | FF          | <u>91</u> |

| F04            | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>92</u> |

| F05            | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>92</u> |

| F06            | Timer 0 Control 0                 | TOCTLO   | 00          | <u>85</u> |

| F07            | Timer 0 Control 1                 | T0CTL1   | 00          | <u>86</u> |

#### Table 7. Register File Address Map

Notes: 1. XX = Undefined.

2. Refer to the <u>eZ8</u> CPU <u>Core User Manual (UM0128)</u>.

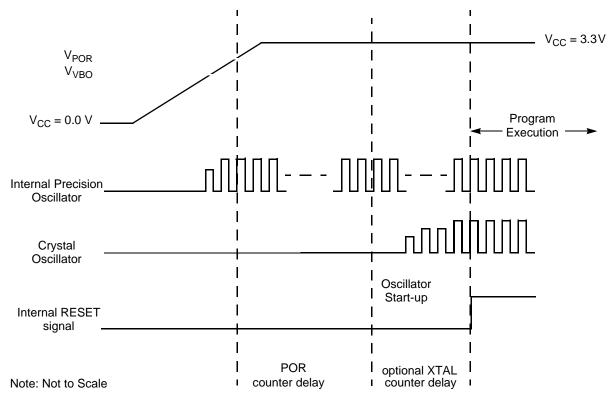

Figure 5. Power-On Reset Operation

# Voltage Brown-Out Reset

The devices in the Z8 Encore! XP F082A Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the Power-On Reset voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the Power-On Reset section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 6 displays Voltage Brown-Out operation. See the <u>Electrical</u> <u>Characteristics</u> chapter on page 226 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The Voltage Brown-Out circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO Flash option bit. See the <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information about configuring VBO\_AO. PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See **the** <u>Timers</u> **chapter on page 70** for more details.

**Caution:** For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF subregister. As a result, spurious transitions through unwanted alternate function modes will be prevented.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) Register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See **the** <u>Electrical Characteristics</u> chapter on page 226 for the maximum total current for the applicable package.

# **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/open-drain output reset until the software reconfigures it. The PD0 pin is an output-only open drain when in GPIO mode. There are no pull-up, High Drive, or Stop Mode Recovery source features associated with the PD0 pin.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its **RESET** alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, return the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8-and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Bit       | 7     | 6    | 5    | 4        | 3        | 2    | 1    | 0    |

|-----------|-------|------|------|----------|----------|------|------|------|

| Field     | PIN7  | PIN6 | PIN5 | PIN4     | PIN3     | PIN2 | PIN1 | PIN0 |

| RESET     | Х     | Х    | Х    | Х        | Х        | Х    | Х    | Х    |

| R/W       | R     | R    | R    | R        | R        | R    | R    | R    |

| Address   |       |      |      | FD2H, FD | 6H, FDAH |      |      |      |

| X = Undef | ined. |      |      |          |          |      |      |      |

Table 29. Port A–C Input Data Registers (PxIN)

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Output Data Register

The Port A–D Output Data Register, shown in Table 30, controls the output data to the pins.

| Bit     | 7     | 6                           | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |  |

|---------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Field   | POUT7 | POUT6                       | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |  |  |

| RESET   | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

| R/W     | R/W   | R/W R/W R/W R/W R/W R/W R/W |       |       |       |       |       |       |  |  |  |  |

| Address |       | FD3H, FD7H, FDBH, FDFH      |       |       |       |       |       |       |  |  |  |  |

Table 30. Port A–D Output Data Register (PxOUT)

#### Bit Description

[7:0] **Port Output Data** PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation. 0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM SINGLE OUTPUT Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:3]<br>PRES  | Prescale value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the Timer is disabled. This reset ensures proper clock division each time the<br>Timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                                                                                                                                                                                                |

| [2:0]<br>TMODE | Timer Mode<br>This field, along with the TMODEHI bit in the TxCTL0 Register, determines the operating mode<br>of the timer. TMODEHI is the most significant bit of the Timer mode selection value. The entire<br>operating mode bits are expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the<br>TxCTL0 Register while TMODE[2:0] is the lower 3 bits of the TxCTL1 Register.<br>0000 = ONE-SHOT Mode.<br>0001 = CONTINUOUS Mode.<br>0010 = COUNTER Mode.<br>0011 = PWM SINGLE OUTPUT Mode.<br>0100 = CAPTURE Mode.<br>0101 = COMPARE Mode.<br>0111 = CAPTURE/COMPARE Mode.<br>1000 = PWM DUAL OUTPUT Mode.<br>1001 = CAPTURE RESTART Mode.<br>1010 = COMPARATOR COUNTER Mode. |

### Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 52 and 53, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from TxL read the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value. 89

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | TH  |            |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     | F00H, F08H |     |     |     |     |     |     |  |  |  |

### Table 52. Timer 0–1 High Byte Register (TxH)

### Table 53. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7             | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|---------------|-----|-----|-------|------|-----|-----|-----|

| Field   | TL            |     |     |       |      |     |     |     |

| RESET   | 0 0 0 0 0 0 1 |     |     |       |      |     |     |     |

| R/W     | R/W           | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |               |     |     | F01H, | F09H |     |     |     |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

### **Output Data**

The output format of the corrected ADC value is shown below.

| MSB |   |   |   |   |   |   |   |   | Г | SB |   |   |   |   |   |

|-----|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|

| S   | v | b | а | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | _ | - |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary flag. For a normal (nonoverflow) sample, the sign and the overflow bit match. If the sign bit and overflow bit do not match, a computational overflow has occurred.

# **Input Buffer Stage**

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See <u>Table 139</u> on page 236 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

# **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register 0 (ADCCTL0): see page 134

ADC Control/Status Register 1 (ADCCTL1): see page 136

ADC Data High Byte Register (ADCD\_H): see page 137

ADC Data Low Byte Register (ADCD L): see page 137

| Bit    | Description (Continued)                                                                     |

|--------|---------------------------------------------------------------------------------------------|

| [5:2]  | Internal Reference Voltage Level                                                            |

| REFLVL | This reference is independent of the ADC voltage reference. Note: 8-pin devices contain two |

|        | additional LSBs for increased resolution.                                                   |

|        | For 20-/28-pin devices:                                                                     |

|        | 0000 = 0.0 V                                                                                |

|        | 0001 = 0.2 V                                                                                |

|        | 0010 = 0.4 V                                                                                |

|        | 0011 = 0.6 V                                                                                |

|        | 0100 = 0.8 V                                                                                |

|        | 0101 = 1.0 V (Default)                                                                      |

|        | 0110 = 1.2 V                                                                                |

|        | 0111 = 1.4 V                                                                                |

|        | 1000 = 1.6 V                                                                                |

|        | 1001 = 1.8 V                                                                                |

|        | 1010–1111 = Reserved                                                                        |

# **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7      | 7 6    |        | 6 5    |        | 5 4    |        | 2      | 1 | 0 |  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|---|---|--|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |   |   |  |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |   |   |  |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |   |   |  |  |

| Address |        | FF9H   |        |        |        |        |        |        |   |   |  |  |

Table 83. Flash Sector Protect Register (FPROT)

#### Bit Description

#### [7:0] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled High. At this point, the PA0/DBG pin may be used to autobaud and cause the device to enter DEBUG Mode. See the <u>OCD Unlock Sequence (8-Pin Devices Only) section on</u> page 185.

### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character transmitted and received by the OCD consists of 1 Start bit, 8 data bits (least-significant bit first) and 1 Stop bit as displayed in Figure 26.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

|           |    |    |    |    |    |    |    |    | 1    |

Figure 26. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open drain output to avoid this issue.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the

Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction and Execute Instruction commands.

DBG  $\leftarrow$  03H DBG  $\rightarrow$  RuntimeCounter[15:8] DBG  $\rightarrow$  RuntimeCounter[7:0]

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

DBG  $\leftarrow$  04H DBG  $\leftarrow$  OCDCTL[7:0]

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

DBG  $\leftarrow$  05H DBG  $\rightarrow$  OCDCTL[7:0]

**Write Program Counter (06H).** The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control registers are allowed and all other register write data values are discarded.

DBG  $\leftarrow$  08H DBG  $\leftarrow$  {4'h0,Register Address[11:8]} DBG  $\leftarrow$  Register Address[7:0] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-256 data bytes

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable1 = Failure detection of Watchdog Timer oscillator is enabled.0 = Failure detection of Watchdog Timer oscillator is disabled.                                                                                                                                                                                                                                             |

| [2:0]<br>SCKSEL | System Clock Oscillator Select000 = Internal precision oscillator functions as system clock at 5.53 MHz.001 = Internal precision oscillator functions as system clock at 32 kHz.010 = Crystal oscillator or external RC oscillator functions as system clock.011 = Watchdog Timer oscillator functions as system.100 = External clock signal on PB3 functions as system clock.101 = Reserved.110 = Reserved.111 = Reserved. |

| Notation | Description    | Operand | Range                                                                                                                     |

|----------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Vector   | Vector address | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| Х        | Indexed        | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to –128 range. |

#### Table 118. Notational Shorthand (Continued)

Table 119 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol                      | Definition                |  |  |  |  |  |  |

|-----------------------------|---------------------------|--|--|--|--|--|--|

| dst                         | Destination Operand       |  |  |  |  |  |  |

| src Source Operand          |                           |  |  |  |  |  |  |

| @ Indirect Address Prefix   |                           |  |  |  |  |  |  |

| SP                          | Stack Pointer             |  |  |  |  |  |  |

| PC                          | Program Counter           |  |  |  |  |  |  |

| FLAGS                       | Flags Register            |  |  |  |  |  |  |

| RP                          | Register Pointer          |  |  |  |  |  |  |

| #                           | Immediate Operand Prefix  |  |  |  |  |  |  |

| В                           | Binary Number Suffix      |  |  |  |  |  |  |

| %                           | Hexadecimal Number Prefix |  |  |  |  |  |  |

| H Hexadecimal Number Suffix |                           |  |  |  |  |  |  |

|                             |                           |  |  |  |  |  |  |

Table 119. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

208

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 120 through 127 list the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as *src*, the destination operand is *dst* and a condition code is *cc*.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 120. Arithmetic Instructions

### 242

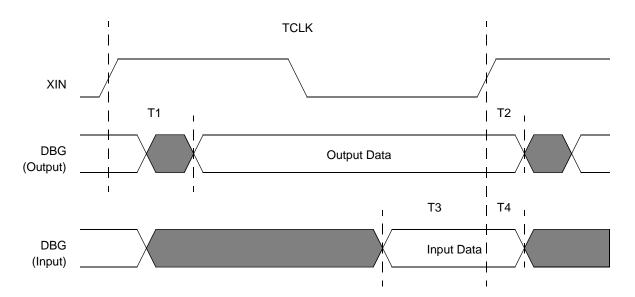

# **On-Chip Debugger Timing**

Figure 36 and Table 145 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                              | Delay (ns) |         |  |  |  |

|----------------|----------------------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |  |  |  |

| DBG            |                                              |            |         |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |  |  |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time             | 5          | -       |  |  |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time              | 5          | -       |  |  |  |

#### Table 145. On-Chip Debugger Timing

| Part Number                           | Flash    | RAM      | SDVN    | - I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------|----------|----------|---------|-------------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A                   |          |          | NB Flas | n           |            |                     |                     |                |            |                    |                     |

| Standard Temperatur<br>Z8F011APB020SG | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020SG                        | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020SG                        | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020SG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020SG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020SG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020SG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020SG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020SG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu                    | re: -40° | °C to 10 | 5°C     |             |            |                     |                     |                |            |                    |                     |

| Z8F011APB020EG                        | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F011AQB020EG                        | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F011ASB020EG                        | 1KB      | 256 B    | 16 B    | 6           | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F011ASH020EG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F011AHH020EG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F011APH020EG                        | 1KB      | 256 B    | 16 B    | 17          | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F011ASJ020EG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F011AHJ020EG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F011APJ020EG                        | 1KB      | 256 B    | 16 B    | 25          | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

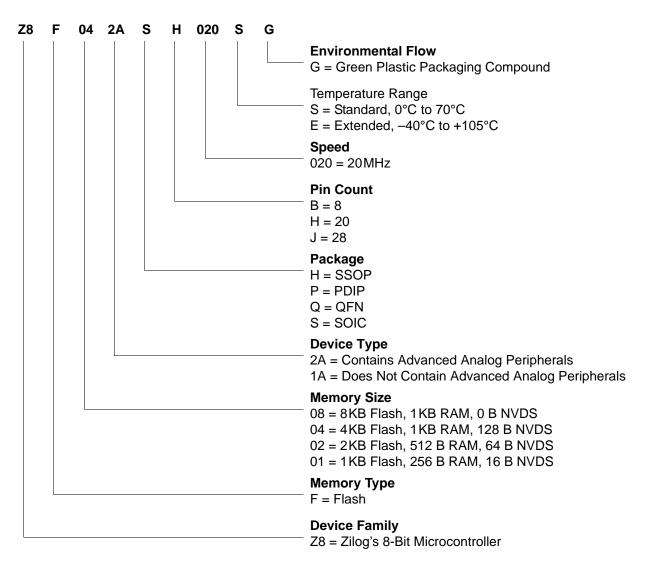

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.