# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 × 8                                                      |

| RAM Size                   | 1K × 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042ash020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                               | Description                                                                                                                                                                                 | Page<br>No.                                                |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Dec<br>2012 | 27                | Port Alternate Function Map-<br>ping (Non 8-Pin Parts), Port<br>Alternate Function Mapping (8-<br>Pin Parts)                  | Added missing Port D data to Table 15; cor-<br>rected active Low status (set overlines) for<br>PA0 (T0OUT), PA2 (RESET) and PA5<br>(T1OUT) in Table 16.                                     | <u>40, 43</u>                                              |

| Sep<br>2011 | 26                | LED Drive Enable Register                                                                                                     | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Flash Sector Protect Regis-<br>ter description; revised Packaging chapter. | <u>53,</u><br><u>157,</u><br>245                           |

| Sep<br>2008 | 25                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Added references to F042A Series back in Table 1, Table 5, Table 7 and Table 14.                                                                                                            | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| May<br>2008 | 24                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Changed title to Z8 Encore! XP F082A Series<br>and removed references to F042A Series in<br>Table 1, Table 5, Table 7 and Table 14.                                                         | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| Dec<br>2007 | 23                | Pin Description, General-Pur-<br>pose Input/Output, Watchdog<br>Timer                                                         | Updated Figure 3, Table 15, Tables 60 through 62.                                                                                                                                           | <u>9, 40,</u><br><u>97</u>                                 |

| Jul<br>2007 | 22                | Electrical Characteristics                                                                                                    | Updated Tables 16 and 132; power con-<br>sumption data.                                                                                                                                     | <u>43,</u><br>229                                          |

| Jun<br>2007 | 21                | n/a                                                                                                                           | Revision number update.                                                                                                                                                                     | All                                                        |

iii

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers64                 |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

### vi

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See the <u>Pin Configurations</u> section on page 8 to determine the signals available for the specific package styles.

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| General-Purpose I/0 | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| PA[7:0]             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |

| PB[7:0]             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |  |

| PC[7:0]             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |

| PD[0]               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |  |  |  |  |

| UART Controllers    |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TXD0                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |

| RXD0                | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |  |

| CTS0                | Ι       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |  |

| DE                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |

| Timers              |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| T0OUT/T1OUT         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |  |  |  |  |

| T0OUT/T1OUT         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |  |  |  |  |

| T0IN/T1IN           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and coun-<br>ter inputs.                                                                                                                                                                                                                 |  |  |  |  |

| Comparator          |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CINP/CINN           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |  |

| COUT                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |  |  |  |  |

#### **Table 2. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

#### Bit Description (Continued)

### [6] **GATED Mode**

- TPOL (cont'd)

- 0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

- 1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

- 1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

- 0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon reload. The PWMD field in TxCTL0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

- 1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon reload. The PWMD field in TxCTL0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload. Also:

0 =Count is captured on the rising edge of the comparator output.

1 = Count is captured on the falling edge of the comparator output.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port Data Direction Subregister is not required to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

- 6. Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-bit) Mode, further actions may be required depending on the MULTIPRO-CESSOR Mode bits MPMD[1:0].

- 7. Return to <u>Step 4</u> to receive additional data.

## **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (and error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request Register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR Modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

| Bit       | 7          | 6    | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------|------------|------|---|----|----|---|---|---|

| Field     |            |      |   | Tک | (D |   |   |   |

| RESET     | Х          | Х    | Х | Х  | Х  | Х | Х | Х |

| R/W       | W          | W    | W | W  | W  | W | W | W |

| Address   | 1          | F40H |   |    |    |   |   |   |

| Note: X = | Undefined. |      |   |    |    |   |   |   |

#### Table 67. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

# **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68 | . UART | Receive | Data | Register | (U0RXD) |

|----------|--------|---------|------|----------|---------|

|----------|--------|---------|------|----------|---------|

| Bit       | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------|------------|---|---|----|----|---|---|---|

| Field     |            |   |   | R۷ | (D |   |   |   |

| RESET     | Х          | Х | Х | Х  | Х  | Х | Х | Х |

| R/W       | R          | R | R | R  | R  | R | R | R |

| Address   | F40H       |   |   |    |    |   |   |   |

| Note: X = | Undefined. |   |   |    |    |   |   |   |

| Bit       | Descriptio | n |   |    |    |   |   |   |

| Dit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

## **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

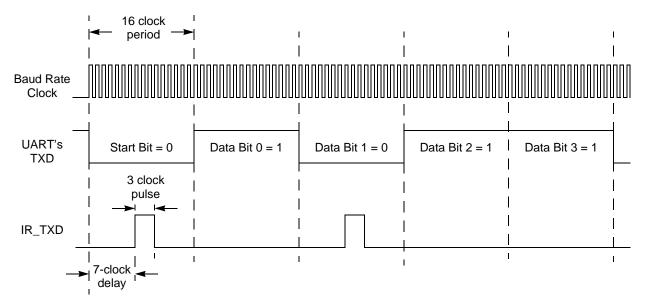

## **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

# Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

# Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

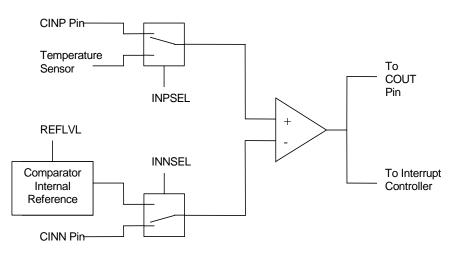

# Comparator

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Bit                   | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:4]<br>OSC_SEL[1:0] | <ul> <li>Oscillator Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [3]<br>VBO_AO         | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out Protection can be disabled in STOP Mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see the <u>Power Control Register Definitions</u> section on page 33).</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul>            |

| [2]<br>FRP            | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                              |

| [1]                   | Reserved<br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [0]<br>FWP            | <ul> <li>Flash Write Protect</li> <li>This Option Bit provides Flash Program Memory protection:</li> <li>0 = Programming and erasure disabled for all of Flash Program Memory. Programming,<br/>Page Erase and Mass Erase through User Code is disabled. Mass Erase is available<br/>using the On-Chip Debugger.</li> <li>1 = Programming, Page Erase and Mass Erase are enabled for all of Flash program<br/>memory.</li> </ul>                                                               |

163

| Info Page | Memory  |                         |                          |                |

|-----------|---------|-------------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage      | ADC Mode                 | Reference Type |

| 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 72        | FE72    | Offset                  | Differential Unbuffered  | Internal 1.0 V |

| 14        | FE14    | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 15        | FE15    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 32        | FE32    | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 33        | FE33    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 75        | FE75    | Offset                  | Differential Unbuffered  | External 2.0 V |

| 16        | FE16    | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 17        | FE17    | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 34        | FE34    | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 35        | FE35    | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 78        | FE78    | Offset                  | Differential 1x Buffered | Internal 2.0 V |

| 18        | FE18    | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 19        | FE19    | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 36        | FE36    | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 37        | FE37    | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 7B        | FE7B    | Offset                  | Differential 1x Buffered | External 2.0 V |

| 1A        | FE1A    | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 1B        | FE1B    | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

| 38        | FE38    | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 39        | FE39    | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

### Table 97. ADC Calibration Data Location (Continued)

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series device. When this option is enabled, several of the OCD commands are disabled. See Table 109.

<u>Table 110</u> on page 191 is a summary of the on-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 110 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | _                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                    |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Table 109. Debug Command Enable/Disable | Table 109. | Debug | Command | Enable/Disable |

|-----------------------------------------|------------|-------|---------|----------------|

|-----------------------------------------|------------|-------|---------|----------------|

| Notation | Description    | Operand | Range                                                                                                                     |

|----------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Vector   | Vector address | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| Х        | Indexed        | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to –128 range. |

#### Table 118. Notational Shorthand (Continued)

Table 119 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 119. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

214

| Assembly      |                                          |         | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>- Cycle | Instr.<br>Cycle |

|---------------|------------------------------------------|---------|-------------|-------------|---|---|-----|-----|---|---|------------------|-----------------|

| Mnemonic      | Symbolic Operation                       | dst src |             | (Hex)       | С | Ζ | S   | S V |   | Н | S                | S               |

| CALL dst      | $SP \leftarrow SP - 2$                   | IRR     |             | D4          | _ | - | _   | _   | - | _ | 2                | 6               |

|               | $@SP \leftarrow PC \\ PC \leftarrow dst$ | DA      |             | D6          | - |   |     |     |   |   | 3                | 3               |

| CCF           | $C \leftarrow \sim C$                    |         |             | EF          | * | - | _   | -   | - |   | 1                | 2               |

| CLR dst       | dst ← 00H                                | R       |             | B0          | _ | _ | _   | _   | _ | _ | 2                | 2               |

|               |                                          | IR      |             | B1          | - |   |     |     |   |   | 2                | 3               |

| COM dst       | dst ← ~dst                               | R       |             | 60          | _ | * | *   | 0   | _ | _ | 2                | 2               |

|               |                                          | IR      |             | 61          | - |   |     |     |   |   | 2                | 3               |

| CP dst, src   | dst - src                                | r       | r           | A2          | * | * | *   | *   | _ | _ | 2                | 3               |

|               |                                          | r       | Ir          | A3          | - |   |     |     |   |   | 2                | 4               |

|               |                                          | R       | R           | A4          | - |   |     |     |   |   | 3                | 3               |

|               |                                          | R       | IR          | A5          | - |   |     |     |   |   | 3                | 4               |

|               |                                          | R       | IM          | A6          | - |   |     |     |   |   | 3                | 3               |

|               |                                          | IR      | IM          | A7          | - |   |     |     |   |   | 3                | 4               |

| CPC dst, src  | dst - src - C                            | r       | r           | 1F A2       | * | * | *   | *   | _ | _ | 3                | 3               |

|               |                                          | r       | Ir          | 1F A3       | - |   |     |     |   |   | 3                | 4               |

|               |                                          | R       | R           | 1F A4       | - |   |     |     |   |   | 4                | 3               |

|               |                                          | R       | IR          | 1F A5       | - |   |     |     |   |   | 4                | 4               |

|               |                                          | R       | IM          | 1F A6       | - |   |     |     |   |   | 4                | 3               |

|               |                                          | IR      | IM          | 1F A7       | - |   |     |     |   |   | 4                | 4               |

| CPCX dst, src | dst - src - C                            | ER      | ER          | 1F A8       | * | * | *   | *   | _ | _ | 5                | 3               |

|               |                                          | ER      | IM          | 1F A9       | - |   |     |     |   |   | 5                | 3               |

| CPX dst, src  | dst - src                                | ER      | ER          | A8          | * | * | *   | *   | _ | _ | 4                | 3               |

|               |                                          | ER      | IM          | A9          | - |   |     |     |   |   | 4                | 3               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|               |                                         |                 |      | •           |   |   |     | '              |                 |   |   |   |

|---------------|-----------------------------------------|-----------------|------|-------------|---|---|-----|----------------|-----------------|---|---|---|

| Assembly      |                                         | Address<br>Mode |      | _ Opcode(s) |   |   | Fla | Fetch<br>Cycle | Instr.<br>Cycle |   |   |   |

| Mnemonic      | Symbolic Operation                      | dst             | src  | (Hex)       |   | Ζ | s v |                | D               | Н | s | s |

| JR dst        | $PC \gets PC + X$                       | DA              |      | 8B          | _ | _ | _   | _              | _               | _ | 2 | 2 |

| JR cc, dst    | if cc is true<br>PC $\leftarrow$ PC + X | DA              |      | 0B-FB       | _ | - | -   | _              | -               | _ | 2 | 2 |

| LD dst, rc    | dst $\leftarrow$ src                    | r               | IM   | 0C-FC       | _ | _ | _   | _              | _               | _ | 2 | 2 |

|               |                                         | r               | X(r) | C7          | - |   |     |                |                 |   | 3 | 3 |

|               |                                         | X(r)            | r    | D7          | - |   |     |                |                 |   | 3 | 4 |

|               |                                         | r               | lr   | E3          | - |   |     |                |                 |   | 2 | 3 |

|               |                                         | R               | R    | E4          | - |   |     |                |                 |   | 3 | 2 |

|               |                                         | R               | IR   | E5          | - |   |     |                |                 |   | 3 | 4 |

|               |                                         | R               | IM   | E6          | _ |   |     |                |                 |   | 3 | 2 |

|               |                                         | IR              | IM   | E7          | _ |   |     |                |                 |   | 3 | 3 |

|               |                                         | lr              | r    | F3          | _ |   |     |                |                 |   | 2 | 3 |

|               |                                         | IR              | R    | F5          | _ |   |     |                |                 |   | 3 | 3 |

| LDC dst, src  | dst $\leftarrow$ src                    | r               | Irr  | C2          | _ | _ | _   | _              | _               | _ | 2 | 5 |

|               |                                         | lr              | Irr  | C5          | _ |   |     |                |                 |   | 2 | 9 |

|               |                                         | Irr             | r    | D2          | _ |   |     |                |                 |   | 2 | 5 |

| LDCI dst, src | dst ← src                               | lr              | Irr  | C3          | _ | _ | _   | _              | _               | _ | 2 | 9 |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | D3          | _ |   |     |                |                 |   | 2 | 9 |

| LDE dst, src  | dst ← src                               | r               | Irr  | 82          | _ | _ | _   | _              | _               | _ | 2 | 5 |

|               |                                         | Irr             | r    | 92          | - |   |     |                |                 |   | 2 | 5 |

| LDEI dst, src | dst $\leftarrow$ src                    | lr              | Irr  | 83          | _ | - | _   | _              | _               | - | 2 | 9 |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | 93          | - |   |     |                |                 |   | 2 | 9 |

| LDWX dst, src | dst ← src                               | ER              | ER   | 1FE8        | _ | _ | _   | -              | _               | _ | 5 | 4 |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

# **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 135 tabulates the electrical characteristics of the POR and VBO blocks.

### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                  | T <sub>A</sub> = | –40°C to +′          |         |       |                                                                                                             |  |

|------------------|------------------------------------------------------------------|------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                        | Minimum          | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                                  |  |

| V <sub>POR</sub> | Power-On Reset Voltage Thresh-<br>old                            | 2.20             | 2.45                 | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                          |  |

| V <sub>VBO</sub> | Voltage Brown-Out Reset Voltage<br>Threshold                     | 2.15             | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                          |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                  |                  | 50                   | 75      | mV    |                                                                                                             |  |

|                  | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset. | -                | $V_{SS}$             | -       | V     |                                                                                                             |  |

| T <sub>ANA</sub> | Power-On Reset Analog Delay                                      | -                | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay<br>follows T <sub>ANA</sub> |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> )             |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator disabled              |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles                                                            |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator enabled               |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>VBO</sub> | Voltage Brown-Out Pulse Rejec-<br>tion Period                    | _                | 10                   | _       | μs    | Period of time<br>in which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.                             |  |

Note: Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

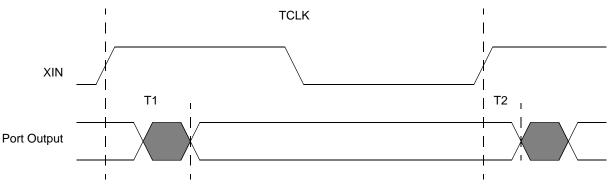

# General Purpose I/O Port Output Timing

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Delay (ns) |         |  |  |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |  |  |

| GPIO port pi   | ns                                              |            |         |  |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 15      |  |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |

### Table 144. GPIO Port Output Timing

| Part Number         | Flash     | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|-----------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |           |         | (B Flas | sh        |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |           |         |         |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40° | C to 10 | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

254

|                        | Flash | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |

|------------------------|-------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|

| Z8 Encore! XP F082A Se | eries | Develo  | pment   | Kit       |            |                     |                     |                |            |                    |             |

| Z8F08A28100KITG        |       | Z8 Enco | ore! XP | F082/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A28100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A08100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 8               | -Pin l              | Deve           | opme       | ent Kit            |             |

| ZUSBSC00100ZACG        |       | USB Sn  | nart Ca | ble Ac    | cess       | ory K               | it                  |                |            |                    |             |

| ZUSBOPTSC01ZACG        |       | USB Op  | to-Isol | ated S    | mart       | Cabl                | e Aco               | cesso          | ry Kit     |                    |             |

| ZENETSC0100ZACG        |       | Etherne | t Smar  | t Cable   | e Acc      | esso                | ry Kit              |                |            |                    |             |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix