Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 128 × 8                                                      |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f042asj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

# Features

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See the <u>Pin Configurations</u> section on page 8 to determine the signals available for the specific package styles.

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| General-Purpose I/0 | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| PA[7:0]             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |

| PB[7:0]             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |  |

| PC[7:0]             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |  |

| PD[0]               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |  |  |  |  |

| UART Controllers    |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TXD0                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |  |

| RXD0                | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |  |

| CTS0                | Ι       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |  |

| DE                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |  |

| Timers              |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| T0OUT/T1OUT         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |  |  |  |  |

| T0OUT/T1OUT         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |  |  |  |  |

| T0IN/T1IN           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and coun-<br>ter inputs.                                                                                                                                                                                                                 |  |  |  |  |

| Comparator          |         |                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CINP/CINN           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |  |

| COUT                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |  |  |  |  |

#### **Table 2. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

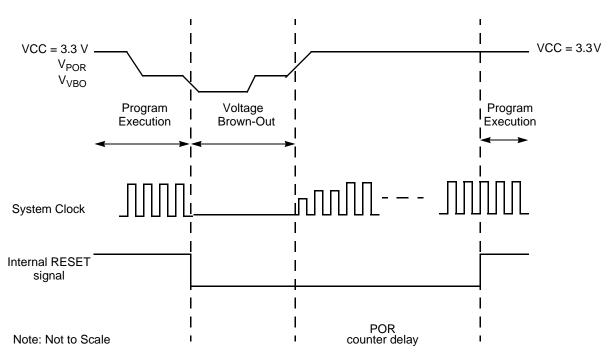

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

# **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

tor address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                   | Action                                                               |  |  |  |  |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

| STOP Mode      | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |  |  |  |  |

|                | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |  |  |  |  |

|                | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |  |  |  |  |

|                | Assertion of external RESET Pin                                             | System Reset                                                         |  |  |  |  |

|                | Debug Pin driven Low                                                        | System Reset                                                         |  |  |  |  |

### Table 10. Stop Mode Recovery Sources and Resulting Action

# Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

# Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

• Note: SMR pulses shorter than specified do not trigger a recovery (see <u>Table 135</u> on page 233). In this instance, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or

# **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----------------------------|---|---|---|---|---|---|---|--|--|--|

| Field   | PCTL                        |   |   |   |   |   |   |   |  |  |  |

| RESET   | 00H                         |   |   |   |   |   |   |   |  |  |  |

| R/W     | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |   |  |  |  |

| Address | FD1H, FD5H, FD9H, FDDH      |   |   |   |   |   |   |   |  |  |  |

### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |  |  |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |  |  |  |  |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer Reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults and other system-level problems which may place the Z8 Encore! XP F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequen |                        |  |  |  |  |

|------------------|------------------|--------------------------------------------------------------------------|------------------------|--|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                                  | Description            |  |  |  |  |

| 000004           | 4                | 400 μs                                                                   | Minimum time-out delay |  |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                               | Maximum time-out delay |  |  |  |  |

### Table 58. Watchdog Timer Approximate Time-Out Delays

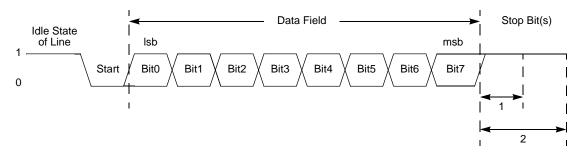

Figure 11. UART Asynchronous Data Format without Parity

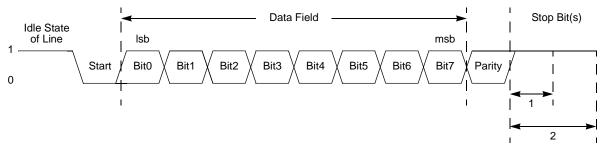

Figure 12. UART Asynchronous Data Format with Parity

# **Transmitting Data using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled and select either even or odd parity (PSEL)

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 8. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART Transmit interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Write the UART Control 1 Register to select the multiprocessor bit for the byte to be transmitted:

- 2. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 3. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 4. Clear the UART Transmit interrupt bit in the applicable Interrupt Request Register.

- 5. Execute the IRET instruction to return from the interrupt-service routine and wait for the Transmit Data Register to again become empty.

### **Receiving Data using the Polled Method**

Observe the following steps to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set an acceptable baud rate for the incoming data stream.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable MULTIPROCESSOR Mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if Multiprocessor mode is not enabled and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by a 1). If RDA is set to 1 to indicate available data, continue to <u>Step 5</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register. When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

113

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

DBG  $\leftarrow$  09H DBG  $\leftarrow$  {4'h0,Register Address[11:8] DBG  $\leftarrow$  Register Address[7:0] DBG  $\leftarrow$  Size[7:0] DBG  $\rightarrow$  1-256 data bytes

**Write Program Memory (0AH).** The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Write Data Memory (0CH).** The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0CH DBG  $\leftarrow$  Data Memory Address[15:8] DBG  $\leftarrow$  Data Memory Address[7:0]

| Assembly         |                                                                                           | Address<br>Mode<br>Opcode(s) |     |       |   |     | Fla | ags | Fetch<br>Cycle | Instr.<br>Cycle |   |   |

|------------------|-------------------------------------------------------------------------------------------|------------------------------|-----|-------|---|-----|-----|-----|----------------|-----------------|---|---|

| Mnemonic         | Symbolic Operation                                                                        | dst                          | src | (Hex) | С | Ζ   | S   | V   | D              | Н               | S | S |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r                            | r   | 52    | _ | *   | *   | 0   | _              | _               | 2 | 3 |

|                  |                                                                                           | r                            | Ir  | 53    |   |     |     |     |                |                 | 2 | 4 |

|                  |                                                                                           | R                            | R   | 54    |   |     |     |     |                |                 | 3 | 3 |

|                  |                                                                                           | R                            | IR  | 55    |   |     |     |     |                |                 | 3 | 4 |

|                  |                                                                                           | R                            | IM  | 56    |   |     |     |     |                |                 | 3 | 3 |

|                  |                                                                                           | IR                           | IM  | 57    |   |     |     |     |                |                 | 3 | 4 |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER                           | ER  | 58    | - | - * | *   | 0   | -              | -               | 4 | 3 |

|                  |                                                                                           | ER                           | IM  | 59    |   |     |     |     |                |                 | 4 | 3 |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |                              |     | 2F    | - | -   | _   | _   | _              | _               | 1 | 2 |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r                            |     | E2    | - | _   | _   | _   | _              | _               | 2 | 2 |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r                            |     | E2    | - | _   | -   | -   | _              | -               | 2 | 2 |

| BRK              | Debugger Break                                                                            |                              |     | 00    | - | _   | -   | -   | _              | -               | 1 | 1 |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r                            |     | E2    | - | _   | -   | -   | _              | -               | 2 | 2 |

| BSWAP dst        | $dst[7:0] \leftarrow dst[0:7]$                                                            | R                            |     | D5    | Х | *   | *   | 0   | _              | -               | 2 | 2 |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                              | r   | F6    | - | _   | -   | -   | _              | -               | 3 | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                              | lr  | F7    |   |     |     |     |                |                 | 3 | 4 |

| BTJNZ bit, src,  | if src[bit] = 1                                                                           |                              | r   | F6    | - | _   | -   | -   | -              | -               | 3 | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                              | lr  | F7    |   |     |     |     |                |                 | 3 | 4 |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                              | r   | F6    | - | _   | -   | -   | -              | -               | 3 | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                              | lr  | F7    |   |     |     |     |                |                 | 3 | 4 |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly        |                                     |       | ress<br>ode | _ Opcode(s) |   |   | Fla | ags | Fetch<br>Cycle | Instr.<br>Cycle |   |   |

|-----------------|-------------------------------------|-------|-------------|-------------|---|---|-----|-----|----------------|-----------------|---|---|

| Mnemonic        | Symbolic Operation                  | dst   | src         | (Hex)       |   | Ζ | S   | v   | D              | н               | S | S |

| LDX dst, src    | $dst \leftarrow src$                | r     | ER          | 84          | - | - | -   | -   | _              | -               | 3 | 2 |

|                 |                                     | lr    | ER          | 85          |   |   |     |     |                |                 | 3 | 3 |

|                 |                                     | R     | IRR         | 86          | - |   |     |     |                |                 | 3 | 4 |

|                 |                                     | IR    | IRR         | 87          |   |   |     |     |                |                 | 3 | 5 |

|                 |                                     | r     | X(rr)       | 88          |   |   |     |     |                |                 | 3 | 4 |

|                 |                                     | X(rr) | r           | 89          |   |   |     |     |                |                 | 3 | 4 |

|                 |                                     | ER    | r           | 94          |   |   |     |     |                |                 | 3 | 2 |

|                 |                                     | ER    | lr          | 95          |   |   |     |     |                |                 | 3 | 3 |

|                 |                                     | IRR   | R           | 96          |   |   |     |     |                |                 | 3 | 4 |

|                 |                                     | IRR   | IR          | 97          | - |   |     |     |                |                 | 3 | 5 |

|                 |                                     | ER    | ER          | E8          | - |   |     |     |                |                 | 4 | 2 |

|                 |                                     | ER    | IM          | E9          | - |   |     |     |                |                 | 4 | 2 |

| LEA dst, X(src) | $dst \gets src + X$                 | r     | X(r)        | 98          | _ | - | -   | -   | -              | -               | 3 | 3 |

|                 |                                     | rr    | X(rr)       | 99          |   |   |     |     |                |                 | 3 | 5 |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4          | _ | - | _   | -   | -              | _               | 2 | 8 |

| NOP             | No operation                        |       |             | 0F          | - | - | -   | -   | -              | -               | 1 | 2 |

| OR dst, src     | $dst \gets dst  OR  src$            | r     | r           | 42          | _ | * | *   | 0   | -              | -               | 2 | 3 |

|                 |                                     | r     | lr          | 43          | - |   |     |     |                |                 | 2 | 4 |

|                 |                                     | R     | R           | 44          |   |   |     |     |                |                 | 3 | 3 |

|                 |                                     | R     | IR          | 45          |   |   |     |     |                |                 | 3 | 4 |

|                 |                                     | R     | IM          | 46          | - |   |     |     |                |                 | 3 | 3 |

|                 |                                     | IR    | IM          | 47          | - |   |     |     |                |                 | 3 | 4 |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | ) = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                      |  |  |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                               | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |  |  |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |  |  |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                  | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |  |  |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |  |  |

### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

|                     |                          | T <sub>A</sub> = - | = 2.7 V to<br>-40°C to +<br>otherwise | -105°C      |       |                                                                                                    |  |

|---------------------|--------------------------|--------------------|---------------------------------------|-------------|-------|----------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                | Minimum            | Typical                               | Maximum     | Units | Conditions                                                                                         |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                    | 10                                    |             | kHz   |                                                                                                    |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                    |                                       | <u>+</u> 50 | %     |                                                                                                    |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Time-out  | 0.98               | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3V;<br>T <sub>A</sub> = 30°C                                                   |  |

|                     |                          | 0.70               | 1                                     | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ}\text{C} \text{ to } 70^{\circ}\text{C}$     |  |

|                     |                          | 0.50               | 1                                     | 1.50        | S     | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$<br>$T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ |  |

### Table 137. Watchdog Timer Electrical Characteristics and Timing

### Table 138. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>-40°C to + |         |        |                                           |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |

| NVDS Byte Read Time    | 34      | _                        | 519     | μs     | With system clock at 20MHz                |

| NVDS Byte Program Time | 0.171   | _                        | 39.7    | ms     | With system clock at 20MHz                |

| Data Retention         | 100     | _                        | -       | years  | 25°C                                      |

| Endurance              | 160,000 | _                        | _       | cycles | Cumulative write cycles for entire memory |

| ning (Continued) |  |

|------------------|--|

|                  |  |

### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

### $V_{DD}$ = 3.0 V to 3.6 V T<sub>A</sub> = 0°C to +70°C (unless otherwise stated)

| Symbol         | Parameter                     | Minimum | Typical | Maximum              | Units                          | Conditions                                                                                                                                                                                                                                |

|----------------|-------------------------------|---------|---------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Continuous Conversion<br>Time | -       | 256     | _                    | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                                   |

|                |                               |         | 512     |                      |                                | Temperature sensor measurement                                                                                                                                                                                                            |

|                | Signal Input Bandwidth        | _       | 10      |                      | kHz                            | As defined by -3 dB point                                                                                                                                                                                                                 |

| R <sub>S</sub> | Analog Source                 | _       | _       | 10                   | kΩ                             | In unbuffered mode                                                                                                                                                                                                                        |

|                | Impedance <sup>4</sup>        |         |         | 500                  | kΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Zin            | Input Impedance               | -       | 150     |                      | kΩ                             | In unbuffered mode at 20MHz <sup>5</sup>                                                                                                                                                                                                  |

|                |                               | 10      | _       |                      | MΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Vin            | Input Voltage Range           | 0       |         | V <sub>DD</sub>      | V                              | Unbuffered Mode                                                                                                                                                                                                                           |

|                |                               | 0.3     |         | V <sub>DD</sub> -1.1 | V                              | Buffered Modes<br>These values define<br>the range over which<br>the ADC performs<br>within spec; exceeding<br>these values does not<br>cause damage or insta-<br>bility; see DC Charac-<br>teristics for absolute<br>pin voltage limits. |

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

# **Ordering Information**

Order your F082A Series products from Zilog using the part numbers shown in Table 148. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                     |                 | 40. 20   |         |           | 002/       |                     | 163 (               | Jiuei          | ing n      | au                 | ^                   |

|---------------------|-----------------|----------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Part Number         | Flash           | RAM      | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

| Z8 Encore! XP F082A | <b>A Series</b> | with 8   | (B Flas | sh, 10    | -Bit A     | Analo               | og-to               | Digit          | al Co      | onve               | erter               |

| Standard Temperatu  | re: 0°C t       | to 70°C  |         |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020SG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40°       | 'C to 10 | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EG      | 8KB             | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EG      | 8KB             | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EG      | 8KB             | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Part Number         | Flash     | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|-----------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |           |         | (B Flas | sh        |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |           |         |         |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40° | C to 10 | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Jaquin<br>N<br>Tred<br>Z8 Encore! XP F082A | Elash    | RAM     | SQ N<br>N<br>KB Elas | // V Lines    | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|--------------------------------------------|----------|---------|----------------------|---------------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Standard Temperatur                        |          |         |                      | п, т <b>с</b> |            | Anan                | Jy-10               | -Digi          |            | 51100              |                     |

| Z8F042APB020SG                             | 4 KB     | 1KB     | ,<br>128 B           | 6             | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020SG                             | 4 KB     | 1KB     | 128 B                | 6             | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020SG                             | 4 KB     | 1KB     | 128 B                | 6             | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |