# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081ahh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F082A Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see <u>Table 20 on page 46</u>), the <u>RESET</u> pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

STOP Mode is entered by execution of a STOP instruction by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 32 for detailed STOP Mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see <u>Table 135</u> on page 233)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vec-

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6            | 5                             | 4                              | 3                             | 2                      | 1 | 0           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------|--------------------------------|-------------------------------|------------------------|---|-------------|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                         | STOP         | WDT                           | EXT                            |                               | Reserved               |   | LVD         |

| RESET       | See c                                                                                                                                                                                                                                                                                                                                                                                                                                                       | lescriptions | below                         | 0                              | 0                             | 0                      | 0 | 0           |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R            | R                             | R                              | R                             | R                      | R | R           |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                               | FF                             | ЮH                            |                        |   |             |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n            |                               |                                |                               |                        |   |             |

| [7]<br>POR  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | ower-On Re                    |                                | ccurs. This t<br>set to 0 whe |                        |   | time-out or |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1<br>the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT<br>bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a<br>Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this regis<br>ter also resets this bit. |              |                               |                                |                               | id the WDT<br>set by a |   |             |

| [5]<br>WDT  | If this bit is from a char                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | /DT time-ou<br>out pin also r | t occurs. A l<br>esets this bi | POR resets<br>t. Reading th   |                        |   |             |

| [4]<br>EXT  | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurs. A Power-On Reset<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                                                  |              |                               |                                |                               |                        |   |             |

| [3:1]       | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                      | are reserved | d and must b                  | be programn                    | ned to 000.                   |                        |   |             |

| [0]<br>LVD  | These bits are reserved and must be programmed to 000.<br><b>Low Voltage Detection Indicator</b><br>If this bit is set to 1 the current state of the supply voltage is below the low voltage detection<br>threshold. This value is not latched but is a real-time indicator of the supply voltage level.                                                                                                                                                    |              |                               |                                |                               |                        |   |             |

### Table 11. Reset Status Register (RSTSTAT)

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

## **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

## Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7             | 6                                                                                                  | 5 | 4  | 3        | 2 | 1 | 0 |

|---------|---------------|----------------------------------------------------------------------------------------------------|---|----|----------|---|---|---|

| Field   | IRQE          |                                                                                                    |   |    | Reserved |   |   |   |

| RESET   | 0             | 0                                                                                                  | 0 | 0  | 0        | 0 | 0 | 0 |

| R/W     | R/W           | R                                                                                                  | R | R  | R        | R | R | R |

| Address |               |                                                                                                    |   | FC | FH       |   |   |   |

| Bit     | Descriptio    | n                                                                                                  |   |    |          |   |   |   |

| [7]     | Interrupt R   | nterrupt Request Enable                                                                            |   |    |          |   |   |   |

| IRQE    | This bit is s | nis bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, |   |    |          |   |   |   |

### Table 49. Interrupt Control Register (IRQCTL)

| ЫІ    | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | Interrupt Request Enable                                                                                                                                                                                                                                                                                                                       |

| IRQE  | This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.<br>0 = Interrupts are disabled. |

|       | 1 = Interrupts are enabled.                                                                                                                                                                                                                                                                                                                    |

| [6:0] | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                |

# **Timers**

These Z8 Encore! XP F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information about using the Baud Rate Generator as an additional timer, see the <u>Universal Asynchronous Receiver/</u> <u>Transmitter</u> chapter on page 99.

# Architecture

Figure 9 displays the architecture of the timers.

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

## **Timer Pin Signal Operation**

The timer output function is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

# **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers, shown in Tables 65 and 66, identify the current UART operating configuration and status.

| Table 65. | UART | Status 0 | Register | (U0STAT0) |

|-----------|------|----------|----------|-----------|

|-----------|------|----------|----------|-----------|

| Bit         | 7                                                                                                                                                                                                                                                                                                                                            | 6                          | 5                                         | 4  | 3           | 2           | 1                          | 0        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|----|-------------|-------------|----------------------------|----------|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                          | PE                         | OE                                        | FE | BRKD        | TDRE        | TXE                        | CTS      |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                            | 0                          | 0                                         | 0  | 0           | 1           | 1                          | Х        |

| R/W         | R                                                                                                                                                                                                                                                                                                                                            | R                          | R                                         | R  | R           | R           | R                          | R        |

| Address     |                                                                                                                                                                                                                                                                                                                                              |                            |                                           | F4 | 1H          |             |                            |          |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                   | n                          |                                           |    |             |             |                            |          |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                                                    | ita Register<br>RT Receive | he UART Re<br>clears this b<br>Data Regis |    | C           | received da | ata. Reading               | the UART |

| [6]<br>PE   | <ul> <li>Parity Error</li> <li>This bit indicates that a parity error has occurred. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No parity error has occurred.</li> <li>1 = A parity error has occurred.</li> </ul>                                                                                                  |                            |                                           |    |             | Register    |                            |          |

| [5]<br>OE   | received an<br>reading the<br>0 = No over                                                                                                                                                                                                                                                                                                    | cates that a<br>d the UART | Receive Da<br>eive Data Re<br>curred.     |    | has not bee |             | s when new<br>e RDA bit is |          |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                                  |                            |                                           |    |             | ected.      |                            |          |

| [3]<br>BRKD | <ul> <li>1 = A framing error occurred.</li> <li>Break Detect</li> <li>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit and Stop bits are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No break occurred.</li> <li>1 = A break occurred.</li> </ul> |                            |                                           |    |             |             |                            |          |

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | N/A                      | N/A                  | N/A          | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 1                        | 223.72               | -10.51       | 250.0                    | N/A                      | N/A                  | N/A          |

| 115.2                    | 2                        | 111.9                | -2.90        | 115.2                    | 1                        | 115.2                | 0.00         |

| 57.6                     | 4                        | 55.9                 | -2.90        | 57.6                     | 2                        | 57.6                 | 0.00         |

| 38.4                     | 6                        | 37.3                 | -2.90        | 38.4                     | 3                        | 38.4                 | 0.00         |

| 19.2                     | 12                       | 18.6                 | -2.90        | 19.2                     | 6                        | 19.2                 | 0.00         |

| 9.60                     | 23                       | 9.73                 | 1.32         | 9.60                     | 12                       | 9.60                 | 0.00         |

| 4.80                     | 47                       | 4.76                 | -0.83        | 4.80                     | 24                       | 4.80                 | 0.00         |

| 2.40                     | 93                       | 2.41                 | 0.23         | 2.40                     | 48                       | 2.40                 | 0.00         |

| 1.20                     | 186                      | 1.20                 | 0.23         | 1.20                     | 96                       | 1.20                 | 0.00         |

| 0.60                     | 373                      | 0.60                 | -0.04        | 0.60                     | 192                      | 0.60                 | 0.00         |

| 0.30                     | 746                      | 0.30                 | -0.04        | 0.30                     | 384                      | 0.30                 | 0.00         |

|                          |                          |                      |              |                          |                          |                      |              |

### Table 72. UART Baud Rates (Continued)

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

## Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

# Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

# Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

The following code example illustrates how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

nop         ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definition**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit     | 7      | 6      | 5      | 4   | 3   | 2   | 1                    | 0   |

|---------|--------|--------|--------|-----|-----|-----|----------------------|-----|

| Field   | INPSEL | INNSEL | REFLVL |     |     |     | Reserved (<br>REFLVL |     |

| RESET   | 0      | 0      | 0      | 1   | 0   | 1   | 0                    | 0   |

| R/W     | R/W    | R/W    | R/W    | R/W | R/W | R/W | R/W                  | R/W |

| Address |        |        |        | F9  | 0H  |     |                      |     |

Table 77. Comparator Control Register (CMP0)

| Bit    | Description                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]    | Signal Select for Positive Input                                                                                                                                       |

| INPSEL | 0 = GPIO pin used as positive comparator input.                                                                                                                        |

|        | <ol> <li>Temperature sensor used as positive comparator input.</li> </ol>                                                                                              |

| [6]    | Signal Select for Negative Input                                                                                                                                       |

| INNSEL | <ul> <li>0 = Internal reference disabled, GPIO pin used as negative comparator input.</li> <li>1 = Internal reference enabled as negative comparator input.</li> </ul> |

# Flash Page Select Register

The Flash Page Select (FPS) Register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

| Bit     | 7       | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|---------|---------|-----|-----|-----|------|-----|-----|-----|

| Field   | INFO_EN |     |     |     | PAGE |     |     |     |

| RESET   | 0       | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W     | R/W     | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| Address |         |     |     | FF  | 9H   |     |     |     |

#### Table 82. Flash Page Select Register (FPS)

#### Bit Description

#### [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

# 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7           | 6                             | 5              | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------|-------------------------------|----------------|-----|-----|-----|-----|-----|

| Field     |             | WDTCALL                       |                |     |     |     |     |     |

| RESET     | U           | U                             | U              | U   | U   | U   | U   | U   |

| R/W       | R/W         | R/W                           | R/W            | R/W | R/W | R/W | R/W | R/W |

| Address   |             | Information Page Memory 007FH |                |     |     |     |     |     |

| Note: U = | Unchanged b | y Reset. R/W                  | / = Read/Write | Э.  |     |     |     |     |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

# **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit                                             | 7                                 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field                                           | S_NUM                             |     |     |     |     |     |     |     |  |

| RESET                                           | U                                 | U   | U   | U   | U   | U   | U   | U   |  |

| R/W                                             | R/W                               | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address                                         | Information Page Memory 001C-001F |     |     |     |     |     |     |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                   |     |     |     |     |     |     |     |  |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 108 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC Baud Minimum E<br>Rate (bps) Rate (Kb |       |  |  |  |

|---------------------------------|-----------------------------------------|------------------------------------------------------------------|-------|--|--|--|

| 20.0                            | 2500.0                                  | 1,843,200                                                        | 39    |  |  |  |

| 1.0                             | 125.0                                   | 115,200                                                          | 1.95  |  |  |  |

| 0.032768 (32kHz)                | 4.096                                   | 2,400                                                            | 0.064 |  |  |  |

#### Table 108. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

## **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control Register. A

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

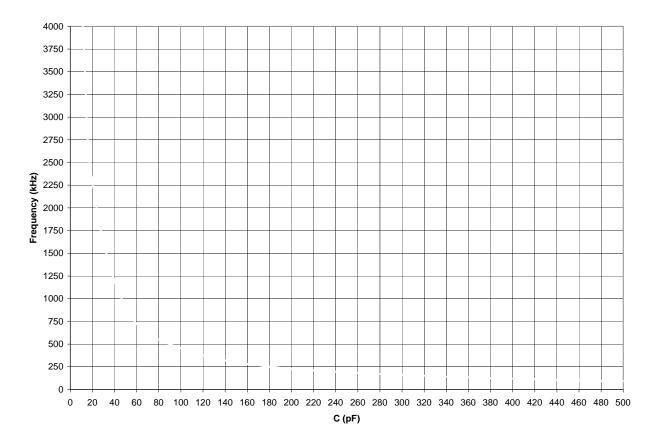

Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45k\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

202

Register file size varies depending on the device type. See the device-specific Z8 Encore! XP Product Specification to determine the exact register file range available.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags and address modes are represented by a notational shorthand that is described in Table 118.

| Notation | Description                    | Operand | Range                                                                                                                         |  |  |  |  |  |

|----------|--------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                              |  |  |  |  |  |

| CC       | Condition code                 | —       | Refer to the Condition Codes section in the <u>eZ8</u><br><u>CPU Core User Manual (UM0128)</u> .                              |  |  |  |  |  |

| DA       | Direct address                 | Addrs   | Represents a number in the range 0000H to FFFFH.                                                                              |  |  |  |  |  |

| ER       | Extended addressing register   | Reg     | Reg. represents a number in the range of 000H to FFFH.                                                                        |  |  |  |  |  |

| IM       | Immediate data                 | #Data   | Data is a number between 00H to FFH.                                                                                          |  |  |  |  |  |

| lr       | Indirect working register      | @Rn     | n = 0–15.                                                                                                                     |  |  |  |  |  |

| IR       | Indirect register              | @Reg    | Reg. represents a number in the range of 00H to FFH.                                                                          |  |  |  |  |  |

| Irr      | Indirect working register pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                             |  |  |  |  |  |

| IRR      | Indirect register pair         | @Reg    | Reg. represents an even number in the range 00H to FEH.                                                                       |  |  |  |  |  |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                     |  |  |  |  |  |

| r        | Working register               | Rn      | n = 0 – 15.                                                                                                                   |  |  |  |  |  |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH.                                                                          |  |  |  |  |  |

| RA       | Relative address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction. |  |  |  |  |  |

| rr       | Working register pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                             |  |  |  |  |  |

| RR       | Register pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                    |  |  |  |  |  |

#### Table 118. Notational Shorthand

|                   |                                       |         | -40°C to +<br>otherwise s |            |       |                                                                                       |  |

|-------------------|---------------------------------------|---------|---------------------------|------------|-------|---------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                             | Minimum | Typical                   | Maximum    | Units | Conditions                                                                            |  |

| V <sub>OH1</sub>  | High Level Output<br>Voltage          | 2.4     | -                         | -          | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.       |  |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage           | _       | -                         | 0.6        | V     | $I_{OL} = 20 \text{ mA}; V_{DD} = 3.3 \text{ V}$<br>High Output Drive enabled.        |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage          | 2.4     | _                         | _          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3V<br>High Output Drive enabled.        |  |

| I <sub>IH</sub>   | Input Leakage Cur-<br>rent            | -       | <u>+</u> 0.002            | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                                |  |

| IIL               | Input Leakage Cur-<br>rent            | -       | <u>+</u> 0.007            | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3V;$                                                 |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current           | -       | -                         | <u>+</u> 5 | μA    |                                                                                       |  |

| I <sub>LED</sub>  | Controlled Current<br>Drive           | 1.8     | 3                         | 4.5        | mA    | $\{AFS2, AFS1\} = \{0, 0\}$                                                           |  |

|                   |                                       | 2.8     | 7                         | 10.5       | mA    | $\{AFS2, AFS1\} = \{0, 1\}$                                                           |  |

|                   |                                       | 7.8     | 13                        | 19.5       | mA    | ${AFS2,AFS1} = {1,0}$                                                                 |  |

|                   |                                       | 12      | 20                        | 30         | mA    | ${AFS2,AFS1} = {1,1}$                                                                 |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -       | 8.0 <sup>2</sup>          | -          | pF    |                                                                                       |  |

| C <sub>XIN</sub>  | XIN Pad Capaci-<br>tance              | -       | 8.0 <sup>2</sup>          | -          | pF    |                                                                                       |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -       | 9.5 <sup>2</sup>          | _          | pF    |                                                                                       |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30      | 100                       | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                         |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD     |                           |            | V     | Voltage at which RAM retains<br>static values; no reading or writ-<br>ing is allowed. |  |

### Table 131. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

| ning (Continued) |  |

|------------------|--|

|                  |  |

#### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

### $V_{DD}$ = 3.0 V to 3.6 V T<sub>A</sub> = 0°C to +70°C (unless otherwise stated)

| Symbol         | Parameter                     | Minimum | Typical | Maximum              | Units                          | Conditions                                                                                                                                                                                                                                |

|----------------|-------------------------------|---------|---------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Continuous Conversion<br>Time | -       | 256     | _                    | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                                   |

|                |                               |         | 512     |                      |                                | Temperature sensor measurement                                                                                                                                                                                                            |

|                | Signal Input Bandwidth        | _       | 10      |                      | kHz                            | As defined by -3 dB point                                                                                                                                                                                                                 |

| R <sub>S</sub> | Analog Source                 | _       | _       | 10                   | kΩ                             | In unbuffered mode                                                                                                                                                                                                                        |

|                | Impedance <sup>4</sup>        |         |         | 500                  | kΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Zin            | Input Impedance               | -       | 150     |                      | kΩ                             | In unbuffered mode at 20MHz <sup>5</sup>                                                                                                                                                                                                  |

|                |                               | 10      | _       |                      | MΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Vin            | Input Voltage Range           | 0       |         | V <sub>DD</sub>      | V                              | Unbuffered Mode                                                                                                                                                                                                                           |

|                |                               | 0.3     |         | V <sub>DD</sub> -1.1 | V                              | Buffered Modes<br>These values define<br>the range over which<br>the ADC performs<br>within spec; exceeding<br>these values does not<br>cause damage or insta-<br>bility; see DC Charac-<br>teristics for absolute<br>pin voltage limits. |

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

# **Ordering Information**

Order your F082A Series products from Zilog using the part numbers shown in Table 148. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                     |                 | <b>40. 20</b> |         |           | 002/       |                     | 163 (               | Jiuei          | ing n      | au                 | ^                   |

|---------------------|-----------------|---------------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Part Number         | Flash           | RAM           | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

| Z8 Encore! XP F082A | <b>A Series</b> | with 8        | (B Flas | sh, 10    | -Bit A     | Analo               | og-to               | Digit          | al Co      | onve               | erter               |

| Standard Temperatu  | re: 0°C t       | to 70°C       |         |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020SG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40°       | 'C to 10      | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EG      | 8KB             | 1KB           | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EG      | 8KB             | 1KB           | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EG      | 8KB             | 1KB           | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

#### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

LD 210 LDC 210 LDCI 209, 210 LDE 210 **LDEI 209** LDX 210 LEA 210 logical 210 **MULT 208 NOP 209** OR 210 **ORX 210 POP 210** POPX 210 program control 211 **PUSH 210** PUSHX 210 RCF 209, 210 **RET 211** RL 211 **RLC 211** rotate and shift 211 RR 211 **RRC 211 SBC 208** SCF 209, 210 SRA 211 SRL 211 **SRP 210 STOP 210 SUB 208 SUBX 208 SWAP 211 TCM 209 TCMX 209** TM 209 TMX 209 **TRAP 211** Watchdog Timer refresh 210 **XOR 210 XORX 210** instructions, eZ8 classes of 207 interrupt control register 69 interrupt controller 55

architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 67 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 211 interrupt vector listing 55 interrupts **UART 108** IR 206 Ir 206 IrDA architecture 120 block diagram 120 control register definitions 123 operation 120 receiving data 122 transmitting data 121 **IRET 211** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 64 IRQ2 enable high and low bit registers 65 **IRR 206** Irr 206

# J

JP 211 jump, conditional, relative, and relative conditional 211

# L

LD 210 LDC 210 LDCI 209, 210 LDE 210 LDEI 209, 210 LDX 210 259

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.