Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             |                                                           |

|----------------------------|-----------------------------------------------------------|

| TToddet Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | <u>.</u>                                                  |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081apb020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Revision History                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                        |

| List of Tables                                                                                                                                                                                         |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview410-Bit Analog-to-Digital Converter4Low-Power Operational Amplifier4Internal Precision Oscillator5Temperature Sensor5  |

| Analog Comparator5External Crystal Oscillator5Low Voltage Detector5On-Chip Debugger5Universal Asynchronous Receiver/Transmitter5Timers5General-Purpose Input/Output6Direct LED Drive6Flash Controller6 |

| Non-Volatile Data Storage       6         Interrupt Controller       6         Reset Controller       6                                                                                                |

| Pin Description8Available Packages8Pin Configurations8Signal Descriptions10Pin Characteristics12                                                                                                       |

| Address Space15Register File15Program Memory15Data Memory17Flash Information Area17                                                                                                                    |

| Register Map                                                                                                                                                                                           |

## **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

## Features

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |

|-------------------------|-------------------------|----------|-------------|------------|

| F85                     | Reserved                | —        | XX          |            |

| <b>Oscillator Contr</b> | ol                      |          |             |            |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |

| F87–F8F                 | Reserved                | _        | XX          |            |

| Comparator 0            |                         |          |             |            |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |

| F91–FBF                 | Reserved                | _        | XX          |            |

| Interrupt Contro        | oller                   |          |             |            |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |

| FC9–FCC                 | Reserved                | —        | XX          |            |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |

| GPIO Port A             |                         |          |             |            |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |

| GPIO Port B             |                         |          |             |            |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |

| GPIO Port C             |                         |          |             |            |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

## LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7    | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|------|-----|-----|-------|---------|-----|-----|-----|

| Field   |      |     |     | LEDLV | LL[7:0] |     |     |     |

| RESET   | 0    | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address | F84H |     |     |       |         |     |     |     |

### Table 33. LED Drive Level Low Register (LEDLVLL)

| Bit           | Description                                                                             |

|---------------|-----------------------------------------------------------------------------------------|

| [7:0]         | LED Level Low Bit                                                                       |

| LEDLVLLx      | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|               | pin.                                                                                    |

|               | 00 = 3mA                                                                                |

|               | 01 = 7 mA                                                                               |

|               | 10 = 13mA                                                                               |

|               | 11 = 20mA                                                                               |

| Note: x indic | cates the specific GPIO port pin number (7–0).                                          |

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7          | 6    | 5   | 4    | 3   | 2   | 1     | 0   |

|---------|------------|------|-----|------|-----|-----|-------|-----|

| Field   | TEN        | TPOL |     | PRES |     |     | TMODE |     |

| RESET   | 0          | 0    | 0   | 0    | 0   | 0   | 0     | 0   |

| R/W     | R/W        | R/W  | R/W | R/W  | R/W | R/W | R/W   | R/W |

| Address | F07H, F0FH |      |     |      |     |     |       |     |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

## Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults and other system-level problems which may place the Z8 Encore! XP F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

## Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequency) |                        |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |

| 000004           | 4                | 400 μs                                                                      | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |

#### Table 58. Watchdog Timer Approximate Time-Out Delays

#### **WDT Reset in Normal Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1. For more information about system reset, see the <u>Reset, Stop Mode</u> <u>Recovery and Low Voltage Detection</u> chapter on page 22.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following WDT time-out in STOP Mode.

## Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. Observe the following steps to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU) with the appropriate time-out value.

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH) with the appropriate time-out value.

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL) with the appropriate time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page; see Tables 100 and 101 on page 173 for details. Loading these values

PRELIMINARY

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>TDRE—Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the Transmit Shift Register is empty and character transmission is finished.<br>0 = Data is currently transmitting.<br>1 = Transmission is complete.                                                                                                                                                                                                    |

| [0]<br>CTS  | <b>CTS</b> Signal When this bit is read it returns the level of the $\overline{\text{CTS}}$ signal. This signal is active Low.                                                                                                                                                                                                                                                                              |

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

| Bit     | 7    | 6      | 5    | 4 | 3   | 2   | 1 | 0 |  |

|---------|------|--------|------|---|-----|-----|---|---|--|

| Field   |      | NEWFRM | MPRX |   |     |     |   |   |  |

| RESET   | 0    | 0      | 0    | 0 | 0   | 0   | 0 | 0 |  |

| R/W     | R    | R      | R    | R | R/W | R/W | R | R |  |

| Address | F44H |        |      |   |     |     |   |   |  |

| Bit           | Description                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                      |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the most recent multiprocessor bit received. Reading from the UART<br>Receive Data Register resets this bit to 0.                                                                                                                                  |

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) Register, shown in Table 67, are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

| Bit     | 7         | 6      | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----------|--------|-----|-----|-----|-----|-----|-----|--|

| Field   | COMP_ADDR |        |     |     |     |     |     |     |  |

| RESET   | 0         | 0      | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W       | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F45H      |        |     |     |     |     |     |     |  |

| Bit     | Deere     | intion |     |     |     |     |     |     |  |

#### Table 69. UART Address Compare Register (U0ADDR)

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

## **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High (UxBRH) and Low Byte (UxBRL) registers, shown in Tables 70 and 71, combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | BRH  |     |     |     |     |     |     |     |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F46H |     |     |     |     |     |     |     |  |

#### Bit Description

| [7:0] | UART Baud Rate High Byte |

|-------|--------------------------|

| BRH   |                          |

#### Table 71. UART Baud Rate Low Byte Register (U0BRL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | BRL  |     |     |     |     |     |     |     |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F47H |     |     |     |     |     |     |     |  |

| Bit          | Description             |

|--------------|-------------------------|

| [7:0]<br>BRL | UART Baud Rate Low Byte |

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |  |  |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|--|--|

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |  |  |

| 625.0                    | N/A                      | N/A                  | N/A          | 625.0                    | N/A                      | N/A                  | N/A          |  |  |

| 250.0                    | 1                        | 223.72               | -10.51       | 250.0                    | N/A                      | N/A                  | N/A          |  |  |

| 115.2                    | 2                        | 111.9                | -2.90        | 115.2                    | 1                        | 115.2                | 0.00         |  |  |

| 57.6                     | 4                        | 55.9                 | -2.90        | 57.6                     | 2                        | 57.6                 | 0.00         |  |  |

| 38.4                     | 6                        | 37.3                 | -2.90        | 38.4                     | 3                        | 38.4                 | 0.00         |  |  |

| 19.2                     | 12                       | 18.6                 | -2.90        | 19.2                     | 6                        | 19.2                 | 0.00         |  |  |

| 9.60                     | 23                       | 9.73                 | 1.32         | 9.60                     | 12                       | 9.60                 | 0.00         |  |  |

| 4.80                     | 47                       | 4.76                 | -0.83        | 4.80                     | 24                       | 4.80                 | 0.00         |  |  |

| 2.40                     | 93                       | 2.41                 | 0.23         | 2.40                     | 48                       | 2.40                 | 0.00         |  |  |

| 1.20                     | 186                      | 1.20                 | 0.23         | 1.20                     | 96                       | 1.20                 | 0.00         |  |  |

| 0.60                     | 373                      | 0.60                 | -0.04        | 0.60                     | 192                      | 0.60                 | 0.00         |  |  |

| 0.30                     | 746                      | 0.30                 | -0.04        | 0.30                     | 384                      | 0.30                 | 0.00         |  |  |

|                          |                          |                      |              |                          |                          |                      |              |  |  |

### Table 72. UART Baud Rates (Continued)

ter with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register, bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector is no longer written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

### **Byte Programming**

Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, available for download on <u>www.zilog.com</u>, for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the Mass Erase or Page Erase commands.

These serial numbers are stored in the Flash information page and are unaffected by mass erasure of the device's Flash memory. See the Reading the Flash Information Page section below and the <u>Serialization Data section on page 173</u> for more details.

#### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page and is unaffected by mass erasure of the device's Flash memory. See Reading the Flash Information Page, below, and the <u>Randomized Lot Identifier section on page 174</u> for more details.

## **Reading the Flash Information Page**

The following code example shows how to read data from the Flash information area.

; get value at info address 60 (FE60h) ldx FPS, #%80 ; enable access to flash info page ld R0, #%FE ld R1, #%60 ldc R2, @RR0 ; R2 now contains the calibration value

## **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

## **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits (Table 86).

| Bit     | 7                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|---------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | TRMADR: Trim Bit Address (00H to 1FH) |     |     |     |     |     |     |     |  |

| RESET   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W                                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | FF6H                                  |     |     |     |     |     |     |     |  |

Table 86. Trim Bit Address Register (TRMADR)

Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction and Execute Instruction commands.

DBG  $\leftarrow$  03H DBG  $\rightarrow$  RuntimeCounter[15:8] DBG  $\rightarrow$  RuntimeCounter[7:0]

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

DBG  $\leftarrow$  04H DBG  $\leftarrow$  OCDCTL[7:0]

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

DBG  $\leftarrow$  05H DBG  $\rightarrow$  OCDCTL[7:0]

**Write Program Counter (06H).** The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control registers are allowed and all other register write data values are discarded.

DBG  $\leftarrow$  08H DBG  $\leftarrow$  {4'h0,Register Address[11:8]} DBG  $\leftarrow$  Register Address[7:0] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-256 data bytes DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

**Step Instruction (10H).** The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

**Stuff Instruction (11H).** The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 11H DBG ← opcode[7:0]

**Execute Instruction (12H).** The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see the <u>Watchdog Timer</u> chapter on page 93).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar nonmaskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which

## General Purpose I/O Port Output Timing

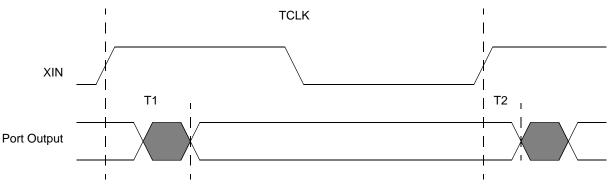

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Delay (ns) |         |  |  |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |  |  |

| GPIO port pins |                                                 |            |         |  |  |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 15      |  |  |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |

#### Table 144. GPIO Port Output Timing

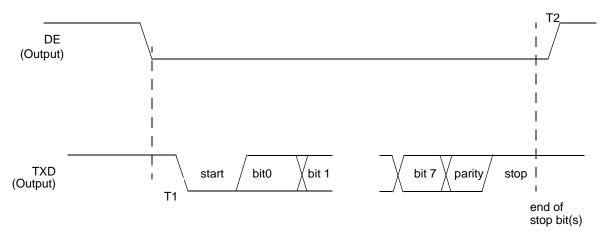

Figure 38 and Table 147 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 147 | UART T | imina Wit | hout CTS |

|-----------|--------|-----------|----------|

|           |        |           |          |

|                |                                                                        | Delay (ns)                 |            |

|----------------|------------------------------------------------------------------------|----------------------------|------------|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |

| UART           |                                                                        |                            |            |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                        |            |

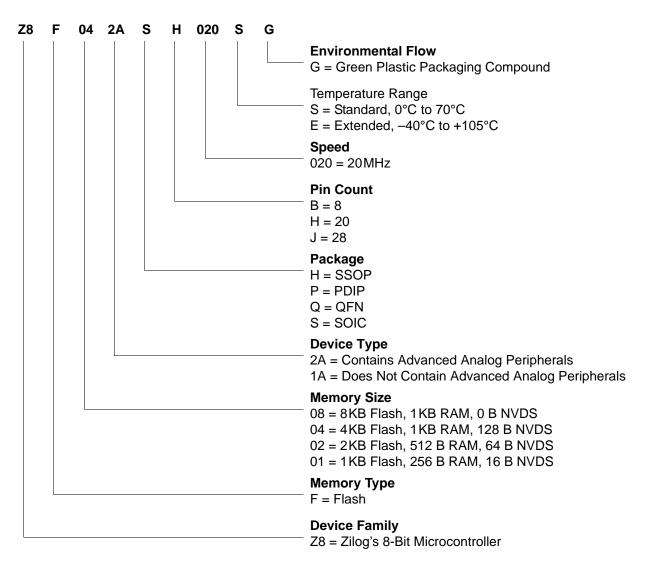

## Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

compare with carry - extended addressing 208 complement 210 complement carry flag 209 condition code 206 continuous conversion (ADC) 127 **CONTINUOUS** mode 87 control register definition, UART 110 Control Registers 15, 18 **COUNTER modes 87** CP 208 **CPC 208 CPCX 208** CPU and peripheral overview 4 CPU control instructions 209 **CPX 208** Customer Feedback Form 265

## D

DA 206, 208 data memory 17 DC characteristics 227 debugger, on-chip 180 **DEC 208** decimal adjust 208 decrement 208 decrement and jump non-zero 211 decrement word 208 **DECW 208** destination operand 207 device, port availability 36 DI 209 direct address 206 disable interrupts 209 DJNZ 211 dst 207

## Ε

EI 209 electrical characteristics 226 ADC 236 flash memory and timing 234 GPIO input data sample timing 240 Watchdog Timer 235, 238 enable interrupt 209 ER 206 extended addressing register 206 external pin reset 26 eZ8 CPU features 4 eZ8 CPU instruction classes 207 eZ8 CPU instruction notation 206 eZ8 CPU instruction set 204 eZ8 CPU instruction summary 212

## F

FCTL register 155, 161, 162 features, Z8 Encore! 1 first opcode map 224 FLAGS 207 flags register 207 flash controller 6 option bit address space 162 option bit configuration - reset 159 program memory address 0000H 162 program memory address 0001H 164 flash memory 146 arrangement 147 byte programming 151 code protection 149 configurations 146 control register definitions 153, 161 controller bypass 152 electrical characteristics and timing 234 flash control register 155, 161, 162 flash option bits 150 flash status register 155 flow chart 148 frequency high and low byte registers 157 mass erase 152 operation 147 operation timing 149 page erase 152 page select register 156, 157 FPS register 156, 157 FSTAT register 155