Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081aph020eg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

The Z8 Encore! XP F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information about physical package specifications, see the <u>Packaging</u> chapter on page 245.

# **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC: 8-, 20- and 28-pin

- PDIP: 8-, 20- and 28-pin

- SSOP: 20- and 28- pin

- QFN 8-pin (MLF-S, a QFN-style package with an 8-pin SOIC footprint)

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A and Z8F011A do not have the advanced analog capability.

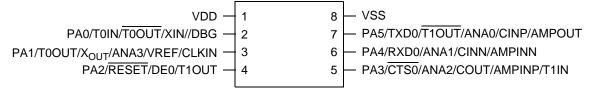

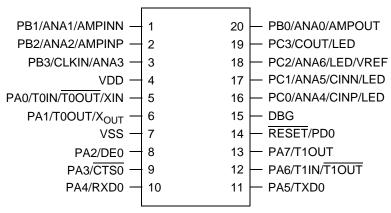

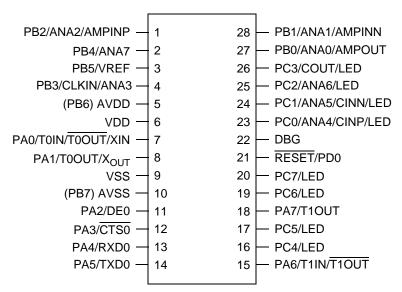

# **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See <u>Table 2</u> on page 10 for a description of the signals. The analog input alternate functions (ANA*x*) are not available on the Z8F081A, Z8F041A, Z8F021A and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the **RESET** alternate function.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                 |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         |                                                                                                                                                                                                                                                                             |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                     |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                             |

| Low-Power Operation | onal Ar | nplifier (LPO)                                                                                                                                                                                                                                                              |

| AMPINP/AMPINN       | I       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                           |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                              |

| Oscillators         |         |                                                                                                                                                                                                                                                                             |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the $X_{OUT}$ pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>    | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                             |

| Clock Input         |         |                                                                                                                                                                                                                                                                             |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                        |

| LED Drivers         |         |                                                                                                                                                                                                                                                                             |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                                                                                |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                             |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                               |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                       |

#### **Table 2. Signal Descriptions (Continued)**

replaced by  $AV_{DD}$  and  $AV_{SS}$ . 2. The  $AV_{DD}$  and  $AV_{SS}$  signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F082A Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see <u>Table 20 on page 46</u>), the <u>RESET</u> pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

STOP Mode is entered by execution of a STOP instruction by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 32 for detailed STOP Mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see <u>Table 135</u> on page 233)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vec-

**Caution:** To avoid retriggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, Zilog recommends that the service routine continues to read from the RSTSTAT Register until the WDT bit is cleared as shown in the following example.

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests.

### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 Register to determine if any interrupt requests are pending.

| Bit     | 7        | 6   | 5   | 4     | 3     | 2        | 1        | 0    |

|---------|----------|-----|-----|-------|-------|----------|----------|------|

| Field   | Reserved | T1I | TOI | U0RXI | U0TXI | Reserved | Reserved | ADCI |

| RESET   | 0        | 0   | 0   | 0     | 0     | 0        | 0        | 0    |

| R/W     | R/W      | R/W | R/W | R/W   | R/W   | R/W      | R/W      | R/W  |

| Address |          |     |     | FC    | 0H    |          |          |      |

| Bit        | Description                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                               |

| [6]<br>T1I | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service. |

| [5]<br>T0I | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from Timer 0 is awaiting service. |

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM SINGLE OUTPUT Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

delay ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode by writing the TMODE bits in the TxCTL1 Register and the TMODEHI bit in TxCTL0 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value xPrescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

111

#### Table 63. UART Control 0 Register (U0CTL0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                      | 6              | 5                            | 4             | 3                              | 2    | 1    | 0    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|---------------|--------------------------------|------|------|------|--|--|

| Field       | TEN                                                                                                                                                                                                                                                                                                                                                    | REN            | CTSE                         | PEN           | PSEL                           | SBRK | STOP | LBEN |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                                      | 0              | 0                            | 0             | 0                              | 0    | 0    | 0    |  |  |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                    | R/W            | R/W                          | R/W           | R/W                            | R/W  | R/W  | R/W  |  |  |

| Address     | F42H                                                                                                                                                                                                                                                                                                                                                   |                |                              |               |                                |      |      |      |  |  |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                            |                |                              |               |                                |      |      |      |  |  |

| [7]<br>TEN  | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is Low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled.                                 |                |                              |               |                                |      |      |      |  |  |

| [6]<br>REN  | Receive EnableThis bit enables or disables the receiver.0 = Receiver disabled.1 = Receiver enabled.                                                                                                                                                                                                                                                    |                |                              |               |                                |      |      |      |  |  |

| [5]<br>CTSE | <b>CTS Enable</b><br>0 = The CTS signal has no effect on the transmitter.<br>1 = The UART recognizes the CTS signal as an enable control from the transmitter.                                                                                                                                                                                         |                |                              |               |                                |      |      |      |  |  |

| [4]<br>PEN  | <ul> <li>Parity Enable</li> <li>This bit enables or disables parity. Even or odd is determined by the PSEL bit.</li> <li>0 = Parity is disabled.</li> <li>1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.</li> </ul>                                                                  |                |                              |               |                                |      |      |      |  |  |

| [3]<br>PSEL |                                                                                                                                                                                                                                                                                                                                                        | arity is trans |                              |               | all received<br>all received o |      |      |      |  |  |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |                |                              |               |                                |      |      |      |  |  |

| [1]<br>STOP |                                                                                                                                                                                                                                                                                                                                                        | nsmitter ser   | ids one stop<br>ids two stop |               |                                |      |      |      |  |  |

| [0]<br>LBEN | Loop Back<br>0 = Normal<br>1 = All trans                                                                                                                                                                                                                                                                                                               | operation.     | is looped ba                 | ack to the re | ceiver.                        |      |      |      |  |  |

148

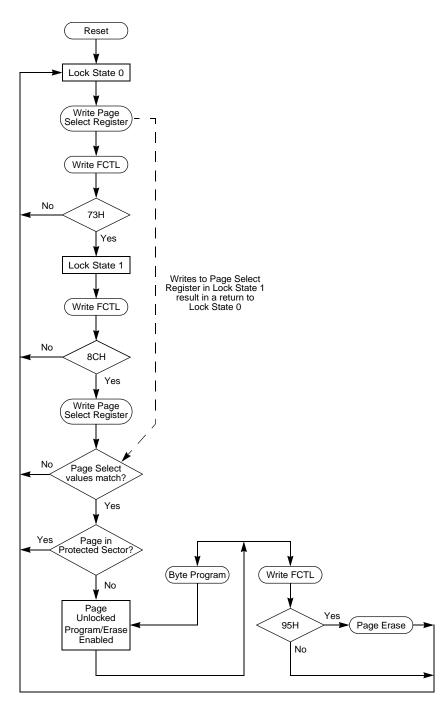

Figure 22 displays a basic Flash Controller flow. The following subsections provide details about the various operations displayed in Figure 22.

Figure 22. Flash Controller Operation Flow Chart

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | FF | 8H |   |   |   |

#### Table 80. Flash Control Register (FCTL)

| Bit Description |

|-----------------|

|-----------------|

[7:0] Flash Command

FCMD 73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access

### Flash Status Register

The Flash Status (FSTAT) Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

#### Table 81. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-------|-------|---|---|---|---|---|--|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |  |

| RESET   | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | R    | R     | R     | R | R | R | R | R |  |

| Address |      | FF8H  |       |   |   |   |   |   |  |

| Bit            | Description                                                                                                                                                                                                                                                                                                     |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [7:6]          | These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                           |  |

| [5:0]<br>FSTAT | Flash Controller Status<br>000000 = Flash Controller locked.<br>000001 = First unlock command received (73H written).<br>000010 = Second unlock command received (8CH written).<br>000011 = Flash Controller unlocked.<br>000100 = Sector protect register selected.<br>001xxx = Program operation in progress. |  |

|                | 010xxx = Page erase operation in progress.<br>100xxx = Mass erase operation in progress.                                                                                                                                                                                                                        |  |

# **Flash Page Select Register**

The Flash Page Select (FPS) Register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

| Bit     | 7       | 6    | 5   | 4   | 3    | 2   | 1   | 0   |  |

|---------|---------|------|-----|-----|------|-----|-----|-----|--|

| Field   | INFO_EN |      |     |     | PAGE |     |     |     |  |

| RESET   | 0       | 0    | 0   | 0   | 0    | 0   | 0   | 0   |  |

| R/W     | R/W     | R/W  | R/W | R/W | R/W  | R/W | R/W | R/W |  |

| Address |         | FF9H |     |     |      |     |     |     |  |

#### Table 82. Flash Page Select Register (FPS)

#### Bit Description

#### [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

| Table 84. | . Flash Frequency | v High Byte | Register | (FFREQH) |

|-----------|-------------------|-------------|----------|----------|

|           |                   |             |          |          |

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   |     |      |     | FFR | EQH |     |     |     |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | FFAH |     |     |     |     |     |     |

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

#### Table 85. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7   | 7 6 5 4 3 2 1 0 |  |    |    |  |  |  |  |  |  |

|---------|-----|-----------------|--|----|----|--|--|--|--|--|--|

| Field   |     | FFREQL          |  |    |    |  |  |  |  |  |  |

| RESET   | 0   |                 |  |    |    |  |  |  |  |  |  |

| R/W     | R/W |                 |  |    |    |  |  |  |  |  |  |

| Address |     |                 |  | FF | BH |  |  |  |  |  |  |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

# **Randomized Lot Identifier**

#### Table 104. Lot Identification Number (RAND\_LOT)

| Bit                                             | 7                                               | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------------------------|-----|-----|------|------|-----|-----|-----|

| Field                                           |                                                 |     |     | RAND | _LOT |     |     |     |

| RESET                                           | U                                               | U   | U   | U    | U    | U   | U   | U   |

| R/W                                             | R/W                                             | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Address                                         | Interspersed throughout Information Page Memory |     |     |      |      |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                                 |     |     |      |      |     |     |     |

# Bit Description [7] Randomized Lot ID RAND\_LOT The randomized lot ID is a 32-byte binary value that changes for each production lot. See Table 105.

#### Table 105. Randomized Lot ID Locations

| Info Page | Memory  |                                               |

|-----------|---------|-----------------------------------------------|

| Address   | Address | Usage                                         |

| 3C        | FE3C    | Randomized Lot ID Byte 31 (most significant). |

| 3D        | FE3D    | Randomized Lot ID Byte 30.                    |

| 3E        | FE3E    | Randomized Lot ID Byte 29.                    |

| 3F        | FE3F    | Randomized Lot ID Byte 28.                    |

| 58        | FE58    | Randomized Lot ID Byte 27.                    |

| 59        | FE59    | Randomized Lot ID Byte 26.                    |

| 5A        | FE5A    | Randomized Lot ID Byte 25.                    |

| 5B        | FE5B    | Randomized Lot ID Byte 24.                    |

| 5C        | FE5C    | Randomized Lot ID Byte 23.                    |

| 5D        | FE5D    | Randomized Lot ID Byte 22.                    |

| 5E        | FE5E    | Randomized Lot ID Byte 21.                    |

| 5F        | FE5F    | Randomized Lot ID Byte 20.                    |

| 61        | FE61    | Randomized Lot ID Byte 19.                    |

| 62        | FE62    | Randomized Lot ID Byte 18.                    |

| 64        | FE64    | Randomized Lot ID Byte 17.                    |

| 65        | FE65    | Randomized Lot ID Byte 16.                    |

| 67        | FE67    | Randomized Lot ID Byte 15.                    |

| 68        | FE68    | Randomized Lot ID Byte 14.                    |

# **Crystal Oscillator**

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

# **Opcode Maps**

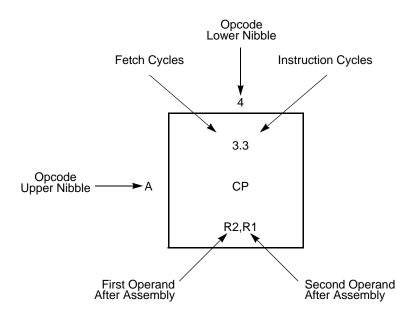

A description of the opcode map data and the abbreviations are provided in Figure 30. Figures 31 and 32 display the eZ8 CPU instructions. Table 129 lists Opcode Map abbreviations.

Figure 30. Opcode Map Cell Description

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F082A Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 130 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C       |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C      |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Table 130. Absolute Maximum Ratings | Table | 130. | Absolute | Maximum | Ratings |

|-------------------------------------|-------|------|----------|---------|---------|

|-------------------------------------|-------|------|----------|---------|---------|

|                                                        |                                                                                                                                                                                                          | V <sub>DD</sub> = 2.7 V to 3.6 V                                                                                                                                                                                    |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                                                                                                         | Conditions                                                                                                                                                                                                                                                                                                                      |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                            | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                            | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                               | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ParameterTypical1Maximum<br>Std Temp2Maximum<br>Ext Temp3ADC Internal Ref-<br>erence Supply Cur-<br>rent000Comparator sup-<br>ply Current150180190Low-Power Opera-<br>tional Amplifier<br>Supply Current355Temperature Sen-<br>sor Supply Current6000Band Gap Supply320480500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

compare with carry - extended addressing 208 complement 210 complement carry flag 209 condition code 206 continuous conversion (ADC) 127 **CONTINUOUS** mode 87 control register definition, UART 110 Control Registers 15, 18 **COUNTER modes 87** CP 208 **CPC 208 CPCX 208** CPU and peripheral overview 4 CPU control instructions 209 **CPX 208** Customer Feedback Form 265

# D

DA 206, 208 data memory 17 DC characteristics 227 debugger, on-chip 180 **DEC 208** decimal adjust 208 decrement 208 decrement and jump non-zero 211 decrement word 208 **DECW 208** destination operand 207 device, port availability 36 DI 209 direct address 206 disable interrupts 209 DJNZ 211 dst 207

# Ε

EI 209 electrical characteristics 226 ADC 236 flash memory and timing 234 GPIO input data sample timing 240 Watchdog Timer 235, 238 enable interrupt 209 ER 206 extended addressing register 206 external pin reset 26 eZ8 CPU features 4 eZ8 CPU instruction classes 207 eZ8 CPU instruction notation 206 eZ8 CPU instruction set 204 eZ8 CPU instruction summary 212

# F

FCTL register 155, 161, 162 features, Z8 Encore! 1 first opcode map 224 FLAGS 207 flags register 207 flash controller 6 option bit address space 162 option bit configuration - reset 159 program memory address 0000H 162 program memory address 0001H 164 flash memory 146 arrangement 147 byte programming 151 code protection 149 configurations 146 control register definitions 153, 161 controller bypass 152 electrical characteristics and timing 234 flash control register 155, 161, 162 flash option bits 150 flash status register 155 flow chart 148 frequency high and low byte registers 157 mass erase 152 operation 147 operation timing 149 page erase 152 page select register 156, 157 FPS register 156, 157 FSTAT register 155

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

260

LEA 210 load 210 load constant 209 load constant to/from program memory 210 load constant with auto-increment addresses 210 load effective address 210 load external data 210 load external data to/from data memory and autoincrement addresses 209 load external to/from data memory and auto-increment addresses 210 load using extended addressing 210 logical AND 210 logical AND/extended addressing 210 logical exclusive OR 210 logical exclusive OR/extended addressing 210 logical instructions 210 logical OR 210 logical OR/extended addressing 210 low power modes 32

# Μ

master interrupt enable 57 memory data 17 program 15 mode **CAPTURE 87, 88 CAPTURE/COMPARE 88** CONTINUOUS 87 COUNTER 87 GATED 88 **ONE-SHOT 87** PWM 87, 88 modes 87 **MULT 208** multiply 208 multiprocessor mode, UART 105

# Ν

NOP (no operation) 209 notation

# 0

b 206

cc 206

DA 206

ER 206

IM 206

IR 206

Ir 206

**IRR 206**

Irr 206

p 206

R 206

r 206

RA 206

**RR 206**

vector 207

notational shorthand 206

rr 206

X 207

OCD architecture 180 auto-baud detector/generator 183 baud rate limits 184 block diagram 180 breakpoints 185 commands 186 control register 191 data format 183 DBG pin to RS-232 Interface 181 debug mode 182 debugger break 211 interface 181 serial errors 184 status register 192 timing 242 OCD commands execute instruction (12H) 190 read data memory (0DH) 190 read OCD control register (05H) 188 read OCD revision (00H) 187 read OCD status register (02H) 187 read program counter (07H) 188