Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081aph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

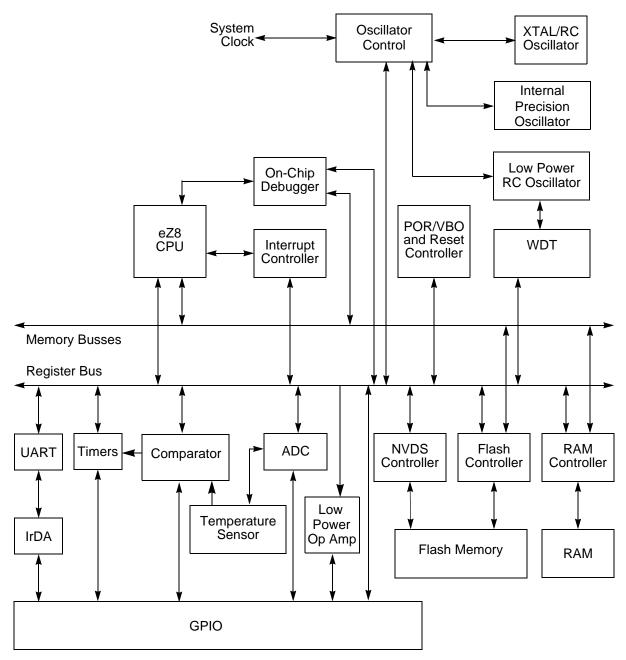

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

### Features

The key features of Z8 Encore! XP F082A Series products include:

- 20MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

## **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP F082A Series devices.

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |  |

|-------------------------|-------------------------|----------|-------------|------------|--|

| F85                     | Reserved                | —        | XX          |            |  |

| <b>Oscillator Contr</b> | ol                      |          |             |            |  |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |  |

| F87–F8F                 | Reserved                | _        | XX          |            |  |

| Comparator 0            |                         |          |             |            |  |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |  |

| F91–FBF                 | Reserved                | _        | XX          |            |  |

| Interrupt Contro        | oller                   |          |             |            |  |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |  |

| FC9–FCC                 | Reserved                | —        | XX          |            |  |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |  |

| GPIO Port A             |                         |          |             |            |  |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |  |

| GPIO Port B             |                         |          |             |            |  |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |  |

| GPIO Port C             |                         |          |             |            |  |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |  |

#### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

# **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Table 9. Reset Sources and Resulting Reset Type |  |

|-------------------------------------------------|--|

| Operating Mode       | Reset Source                                          | Special Conditions                                                                            |  |  |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |  |  |

|                      | Watchdog Timer time-out when configured for Reset     | None.                                                                                         |  |  |

|                      | RESET pin assertion                                   | All reset pulses less than three system cloc in width are ignored.                            |  |  |

|                      | On-Chip Debugger initiated Reset (OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |  |  |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |  |  |

|                      | RESET pin assertion                                   | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |  |  |

|                      | DBG pin driven Low                                    | None.                                                                                         |  |  |

### **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold (VPOR), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage (V<sub>POR</sub>).

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failure to perform this results in STOP Mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                       | 6                                                    | 5            | 4          | 3           | 2            | 1            | 0             |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|------------|-------------|--------------|--------------|---------------|--|

| Field       | LPO                                                                                                                     | Rese                                                 | erved        | VBO        | TEMP        | ADC          | COMP         | Reserved      |  |

| RESET       | 1                                                                                                                       | 0                                                    | 0            | 0          | 0           | 0            | 0            | 0             |  |

| R/W         | R/W                                                                                                                     | R/W                                                  | R/W          | R/W        | R/W         | R/W          | R/W          | R/W           |  |

| Address     |                                                                                                                         |                                                      |              | F8         | ОH          |              | •            | ·             |  |

| Bit         | Description                                                                                                             |                                                      |              |            |             |              |              |               |  |

| [7]<br>LPO  | Low-Power Operational Amplifier Disable<br>0 = LPO is enabled (this applies even in STOP Mode).<br>1 = LPO is disabled. |                                                      |              |            |             |              |              |               |  |

| [6:5]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                |                                                      |              |            |             |              |              |               |  |

| [4]<br>VBO  |                                                                                                                         | nabled.                                              |              |            | both enable | e the VBO fo | or the VBO t | to be active. |  |

| [3]<br>TEMP | 0 = Temper                                                                                                              | ature Sensor I<br>ature Senso<br>ature Senso         | r enabled.   |            |             |              |              |               |  |

| [2]<br>ADC  | 0 = Analog-                                                                                                             | <b>Digital Con</b><br>to-Digital Co<br>to-Digital Co | onverter ena | abled.     |             |              |              |               |  |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                         |                                                      |              |            |             |              |              |               |  |

| [0]         | Reserved<br>This bit is re                                                                                              | eserved and                                          | must be pr   | ogrammed t | o 0.        |              |              |               |  |

#### Table 13. Power Control Register 0 (PWRCTL0)

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit     | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|------|------|-------|-----|------|------|------|------|

| Field   |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H |      |       |     |      |      |      |      |

| Table 37. | Interrupt | Request 2 | Register | (IRQ2) |

|-----------|-----------|-----------|----------|--------|

|-----------|-----------|-----------|----------|--------|

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [7:4]   | Reserved                                                             |  |

|         | These bits are reserved and must be programmed to 0000.              |  |

| [3:0]   | Port C Pin <i>x</i> Interrupt Request                                |  |

| PCxI    | 0 = No interrupt request is pending for GPIO Port C pin $x$ .        |  |

|         | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: x | c indicates the specific GPIO Port C pin number (0–3).               |  |

### **IRQ0 Enable High and Low Bit Registers**

Table 38 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register.

| IRQ0ENH[x]                           | IRQ0ENL[x] | Priority | Description |  |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |  |  |

Table 38. IRQ0 Enable and Priority Encoding

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer Reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer Reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of Timer Input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

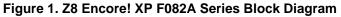

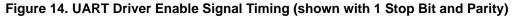

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, plus the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable-to-Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

111

#### Table 63. UART Control 0 Register (U0CTL0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                      | 5                                    | 4      | 3                               | 2              | 1                         | 0          |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------|---------------------------------|----------------|---------------------------|------------|--|--|

| Field       | TEN                                                                                                                                                                                                                                                                                                                                                    | REN                                                                                                                                                                                                                                                                                                                    | CTSE                                 | PEN    | PSEL                            | SBRK           | STOP                      | LBEN       |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                      | 0                                    | 0      | 0                               | 0              | 0                         | 0          |  |  |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                    | R/W                                  | R/W    | R/W                             | R/W            | R/W                       | R/W        |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                        |                                      | F4     | 2H                              |                |                           |            |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                             | n                                                                                                                                                                                                                                                                                                                      |                                      |        |                                 |                |                           |            |  |  |

| [7]<br>TEN  | Transmit E<br>This bit ena<br>and the CT<br>0 = Transm                                                                                                                                                                                                                                                                                                 | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is Low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled. |                                      |        |                                 |                |                           |            |  |  |

| [6]<br>REN  | Receive Er<br>This bit ena<br>0 = Receive<br>1 = Receive                                                                                                                                                                                                                                                                                               | ables or disa<br>er disabled.                                                                                                                                                                                                                                                                                          | bles the rec                         | eiver. |                                 |                |                           |            |  |  |

| [5]<br>CTSE |                                                                                                                                                                                                                                                                                                                                                        | S signal has                                                                                                                                                                                                                                                                                                           | s no eff <u>ect o</u><br>zes the CTS |        |                                 | ntrol from the | e transmitter             |            |  |  |

| [4]<br>PEN  | 0 = Parity is                                                                                                                                                                                                                                                                                                                                          | ibles or disa<br>s disabled.<br>nsmitter ser                                                                                                                                                                                                                                                                           |                                      |        | is determine<br>al parity bit a |                | SEL bit.<br>eiver receive | s an addi- |  |  |

| [3]<br>PSEL |                                                                                                                                                                                                                                                                                                                                                        | arity is trans                                                                                                                                                                                                                                                                                                         |                                      |        | all received<br>all received o  |                |                           |            |  |  |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |                                                                                                                                                                                                                                                                                                                        |                                      |        |                                 |                |                           |            |  |  |

| [1]<br>STOP |                                                                                                                                                                                                                                                                                                                                                        | nsmitter ser                                                                                                                                                                                                                                                                                                           | ids one stop<br>ids two stop         |        |                                 |                |                           |            |  |  |

| [0]<br>LBEN | 0 = Normal                                                                                                                                                                                                                                                                                                                                             | <ul> <li>1 = The transmitter sends two stop bits.</li> <li>Loop Back Enable</li> <li>0 = Normal operation.</li> <li>1 = All transmitted data is looped back to the receiver.</li> </ul>                                                                                                                                |                                      |        |                                 |                |                           |            |  |  |

### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers, shown in Tables 65 and 66, identify the current UART operating configuration and status.

| Table 65. | UART | Status 0 | Register | (U0STAT0) |

|-----------|------|----------|----------|-----------|

|-----------|------|----------|----------|-----------|

| Bit         | 7                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                        | 5  | 4  | 3    | 2    | 1   | 0   |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|------|------|-----|-----|--|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                            | PE                                                                                                                                                                                                                                                                       | OE | FE | BRKD | TDRE | TXE | CTS |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                        | 0  | 0  | 0    | 1    | 1   | Х   |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                              | R                                                                                                                                                                                                                                                                        | R  | R  | R    | R    | R   | R   |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                          |    | F4 | 1H   |      |     |     |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                     | n                                                                                                                                                                                                                                                                        |    |    |      |      |     |     |  |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                                                      | Receive Data Available<br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register. |    |    |      |      |     |     |  |  |

| [6]<br>PE   | <ul> <li>Parity Error</li> <li>This bit indicates that a parity error has occurred. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No parity error has occurred.</li> <li>1 = A parity error has occurred.</li> </ul>                                                                                                    |                                                                                                                                                                                                                                                                          |    |    |      |      |     |     |  |  |

| [5]<br>OE   | Overrun Error<br>This bit indicates that an overrun error has occurred. An overrun occurs when new data is<br>received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0,<br>reading the UART Receive Data Register clears this bit.<br>0 = No overrun error occurred.<br>1 = An overrun error occurred.      |                                                                                                                                                                                                                                                                          |    |    |      |      |     |     |  |  |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                                    |                                                                                                                                                                                                                                                                          |    |    |      |      |     |     |  |  |

| [3]<br>BRKD | <ul> <li>1 = A framing error occurred.</li> <li>Break Detect</li> <li>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No break occurred.</li> <li>1 = A break occurred.</li> </ul> |                                                                                                                                                                                                                                                                          |    |    |      |      |     |     |  |  |

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>TDRE—Transmitter Data Register Empty</li> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the Transmit Shift Register is empty and character transmission is finished.<br>0 = Data is currently transmitting.<br>1 = Transmission is complete.                                                                                                                                                                                                    |

| [0]<br>CTS  | <b>CTS</b> Signal When this bit is read it returns the level of the $\overline{\text{CTS}}$ signal. This signal is active Low.                                                                                                                                                                                                                                                                              |

### **UART Status 1 Register**

This register contains multiprocessor control and status bits.

| Bit     | 7    | 6      | 5    | 4 | 3   | 2   | 1 | 0 |  |  |

|---------|------|--------|------|---|-----|-----|---|---|--|--|

| Field   |      | NEWFRM | MPRX |   |     |     |   |   |  |  |

| RESET   | 0    | 0      | 0    | 0 | 0   | 0   | 0 | 0 |  |  |

| R/W     | R    | R      | R    | R | R/W | R/W | R | R |  |  |

| Address | F44H |        |      |   |     |     |   |   |  |  |

| Bit           | Description                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                      |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the most recent multiprocessor bit received. Reading from the UART<br>Receive Data Register resets this bit to 0.                                                                                                                                  |

### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) Register, shown in Table 67, are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                        | 6                                                                                                                                                              | 5   | 4           | 3           | 2 1     |              | 0   |  |  |              |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|---------|--------------|-----|--|--|--------------|--|--|--|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REFSELH                  | SELH Reserved                                                                                                                                                  |     |             |             |         | BUFMODE[2:0] |     |  |  | BUFMODE[2:0] |  |  |  |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                        | 0                                                                                                                                                              | 0   | 0           | 0           | 0       | 0            | 0   |  |  |              |  |  |  |  |  |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W                      | R/W                                                                                                                                                            | R/W | R/W         | R/W         | R/W     | R/W          | R/W |  |  |              |  |  |  |  |  |

| Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |                                                                                                                                                                |     | F7          | 1H          |         |              |     |  |  |              |  |  |  |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description              |                                                                                                                                                                |     |             |             |         |              |     |  |  |              |  |  |  |  |  |

| <ul> <li>[7] Voltage Reference Level Select High Bit</li> <li>REFSELH In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this de the level of the internal voltage reference; the following details the effects of {R REFSELL}; this reference is independent of the Comparator reference.</li> <li>00= Internal Reference Disabled, reference comes from external pin.</li> <li>01= Internal Reference set to 1.0V.</li> <li>10= Internal Reference set to 2.0V (default).</li> <li>11= Reserved.</li> </ul> |                          |                                                                                                                                                                |     |             |             |         |              |     |  |  |              |  |  |  |  |  |

| [6:3] <b>Reserved</b><br>These bits are reserved ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |                                                                                                                                                                |     | must be pro | ogrammed to | o 0000. |              |     |  |  |              |  |  |  |  |  |

| [2:0]<br>BUFMODI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E[2:0] 000<br>001<br>010 | Input Buffer Mode Select<br>000 = Single-ended, unbuffered input.<br>001 = Single-ended, buffered input with unity gain.<br>010 = Reserved.<br>011 = Reserved. |     |             |             |         |              |     |  |  |              |  |  |  |  |  |

#### Table 74. ADC Control/Status Register 1 (ADCCTL1)

100 = Differential, unbuffered input.101 = Differential, buffered input with unity gain.

110 = Reserved. 111 = Reserved.

### ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) Register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

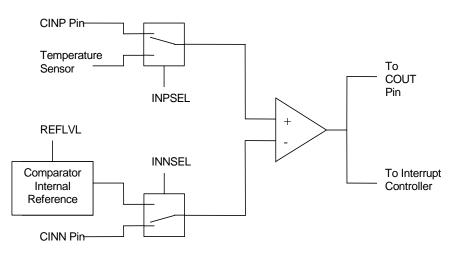

# **Comparator**

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

## Operation

This section describes the interface and modes of operation of the On-Chip Debugger.

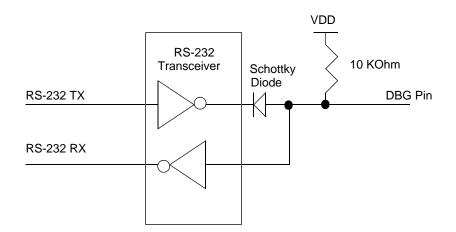

### **OCD** Interface

The on-chip debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional, open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP F082A Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 24 and Figure 25. The recommended method is the buffered implementation displayed in Figure 25. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details about the pull-up current, see the <u>Electrical Characteristics</u> chapter on page 226). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

**Caution:** For operation of the on-chip debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and may require an external pull-up resistor to ensure proper operation.

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #1 of 2

### **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

#### Table 111. OCD Status Register (OCDSTAT)

| Bit   | 7   | 6    | 5      | 4        | 0 |   |   |   |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|

| Field | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |

| Bit           | Description                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                    |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                                |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled, that allows disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be programmed to 00000.                                                                   |

the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry and all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

# **Oscillator Control Register Definitions**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Unlock the Oscillator Control Register by writing the two-step sequence E7H followed by 18H. The register is locked at successful completion of a register write to the OSCCTL.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2           | 1 | 0 |  |  |

|---------|-------|-------|-------|-------|-------|-------------|---|---|--|--|

| Field   | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL      |   |   |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0 0 0       |   |   |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W R/W R/V |   |   |  |  |

| Address | F86H  |       |       |       |       |             |   |   |  |  |

Table 113. Oscillator Control Register (OSCCTL)

| Bit          | Description                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                             |

| [6]<br>XTLEN | Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled.                            |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                         |

| [4]<br>SOFEN | System Clock Oscillator Failure Detection Enable1 = Failure detection and recovery of system clock oscillator is enabled.0 = Failure detection and recovery of system clock oscillator is disabled. |

| 24 | 0 |

|----|---|

| 21 | Ö |

| Assembly     |                                                                          |     | lress<br>ode | _ Opcode(s) |     |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|--------------------------------------------------------------------------|-----|--------------|-------------|-----|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                       | dst | src          | (Hex)       |     | Ζ | S   | V   | D | Н | s              | S               |

| ORX dst, src | $dst \gets dst \ OR \ src$                                               | ER  | ER           | 48          | -   | * | *   | 0   | - | - | 4              | 3               |

|              |                                                                          | ER  | IM           | 49          | -   |   |     |     |   |   | 4              | 3               |

| POP dst      | dst ← @SP                                                                | R   |              | 50          | -   | _ | -   | -   | - | - | 2              | 2               |

|              | $SP \leftarrow SP + 1$                                                   | IR  |              | 51          | -   |   |     |     |   |   | 2              | 3               |

| POPX dst     | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER  |              | D8          | -   | _ | -   | _   | _ | - | 3              | 2               |

| PUSH src     | $SP \leftarrow SP - 1$                                                   | R   |              | 70          | -   | - | _   | -   | - | - | 2              | 2               |

|              | @SP ← src                                                                | IR  |              | 71          |     |   |     |     |   |   | 2              | 3               |

|              |                                                                          | IM  |              | IF70        |     |   |     |     |   |   | 3              | 2               |

| PUSHX src    | $SP \leftarrow SP - 1$<br>@ $SP \leftarrow src$                          | ER  |              | C8          | _   | - | _   | -   | - | _ | 3              | 2               |

| RCF          | C ← 0                                                                    |     |              | CF          | 0   | _ | _   | _   | _ | - | 1              | 2               |

| RET          | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |              | AF          | _   | - | _   | _   | _ | _ | 1              | 4               |

| RL dst       |                                                                          | R   |              | 90          | *   | * | *   | *   | _ | _ | 2              | 2               |

|              | C D7D6D5D4D3D2D1D0                                                       | IR  |              | 91          | _   |   |     |     |   |   | 2              | 3               |

| RLC dst      |                                                                          | R   |              | 10          | * * | * | *   | _   | _ | 2 | 2              |                 |

|              | C - D7D6D5D4D3D2D1D0 - dst                                               | IR  |              | 11          | -   |   |     |     |   |   | 2              | 3               |

| RR dst       |                                                                          | R   |              | E0          | *   | * | *   | *   | _ | _ | 2              | 2               |

|              | ► D7 D6 D5 D4 D3 D2 D1 D0 C<br>dst                                       | IR  |              | E1          |     |   |     |     |   |   | 2              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

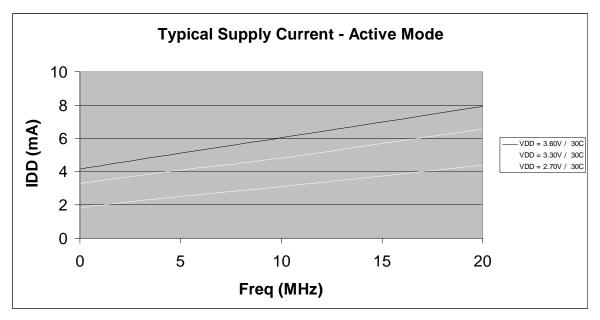

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode  $I_{\text{DD}}$  Versus System Clock Frequency

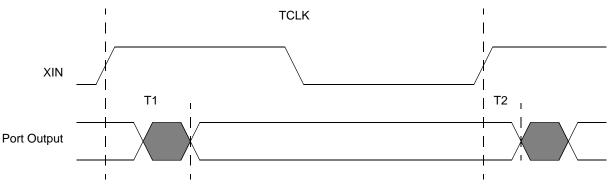

### General Purpose I/O Port Output Timing

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Delay (ns) |         |

|----------------|-------------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |

| GPIO port pi   | ns                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |

#### Table 144. GPIO Port Output Timing