Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081asb020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 15

## **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral and general-purpose I/O port control registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more information about eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

### **Register File**

The Register File address space in the Z8 Encore! MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore!  $XP^{TM}$  F082A Series devices contain 256 B to 1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

### **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

### **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]                           | IRQ1ENL[x] | Priority | Description |  |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |  |  |

#### Table 41. IRQ1 Enable and Priority Encoding

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7          | 6                   | 5   | 4   | 3   | 2     | 1   | 0   |  |

|---------|------------|---------------------|-----|-----|-----|-------|-----|-----|--|

| Field   | TEN        | TEN TPOL PRES TMODE |     |     |     |       |     |     |  |

| RESET   | 0          | 0                   | 0   | 0   | 0   | 0 0 0 |     |     |  |

| R/W     | R/W        | R/W                 | R/W | R/W | R/W | R/W   | R/W | R/W |  |

| Address | F07H, F0FH |                     |     |     |     |       |     |     |  |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

111

#### Table 63. UART Control 0 Register (U0CTL0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                      | 5                                    | 4             | 3                               | 2              | 1                         | 0          |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|---------------------------------|----------------|---------------------------|------------|--|--|

| Field       | TEN                                                                                                                                                                                                                                                                                                                                                    | REN                                                                                                                                                                                                                                                                                                                    | CTSE                                 | PEN           | PSEL                            | SBRK           | STOP                      | LBEN       |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                      | 0                                    | 0             | 0                               | 0              | 0                         | 0          |  |  |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                    | R/W                                  | R/W           | R/W                             | R/W            | R/W                       | R/W        |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                        |                                      | F4            | 2H                              |                |                           |            |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                             | n                                                                                                                                                                                                                                                                                                                      |                                      |               |                                 |                |                           |            |  |  |

| [7]<br>TEN  | Transmit E<br>This bit ena<br>and the CT<br>0 = Transm                                                                                                                                                                                                                                                                                                 | <b>Transmit Enable</b><br>This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal and the CTSE bit. If the $\overline{\text{CTS}}$ signal is Low and the CTSE bit is 1, the transmitter is enabled.<br>0 = Transmitter disabled.<br>1 = Transmitter enabled. |                                      |               |                                 |                |                           |            |  |  |

| [6]<br>REN  | <b>Receive Er</b><br>This bit ena<br>0 = Receive<br>1 = Receive                                                                                                                                                                                                                                                                                        | ables or disa<br>er disabled.                                                                                                                                                                                                                                                                                          | bles the rec                         | eiver.        |                                 |                |                           |            |  |  |

| [5]<br>CTSE |                                                                                                                                                                                                                                                                                                                                                        | S signal has                                                                                                                                                                                                                                                                                                           | s no eff <u>ect o</u><br>zes the CTS |               |                                 | ntrol from the | e transmitter             |            |  |  |

| [4]<br>PEN  | 0 = Parity is                                                                                                                                                                                                                                                                                                                                          | ibles or disa<br>s disabled.<br>nsmitter ser                                                                                                                                                                                                                                                                           |                                      |               | is determine<br>al parity bit a |                | SEL bit.<br>eiver receive | s an addi- |  |  |

| [3]<br>PSEL |                                                                                                                                                                                                                                                                                                                                                        | arity is trans                                                                                                                                                                                                                                                                                                         |                                      |               | all received<br>all received o  |                |                           |            |  |  |

| [2]<br>SBRK | <ul> <li>Send Break</li> <li>This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.</li> <li>0 = No break is sent.</li> <li>1 = Forces a break condition by setting the output of the transmitter to zero.</li> </ul> |                                                                                                                                                                                                                                                                                                                        |                                      |               |                                 |                |                           |            |  |  |

| [1]<br>STOP |                                                                                                                                                                                                                                                                                                                                                        | nsmitter ser                                                                                                                                                                                                                                                                                                           | ids one stop<br>ids two stop         |               |                                 |                |                           |            |  |  |

| [0]<br>LBEN | Loop Back<br>0 = Normal<br>1 = All trans                                                                                                                                                                                                                                                                                                               | operation.                                                                                                                                                                                                                                                                                                             | is looped ba                         | ack to the re | ceiver.                         |                |                           |            |  |  |

| Bit                  | 7    | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------------|------|-----------------|---|---|---|---|---|---|--|--|

| Field                | TXD  |                 |   |   |   |   |   |   |  |  |

| RESET                | Х    | X X X X X X X X |   |   |   |   |   |   |  |  |

| R/W                  | W    | W               | W | W | W | W | W | W |  |  |

| Address              | F40H |                 |   |   |   |   |   |   |  |  |

| Note: X = Undefined. |      |                 |   |   |   |   |   |   |  |  |

#### Table 67. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68 | . UART | Receive | Data | Register | (U0RXD) |

|----------|--------|---------|------|----------|---------|

|----------|--------|---------|------|----------|---------|

| Bit                  | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------------|------------|---|---|---|---|---|---|---|--|--|

| Field                | RXD        |   |   |   |   |   |   |   |  |  |

| RESET                | Х          | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W                  | R          | R | R | R | R | R | R | R |  |  |

| Address              | F40H       |   |   |   |   |   |   |   |  |  |

| Note: X = Undefined. |            |   |   |   |   |   |   |   |  |  |

| Bit                  | Descriptio | n |   |   |   |   |   |   |  |  |

| Dit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

### **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

#### **Output Data**

The output format of the corrected ADC value is shown below.

| MSB |   |   |   |   |   |   |   |   |   | Г | SB |   |   |   |   |

|-----|---|---|---|---|---|---|---|---|---|---|----|---|---|---|---|

| S   | v | b | а | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 | _ | - |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary flag. For a normal (nonoverflow) sample, the sign and the overflow bit match. If the sign bit and overflow bit do not match, a computational overflow has occurred.

### **Input Buffer Stage**

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See <u>Table 139</u> on page 236 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

### **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register 0 (ADCCTL0): see page 134

ADC Control/Status Register 1 (ADCCTL1): see page 136

ADC Data High Byte Register (ADCD\_H): see page 137

ADC Data Low Byte Register (ADCD L): see page 137

### Watchdog Timer Calibration Data

#### Table 100. Watchdog Calibration High Byte at 007EH (WDTCALH)

| Bit       | 7                             | 6           | 5             | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------|-------------|---------------|-----|-----|-----|-----|-----|--|--|--|

| Field     | WDTCALH                       |             |               |     |     |     |     |     |  |  |  |

| RESET     |                               |             |               |     |     |     |     |     |  |  |  |

| R/W       | R/W                           | R/W         | R/W           | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 007EH |             |               |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged h                   | w Reset R/M | / = Read/Writ | e.  |     |     |     |     |  |  |  |

Note: U = Unchanged by Reset. R/W = Read/Write.

#### Bit Description

[7:0] Watchdog Timer Calibration High Byte

WDTCALH

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second time-out at room temperature and 3.3V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-CALH and WDTL with WDTCALL.

| Debug Command           | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter   | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter    | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control Register. |

| Read Register           | 09H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory    | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory     | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory       | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory        | 0DH             | _                                     | _                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     |                                                                                                                                                                           |

| Reserved                | 0FH             | _                                     | _                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled.                                                                                                                                                                 |

| Stuff Instruction       | 11H             | _                                     | Disabled.                                                                                                                                                                 |

| Execute Instruction     | 12H             | _                                     | Disabled.                                                                                                                                                                 |

| Reserved                | 13H–FFH         | _                                     | -                                                                                                                                                                         |

#### Table 109. Debug Command Enable/Disable (Continued)

In the list of OCD commands that follows, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

DBG  $\leftarrow$  02H DBG  $\rightarrow$  OCDSTAT[7:0]

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory,

in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

### **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP F082A Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

| Bit   | 7       | 6     | 5      | 4 | 3        | 1 | 0 |     |  |  |  |  |

|-------|---------|-------|--------|---|----------|---|---|-----|--|--|--|--|

| Field | DBGMODE | BRKEN | DBGACK |   | Reserved |   |   |     |  |  |  |  |

| RESET | 0       | 0     | 0      | 0 | 0 0 0 0  |   |   |     |  |  |  |  |

| R/W   | R/W     | R/W   | R/W    | R | R        | R | R | R/W |  |  |  |  |

Table 110. OCD Control Register (OCDCTL)

#### Bit Description

#### [7] **DEBUG Mode** DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0. 0 = The Z8 Encore! XP F082A Series device is operating in NORMAL Mode. 1 = The Z8 Encore! XP F082A Series device is in DEBUG Mode. [6] **Breakpoint Enable** BRKEN This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL Register is automatically set to 1. 0 = Breakpoints are disabled. 1 = Breakpoints are enabled.

the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry and all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

### **Oscillator Control Register Definitions**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Unlock the Oscillator Control Register by writing the two-step sequence E7H followed by 18H. The register is locked at successful completion of a register write to the OSCCTL.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2           | 0 |  |  |  |

|---------|-------|-------|-------|-------|-------|-------------|---|--|--|--|

| Field   | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL      |   |  |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0 0 0       |   |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W R/W R/W |   |  |  |  |

| Address |       |       |       | F8    | 6H    | · · ·       |   |  |  |  |

Table 113. Oscillator Control Register (OSCCTL)

| Bit          | Description                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                             |

| [6]<br>XTLEN | Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled.                            |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                         |

| [4]<br>SOFEN | System Clock Oscillator Failure Detection Enable1 = Failure detection and recovery of system clock oscillator is enabled.0 = Failure detection and recovery of system clock oscillator is disabled. |

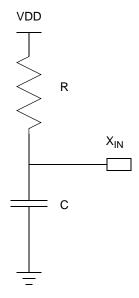

### **Oscillator Operation with an External RC Network**

Figure 28 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

#### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45 \text{ k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$

Figure 29 displays the typical  $(3.3 \text{ V} \text{ and } 25^{\circ}\text{C})$  oscillator frequency as a function of the capacitor (C, in pF) employed in the RC network assuming a  $45 \text{ K}\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended.

#### Table 123. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

#### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | SIC         | Push using Extended Addressing                                          |

#### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

### eZ8 CPU Instruction Summary

Table 128 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch and the number of CPU clock cycles required for the instruction.

| Assembly      |                            |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|----------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation         | dst | src         | • • • •     | С | Ζ | S   | V   | D | Н | S              | S               |

| ADC dst, src  | $dst \gets dst + src + C$  | r   | r           | 12          | * | * | *   | *   | 0 | * | 2              | 3               |

|               |                            | r   | lr          | 13          | - |   |     |     |   |   | 2              | 4               |

|               |                            | R   | R           | 14          | - |   |     |     |   |   | 3              | 3               |

|               |                            | R   | IR          | 15          | - |   |     |     |   |   | 3              | 4               |

|               |                            | R   | IM          | 16          |   |   |     |     |   |   | 3              | 3               |

|               |                            | IR  | IM          | 17          |   |   |     |     |   |   | 3              | 4               |

| ADCX dst, src | $dst \gets dst + src + C$  | ER  | ER          | 18          | * | * | *   | *   | 0 | * | 4              | 3               |

|               |                            | ER  | IM          | 19          |   |   |     |     |   |   | 4              | 3               |

| ADD dst, src  | $dst \leftarrow dst + src$ | r   | r           | 02          | * | * | *   | *   | 0 | * | 2              | 3               |

|               |                            | r   | lr          | 03          | - |   |     |     |   |   | 2              | 4               |

|               |                            | R   | R           | 04          | - |   |     |     |   |   | 3              | 3               |

|               |                            | R   | IR          | 05          | - |   |     |     |   |   | 3              | 4               |

|               |                            | R   | IM          | 06          | - |   |     |     |   |   | 3              | 3               |

|               |                            | IR  | IM          | 07          | - |   |     |     |   |   | 3              | 4               |

| ADDX dst, src | $dst \gets dst + src$      | ER  | ER          | 08          | * | * | *   | *   | 0 | * | 4              | 3               |

|               |                            | ER  | IM          | 09          | - |   |     |     |   |   | 4              | 3               |

#### Table 128. eZ8 CPU Instruction Summary

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

214

| Assembly      |                                          | Address<br>Mode |     | _ Opcode(s) | Flags  |   |   |   |   | Fetch      | Instr.     |   |

|---------------|------------------------------------------|-----------------|-----|-------------|--------|---|---|---|---|------------|------------|---|

| Mnemonic      | Symbolic Operation                       | dst             | src | (Hex)       | CZSVDH |   |   |   |   | Cycle<br>s | Cycle<br>s |   |

| CALL dst      | $SP \leftarrow SP - 2$                   | IRR             |     | D4          | _      | _ | - | - | - | _          | 2          | 6 |

|               | $@SP \leftarrow PC \\ PC \leftarrow dst$ | DA              |     | D6          | -      |   |   |   |   |            | 3          | 3 |

| CCF           | $C \leftarrow \sim C$                    |                 |     | EF          | *      | - | _ | - | - |            | 1          | 2 |

| CLR dst       | dst ← 00H                                | R               |     | B0          | _      | _ | _ | _ | _ | _          | 2          | 2 |

|               |                                          | IR              |     | B1          | -      |   |   |   |   |            | 2          | 3 |

| COM dst       | $dst \leftarrow \sim dst$                | R               |     | 60          | _      | * | * | 0 | _ | _          | 2          | 2 |

|               |                                          | IR              |     | 61          | -      |   |   |   |   |            | 2          | 3 |

| CP dst, src   | dst - src                                | r               | r   | A2          | *      | * | * | * | _ | _          | 2          | 3 |

|               |                                          | r               | Ir  | A3          | -      |   |   |   |   |            | 2          | 4 |

|               |                                          | R               | R   | A4          | -      |   |   |   |   |            | 3          | 3 |

|               |                                          | R               | IR  | A5          | -      |   |   |   |   |            | 3          | 4 |

|               |                                          | R               | IM  | A6          | -      |   |   |   |   |            | 3          | 3 |

|               |                                          | IR              | IM  | A7          | -      |   |   |   |   |            | 3          | 4 |

| CPC dst, src  | dst - src - C                            | r               | r   | 1F A2       | *      | * | * | * | _ | _          | 3          | 3 |

|               |                                          | r               | Ir  | 1F A3       | -      |   |   |   |   |            | 3          | 4 |

|               |                                          | R               | R   | 1F A4       | -      |   |   |   |   |            | 4          | 3 |

|               |                                          | R               | IR  | 1F A5       | -      |   |   |   |   |            | 4          | 4 |

|               |                                          | R               | IM  | 1F A6       | -      |   |   |   |   |            | 4          | 3 |

|               |                                          | IR              | IM  | 1F A7       | -      |   |   |   |   |            | 4          | 4 |

| CPCX dst, src | dst - src - C                            | ER              | ER  | 1F A8       | *      | * | * | * | _ | _          | 5          | 3 |

|               |                                          | ER              | IM  | 1F A9       | -      |   |   |   |   |            | 5          | 3 |

| CPX dst, src  | dst - src                                | ER              | ER  | A8          | *      | * | * | * | _ | _          | 4          | 3 |

|               |                                          | ER              | IM  | A9          | -      |   |   |   |   |            | 4          | 3 |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F082A Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

### **Absolute Maximum Ratings**

Stresses greater than those listed in Table 130 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C       |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C      |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Table 130. Absolute Maximum Ratings | Table | 130. | Absolute | Maximum | Ratings |

|-------------------------------------|-------|------|----------|---------|---------|

|-------------------------------------|-------|------|----------|---------|---------|

| Part Number                               | Flash | RAM | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|-------------------------------------------|-------|-----|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A Series with 8KB Flash |       |     |      |           |            |                     |                     |                |            |                    |                     |

| Standard Temperatu                        |       |     |      |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C      |       |     |      |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EG                            | 8KB   | 1KB | 0    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EG                            | 8KB   | 1KB | 0    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EG                            | 8KB   | 1KB | 0    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

#### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

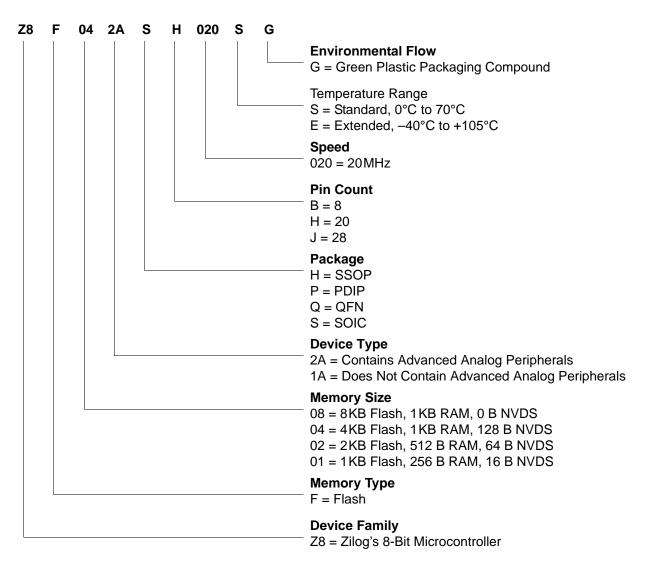

### Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

LD 210 LDC 210 LDCI 209, 210 LDE 210 **LDEI 209** LDX 210 LEA 210 logical 210 **MULT 208 NOP 209** OR 210 **ORX 210 POP 210** POPX 210 program control 211 **PUSH 210** PUSHX 210 RCF 209, 210 **RET 211** RL 211 **RLC 211** rotate and shift 211 RR 211 **RRC 211 SBC 208** SCF 209, 210 SRA 211 SRL 211 **SRP 210 STOP 210 SUB 208 SUBX 208 SWAP 211 TCM 209 TCMX 209** TM 209 TMX 209 **TRAP 211** Watchdog Timer refresh 210 **XOR 210 XORX 210** instructions, eZ8 classes of 207 interrupt control register 69 interrupt controller 55

architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 67 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 211 interrupt vector listing 55 interrupts **UART 108** IR 206 Ir 206 IrDA architecture 120 block diagram 120 control register definitions 123 operation 120 receiving data 122 transmitting data 121 **IRET 211** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 64 IRQ2 enable high and low bit registers 65 **IRR 206** Irr 206

### J

JP 211 jump, conditional, relative, and relative conditional 211

### L

LD 210 LDC 210 LDCI 209, 210 LDE 210 LDEI 209, 210 LDX 210 259