Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 8KB (8K × 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081asj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |

|-------------------------|-------------------------|----------|-------------|------------|

| F85                     | Reserved                | —        | XX          |            |

| <b>Oscillator Contr</b> | ol                      |          |             |            |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |

| F87–F8F                 | Reserved                | _        | XX          |            |

| Comparator 0            |                         |          |             |            |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |

| F91–FBF                 | Reserved                | —        | XX          |            |

| Interrupt Contro        | oller                   |          |             |            |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |

| FC9–FCC                 | Reserved                | —        | XX          |            |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |

| GPIO Port A             |                         |          |             |            |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |

| GPIO Port B             |                         |          |             |            |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |

| GPIO Port C             |                         |          |             |            |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |

## Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

# HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate, if enabled

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections define the Power Control registers.

## **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

## Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>RFF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

| Bit     | 7                                                                                     | 6                             | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|---------------------------------------------------------------------------------------|-------------------------------|------|------|------|------|------|------|

| Field   | POC7                                                                                  | POC6                          | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D) |      |      |      |      |      |      |

| R/W     | R/W                                                                                   | R/W                           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |                               |      |      |      |      |      |      |

| D:4     | Decertation                                                                           |                               |      |      |      |      |      |      |

## Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

## Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7     | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | lf 04H ir | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit        | Description                                                       |

|------------|-------------------------------------------------------------------|

| [7:0]      | Port High Drive Enabled                                           |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |

|            | 1 = The port pin is configured for high output current drive.     |

| Note: x in | dicates the specific GPIO port pin number (7–0).                  |

## Port A–D Pull-up Enable Subregisters

The Port A–D Pull-up Enable Subregister, shown in Table 26, is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. Setting the bits in the Port A–D Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 7                                                                                     | 6                                                           | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Field   | PPUE7                                                                                 | PPUE6                                                       | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device) |       |       |       |       |       |       |

| R/W     | R/W                                                                                   | R/W                                                         | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |                                                             |       |       |       |       |       |       |

| Bit     | Description                                                                           | n                                                           |       |       |       |       |       |       |

| Table 26 | Dort    | וויים ח_א | IIn Enab |           | istors ( |        |

|----------|---------|-----------|----------|-----------|----------|--------|

| Table 20 | ). FUIL | A-D Fuii  | -∪p ⊏nau | le Subreg | isters ( | FXFUE) |

| Bit        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-up Enabled                              |

| PPUEx      | 0 = The weak pull-up on the port pin is disabled. |

|            | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x ii | ndicates the specific GPIO port pin number (7–0). |

## Port A–D Alternate Function Set 1 Subregisters

The Port A–D Alternate Function Set1 Subregister, shown in Table 27, is accessed through the Port A–D Control Register by writing 07H to the Port A–D Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in the <u>GPIO Alternate Functions</u> section on page 37.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A</u>– <u>D Alternate Function Subregisters</u> section on page 47.

# **LED Drive Enable Register**

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|------------|-----|-----|-----|-----|-----|-----|

| Field   |      | LEDEN[7:0] |     |     |     |     |     |     |

| RESET   | 0    | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F82H |            |     |     |     |     |     |     |

| Table 31. LED Drive Enable | (LEDEN) |

|----------------------------|---------|

|                            | ,       |

### Bit Description

[7:0] LED Drive Enable

LEDENx These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1 = Enable controlled current sink on the Port C pin.

**Note:** *x* indicates the specific GPIO port pin number (7–0).

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin, as shown in Table 32. These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit               | 7                                                                                                                                     | 6             | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|-----|-----|-----|-----|--|

| Field             | LEDLVLH[7:0]                                                                                                                          |               |     |     |     |     |     |     |  |

| RESET             | 0                                                                                                                                     | 0 0 0 0 0 0 0 |     |     |     |     |     |     |  |

| R/W               | R/W                                                                                                                                   | R/W           | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address           |                                                                                                                                       | -             |     | F8  | 3H  |     |     |     |  |

| Bit               | Descrip                                                                                                                               | Description   |     |     |     |     |     |     |  |

| [7:0]<br>LEDLVLH> | <b>LED Level High Bit</b><br>{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.<br>00 = 3mA |               |     |     |     |     |     |     |  |

| Table 32. LED | Drive Level | <b>High Register</b> | (LEDLVLH) |

|---------------|-------------|----------------------|-----------|

|               |             | ingii itogiotoi      |           |

01 = 7mA 10 = 13mA

11 = 20 mA

Note: x indicates the specific GPIO port pin number (7–0).

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|--|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |

| Address |         | FC4H    |        |        |               |        |        |        |  |

| Bit             | Description                                                   |

|-----------------|---------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] or LVD Interrupt Request Enable High Bit        |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit |

| [5:0]<br>PAxENH | Port A Bit[ <i>x</i> ] Interrupt Request Enable High Bit      |

See the <u>Shared Interrupt Select Register (IRQSS) Register</u> on page 68 for selection of either the LVD or the comparator as the interrupt source.

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address | FC5H    |         |        |        |               |        |        |        |

| Bit             | Description                                                  |

|-----------------|--------------------------------------------------------------|

| [7]<br>PA7VENL  | Port A Bit[7] or LVD Interrupt Request Enable Low Bit        |

| [6]<br>PA6CENL  | Port A Bit[6] or Comparator Interrupt Request Enable Low Bit |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |

## **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 44 and 45, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register. The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                                | 6                                                                                                                                                                                                                                                                                                                                | 5    | 4        | 3    | 2    | 1   | 0      |  |

|----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|------|-----|--------|--|

| Field          | TMODEHI                          | TICO                                                                                                                                                                                                                                                                                                                             | NFIG | Reserved |      | PWMD |     | INPCAP |  |

| RESET          | 0                                | 0                                                                                                                                                                                                                                                                                                                                | 0    | 0        | 0    | 0    | 0   | 0      |  |

| R/W            | R/W                              | R/W                                                                                                                                                                                                                                                                                                                              | R/W  | R/W      | R/W  | R/W  | R/W | R      |  |

| Address        |                                  |                                                                                                                                                                                                                                                                                                                                  |      | F06H,    | F0EH |      |     |        |  |

| Bit            | Descript                         | Description                                                                                                                                                                                                                                                                                                                      |      |          |      |      |     |        |  |

| [7]<br>TMODEHI | This bit,<br>mode of<br>the desc | Timer Mode High Bit     This bit, along with the TMODE field in the TxCTL1 Register, determines the operating mode of the timer. This bit is the most significant bit of the Timer mode selection value. See the description of the <u>Timer 0–1 Control Register 1 (TxCTL1)</u> for details about the full timer mode decoding. |      |          |      |      |     |        |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

| Bit   | Description (Continued)                                                                        |

|-------|------------------------------------------------------------------------------------------------|

| [1:0] | For 8-pin devices, the following voltages can be configured; for 20- and 28-pin devices, these |

|       | bits are reserved.                                                                             |

|       | 000000 = 0.00 V                                                                                |

|       | 000001 = 0.05 V                                                                                |

|       | 000010 = 0.10 V                                                                                |

|       | 000011 = 0.15 V                                                                                |

|       | 000100 = 0.20 V                                                                                |

|       | 000101 = 0.25 V                                                                                |

|       | 000110 = 0.30 V                                                                                |

|       | 000111 = 0.35 V                                                                                |

|       | 001000 = 0.40  V                                                                               |

|       | 001001 = 0.45 V                                                                                |

|       | 001010 = 0.50  V                                                                               |

|       | 001011 = 0.55 V                                                                                |

|       | 001100 = 0.60  V                                                                               |

|       | 001101 = 0.65 V                                                                                |

|       | 001110 = 0.70 V                                                                                |

|       | 001111 = 0.75 V                                                                                |

|       | 010000 = 0.80  V                                                                               |

|       | 010001 = 0.85  V                                                                               |

|       | 010010 = 0.90  V                                                                               |

|       | 010011 = 0.95  V                                                                               |

|       | 010100 = 1.00  V (Default)                                                                     |

|       | 010101 = 1.05  V                                                                               |

|       | 010110 = 1.10 V<br>010111 = 1.15 V                                                             |

|       | 01000 = 1.20  V                                                                                |

|       | 011001 = 1.25 V                                                                                |

|       | 011010 = 1.30  V                                                                               |

|       | 011011 = 1.35 V                                                                                |

|       | 011100 = 1.40  V                                                                               |

|       | 011101 = 1.45 V                                                                                |

|       | 011110 = 1.50 V                                                                                |

|       | 011111 = 1.55 V                                                                                |

|       | 100000 = 1.60  V                                                                               |

|       | 100001 = 1.65  V                                                                               |

|       | 100010 = 1.70  V                                                                               |

|       | 100011 = 1.75 V                                                                                |

|       | 100100 = 1.80  V                                                                               |

# **ADC Calibration Data**

## Table 96. ADC Calibration Bits

| Bit        | 7                                   | 6           | 5             | 4      | 3   | 2   | 1   | 0   |

|------------|-------------------------------------|-------------|---------------|--------|-----|-----|-----|-----|

| Field      | ADC_CAL                             |             |               |        |     |     |     |     |

| RESET      | U                                   | U           | U             | U      | U   | U   | U   | U   |

| R/W        | R/W                                 | R/W         | R/W           | R/W    | R/W | R/W | R/W | R/W |

| Address    | Information Page Memory 0060H–007DH |             |               |        |     |     |     |     |

| Noto: II - | I Inchanged h                       | W Reset R/M | / - Road/Writ | ۰<br>۵ |     |     |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

# Bit Description

[7:0] Analog-to-Digital Converter Calibration Values

ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in the Software Compensation Procedure Using Factory Calibration Data section on page 129. The location of each calibration byte is provided in Table 97.

| Info Page | Memory  |                    |                          |                |

|-----------|---------|--------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage | ADC Mode                 | Reference Type |

| 60        | FE60    | Offset             | Single-Ended Unbuffered  | Internal 2.0 V |

| 08        | FE08    | Gain High Byte     | Single-Ended Unbuffered  | Internal 2.0 V |

| 09        | FE09    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 2.0 V |

| 63        | FE63    | Offset             | Single-Ended Unbuffered  | Internal 1.0 V |

| 0A        | FE0A    | Gain High Byte     | Single-Ended Unbuffered  | Internal 1.0 V |

| 0B        | FE0B    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 1.0 V |

| 66        | FE66    | Offset             | Single-Ended Unbuffered  | External 2.0 V |

| 0C        | FE0C    | Gain High Byte     | Single-Ended Unbuffered  | External 2.0 V |

| 0D        | FE0D    | Gain Low Byte      | Single-Ended Unbuffered  | External 2.0 V |

| 69        | FE69    | Offset             | Single-Ended 1x Buffered | Internal 2.0 V |

| 0E        | FE0E    | Gain High Byte     | Single-Ended 1x Buffered | Internal 2.0 V |

| 0F        | FE0F    | Gain Low Byte      | Single-Ended 1x Buffered | Internal 2.0 V |

| 6C        | FE6C    | Offset             | Single-Ended 1x Buffered | External 2.0 V |

| 10        | FE10    | Gain High Byte     | Single-Ended 1x Buffered | External 2.0 V |

| 11        | FE11    | Gain Low Byte      | Single-Ended 1x Buffered | External 2.0 V |

| 6F        | FE6F    | Offset             | Differential Unbuffered  | Internal 2.0 V |

## Table 97. ADC Calibration Data Location

# **Temperature Sensor Calibration Data**

## Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field     | TSCALH                                          |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 003A                    |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

#### Bit Description [7:0] **Temperature Sensor Calibration High Byte** TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-

tion value. For more details, see Temperature Sensor Operation on page 139.

## Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field     | TSCALL                                          |     |     |     |     |     |     |     |  |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address   | Information Page Memory 003B                    |     |     |     |     |     |     |     |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |  |

#### Bit Description

| [7:0]  | Temperature Sensor Calibration Low Byte                                                   |

|--------|-------------------------------------------------------------------------------------------|

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra- |

|        | tion value. For usage details, see the Temperature Sensor Operation section on page 144.  |

# Watchdog Timer Calibration Data

## Table 100. Watchdog Calibration High Byte at 007EH (WDTCALH)

| Bit       | 7                               | 6           | 5             | 4       | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|---------------------------------|-------------|---------------|---------|-----|-----|-----|-----|--|--|--|--|

| Field     |                                 |             |               | WDTCALH |     |     |     |     |  |  |  |  |

| RESET     | U                               | U           | U             | U       | U   | U   | U   |     |  |  |  |  |

| R/W       | R/W                             | R/W         | R/W           | R/W     | R/W | R/W | R/W | R/W |  |  |  |  |

| Address   | s Information Page Memory 007EH |             |               |         |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged h                     | w Reset R/M | / = Read/Writ | e.      |     |     |     |     |  |  |  |  |

Note: U = Unchanged by Reset. R/W = Read/Write.

### Bit Description

[7:0] Watchdog Timer Calibration High Byte

WDTCALH

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second time-out at room temperature and 3.3V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-CALH and WDTL with WDTCALL.

## **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine  $(0 \times 1000)$ . At the return from the sub-routine, the read byte resides in working register R0 and the read status byte resides in working register R1. The contents of the status byte are undefined for read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is nonzero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

## **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

# **Optimizing NVDS Memory Usage for Execution Speed**

NVDS read time can vary drastically. This discrepancy is a trade-off for minimizing the frequency of writes that require post-write page erases, as indicated in Table 107. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, plus the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1 µs up to a maximum of (511-NVDS\_SIZE)µs.

# **On-Chip Debugger**

The Z8 Encore! XP F082A Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize pins available to the user (8-pin product only)

# Architecture

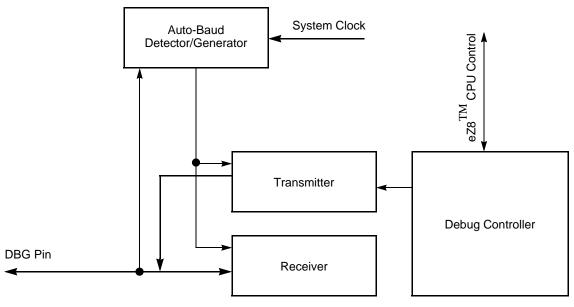

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator and debug controller. Figure 23 displays the architecture of the on-chip debugger.

Figure 23. On-Chip Debugger Block Diagram

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled High. At this point, the PA0/DBG pin may be used to autobaud and cause the device to enter DEBUG Mode. See the <u>OCD Unlock Sequence (8-Pin Devices Only) section on</u> page 185.

## **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

## OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character transmitted and received by the OCD consists of 1 Start bit, 8 data bits (least-significant bit first) and 1 Stop bit as displayed in Figure 26.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

|           |    |    |    |    |    |    |    |    | 1    |

Figure 26. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open drain output to avoid this issue.

## **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the

# **Crystal Oscillator**

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

| Assembly         |                                                                                           |     | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|------------------|-------------------------------------------------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src          | (Hex)       | С | Ζ | S   | V   | D | Н | S              | S               |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r   | r            | 52          | _ | * | *   | 0   | _ | _ | 2              | 3               |

|                  |                                                                                           | r   | Ir           | 53          |   |   |     |     |   |   | 2              | 4               |

|                  |                                                                                           | R   | R            | 54          |   |   |     |     |   |   | 3              | 3               |

|                  |                                                                                           | R   | IR           | 55          |   |   |     |     |   |   | 3              | 4               |

|                  |                                                                                           | R   | IM           | 56          |   |   |     |     |   |   | 3              | 3               |

|                  |                                                                                           | IR  | IM           | 57          |   |   |     |     |   |   | 3              | 4               |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER  | ER           | 58          | - | * | *   | 0   | - | - | 4              | 3               |

|                  |                                                                                           | ER  | IM           | 59          |   |   |     |     |   |   | 4              | 3               |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |     |              | 2F          | - | - | _   | _   | _ | _ | 1              | 2               |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |              | E2          | - | _ | _   | _   | _ | _ | 2              | 2               |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |              | E2          | - | _ | -   | -   | _ | - | 2              | 2               |

| BRK              | Debugger Break                                                                            |     |              | 00          | - | _ | -   | -   | _ | - | 1              | 1               |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |              | E2          | - | _ | -   | -   | _ | - | 2              | 2               |

| BSWAP dst        | $dst[7:0] \leftarrow dst[0:7]$                                                            | R   |              | D5          | Х | * | *   | 0   | _ | - | 2              | 2               |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r            | F6          | - | _ | -   | -   | _ | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

| BTJNZ bit, src,  | if src[bit] = 1                                                                           |     | r            | F6          | - | _ | -   | -   | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r            | F6          | - | _ | -   | -   | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

## Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly        |                                     |       | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|-----------------|-------------------------------------|-------|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic        | Symbolic Operation                  | dst   | src         | (Hex)       | С | Ζ | S   | v   | D | н | S              | S               |

| LDX dst, src    | $dst \leftarrow src$                | r     | ER          | 84          | - | - | -   | -   | _ | - | 3              | 2               |

|                 |                                     | lr    | ER          | 85          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | R     | IRR         | 86          | - |   |     |     |   |   | 3              | 4               |

|                 |                                     | IR    | IRR         | 87          |   |   |     |     |   |   | 3              | 5               |

|                 |                                     | r     | X(rr)       | 88          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | X(rr) | r           | 89          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | ER    | r           | 94          |   |   |     |     |   |   | 3              | 2               |

|                 |                                     | ER    | lr          | 95          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | IRR   | R           | 96          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | IRR   | IR          | 97          | - |   |     |     |   |   | 3              | 5               |

|                 |                                     | ER    | ER          | E8          | - |   |     |     |   |   | 4              | 2               |

|                 |                                     | ER    | IM          | E9          | - |   |     |     |   |   | 4              | 2               |

| LEA dst, X(src) | $dst \gets src + X$                 | r     | X(r)        | 98          | _ | - | -   | -   | - | - | 3              | 3               |

|                 |                                     | rr    | X(rr)       | 99          |   |   |     |     |   |   | 3              | 5               |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4          | _ | - | _   | -   | - | _ | 2              | 8               |

| NOP             | No operation                        |       |             | 0F          | - | - | -   | -   | - | - | 1              | 2               |

| OR dst, src     | $dst \gets dst  OR  src$            | r     | r           | 42          | _ | * | *   | 0   | - | _ | 2              | 3               |

|                 |                                     | r     | lr          | 43          | - |   |     |     |   |   | 2              | 4               |

|                 |                                     | R     | R           | 44          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | R     | IR          | 45          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | R     | IM          | 46          | - |   |     |     |   |   | 3              | 3               |

|                 |                                     | IR    | IM          | 47          | - |   |     |     |   |   | 3              | 4               |

## Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

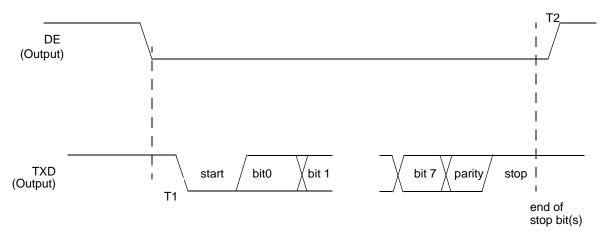

Figure 38 and Table 147 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 147 | UART T | imina Wit   | hout CTS |

|-----------|--------|-------------|----------|

|           |        | mining with |          |

|                |                                                                        | Delay (ns)                 |            |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |

| UART           |                                                                        |                            |            |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                        |            |  |  |

compare with carry - extended addressing 208 complement 210 complement carry flag 209 condition code 206 continuous conversion (ADC) 127 **CONTINUOUS** mode 87 control register definition, UART 110 Control Registers 15, 18 **COUNTER modes 87** CP 208 **CPC 208 CPCX 208** CPU and peripheral overview 4 CPU control instructions 209 **CPX 208** Customer Feedback Form 265

# D

DA 206, 208 data memory 17 DC characteristics 227 debugger, on-chip 180 **DEC 208** decimal adjust 208 decrement 208 decrement and jump non-zero 211 decrement word 208 **DECW 208** destination operand 207 device, port availability 36 DI 209 direct address 206 disable interrupts 209 DJNZ 211 dst 207

# Ε

EI 209 electrical characteristics 226 ADC 236 flash memory and timing 234 GPIO input data sample timing 240 Watchdog Timer 235, 238 enable interrupt 209 ER 206 extended addressing register 206 external pin reset 26 eZ8 CPU features 4 eZ8 CPU instruction classes 207 eZ8 CPU instruction notation 206 eZ8 CPU instruction set 204 eZ8 CPU instruction summary 212

# F

FCTL register 155, 161, 162 features, Z8 Encore! 1 first opcode map 224 FLAGS 207 flags register 207 flash controller 6 option bit address space 162 option bit configuration - reset 159 program memory address 0000H 162 program memory address 0001H 164 flash memory 146 arrangement 147 byte programming 151 code protection 149 configurations 146 control register definitions 153, 161 controller bypass 152 electrical characteristics and timing 234 flash control register 155, 161, 162 flash option bits 150 flash status register 155 flow chart 148 frequency high and low byte registers 157 mass erase 152 operation 147 operation timing 149 page erase 152 page select register 156, 157 FPS register 156, 157 FSTAT register 155