Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Due durch Chabura          | Obselete                                                  |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081asj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers                   |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

### vi

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brown-Out (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO and LVD

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- 8-, 20- and 28-pin packages

- $0^{\circ}$ C to  $+70^{\circ}$ C and  $-40^{\circ}$ C to  $+105^{\circ}$ C for operating temperature ranges

# **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP F082A Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Mateau         |               |            |                          |      |            |                                 |               |                    |

#### Table 1. Z8 Encore! XP F082A Series Family Part Selection Guide

Notes:

1. Non-volatile data storage.

2. Advanced Analog includes ADC, temperature sensor and low-power operational amplifier.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                           | 5             | 4           | 3                               | 2        | 1 | 0   |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|---------------------------------|----------|---|-----|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                             | STOP                                                                                                                                                                                                                        | WDT           | EXT         |                                 | Reserved |   | LVD |  |

| RESET       | See c                                                                                                                                                                                                                                                                                                                                                                                                                                           | lescriptions                                                                                                                                                                                                                | below         | 0           | 0                               | 0        | 0 | 0   |  |

| R/W         | R R R R R R                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |               |             |                                 |          |   | R   |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                             |               | FF          | ЮH                              |          |   |     |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                 |               |             |                                 |          |   |     |  |

| [7]<br>POR  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or<br>Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read. |               |             |                                 |          |   |     |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                             |               |             |                                 |          |   |     |  |

| [5]<br>WDT  | Watchdog Timer Time-Out Indicator<br>If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery<br>from a change in an input pin also resets this bit. Reading this register resets this bit. This read<br>must occur before clearing the WDT interrupt.                                                                                                                                                       |                                                                                                                                                                                                                             |               |             |                                 |          |   |     |  |

| [4]<br>EXT  | <b>External Reset Indicator</b><br>If this bit is set to 1, a Reset initiated by the external RESET pin occurs. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                            |                                                                                                                                                                                                                             |               |             |                                 |          |   |     |  |

| [3:1]       | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                          | are reserved                                                                                                                                                                                                                | d and must b  | be programn | ned to 000.                     |          |   |     |  |

| [0]<br>LVD  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                             | current state |             | oly voltage is<br>I-time indica |          | • |     |  |

### Table 11. Reset Status Register (RSTSTAT)

# **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|-----------------------------|---|---|---|---|---|---|

| Field   | PCTL |                             |   |   |   |   |   |   |

| RESET   |      | 00H                         |   |   |   |   |   |   |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| Address |      | FD1H, FD5H, FD9H, FDDH      |   |   |   |   |   |   |

#### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |  |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

# Port A–D Alternate Function Subregisters

The Port A–D Alternate Function Subregister, shown in Table 22, is accessed through the Port A–D Control Register by writing 02H to the Port A–D Address Register. The Port A–D Alternate Function subregisters enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the the Port A–D Alternate Functions section on page 37 and the Port A–D Alternate Function Set 2 Subregisters section on page 51. See the <u>GPIO Alternate Functions</u> section on page 37 to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Bit     | 7                                                           | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | AF7                                                         | AF6                                                                                   | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |

| RESET   | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device) |                                                                                       |     |     |     |     |     |     |

| R/W     |                                                             | R/W                                                                                   |     |     |     |     |     |     |

| Address | If 02H ir                                                   | If 02H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |

| Bit   | Description                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function Enabled                                                                                                                            |

| AFx   | 0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction subregister determines the direction of the pin.                         |

|       | 1 = The alternate function selected through Alternate Function Set subregisters is enabled.<br>Port pin operation is controlled by the alternate function. |

Note: x indicates the specific GPIO port pin number (7-0).

### Port A–D Output Control Subregisters

The Port A–D Output Control Subregister, shown in Table 23, is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. Setting the bits in the Port A–D Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

### **Timer Pin Signal Operation**

The timer output function is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded. The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                   | 6           | 5   | 4        | 3   | 2    | 1          | 0      |  |

|----------------|---------------------|-------------|-----|----------|-----|------|------------|--------|--|

| Field          | TMODEHI             | TICONFIG    |     | Reserved |     | PWMD |            | INPCAP |  |

| RESET          | 0                   | 0           | 0   | 0        | 0   | 0    | 0          | 0      |  |

| R/W            | R/W                 | R/W         | R/W | R/W      | R/W | R/W  | R/W        | R      |  |

| Address        |                     | F06H, F0EH  |     |          |     |      |            |        |  |

| Bit            | Descript            | Description |     |          |     |      |            |        |  |

| [7]<br>TMODEHI | Timer Mode High Bit |             |     |          |     |      | value. See |        |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7   | 6          | 5                 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----|------------|-------------------|---|---|---|---|---|--|--|--|

| Field   | TEN | TPOL       | PRES TMODE        |   |   |   |   |   |  |  |  |

| RESET   | 0   | 0          | 0                 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W     | R/W | R/W        | R/W R/W R/W R/W F |   |   |   |   |   |  |  |  |

| Address |     | F07H, F0FH |                   |   |   |   |   |   |  |  |  |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|

| Field   |     | TH                          |   |   |   |   |   |   |  |  |  |

| RESET   | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| Address |     | F00H, F08H                  |   |   |   |   |   |   |  |  |  |

### Table 52. Timer 0–1 High Byte Register (TxH)

### Table 53. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6           | 5   | 4     | 3 2  |     | 1   | 0   |  |  |  |

|---------|-----|-------------|-----|-------|------|-----|-----|-----|--|--|--|

| Field   | TL  |             |     |       |      |     |     |     |  |  |  |

| RESET   | 0   | 0 0 0 0 0 0 |     |       |      |     |     |     |  |  |  |

| R/W     | R/W | R/W         | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |

| Address |     |             |     | F01H, | F09H |     |     |     |  |  |  |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered down.

# **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value overwrites the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the appropriate analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

# **Calibration and Compensation**

The Z8 Encore! XP F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL Mode operation.

# **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 168.

# **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and nonlinearity; therefore Zilog recommends that this calibration be performed separately for each of the ADC input modes planned for use.

# **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see <u>Table 139</u> on page 236). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION Mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in nonvolatile memory (see the <u>Nonvolatile Data Storage</u> chapter on page 176) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

# Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2$$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

| Bit                                                                                                                                                                               | 7                                             | 6                                                                             | 5              | 4                                                                     | 3                                                              | 2 1 0                           |   |     |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------|---|-----|--|--|--|

| Field                                                                                                                                                                             | REFSELH                                       |                                                                               | Rese           | erved                                                                 |                                                                | BUFMODE[2:0]                    |   |     |  |  |  |

| RESET                                                                                                                                                                             | 1                                             | 0                                                                             | 0              | 0                                                                     | 0                                                              | 0                               | 0 | 0   |  |  |  |

| R/W                                                                                                                                                                               | R/W                                           | R/W                                                                           | R/W            | R/W                                                                   | R/W                                                            | R/W R/W                         |   | R/W |  |  |  |

| Address                                                                                                                                                                           |                                               | F71H                                                                          |                |                                                                       |                                                                |                                 |   |     |  |  |  |

| Bit                                                                                                                                                                               | Bit Description                               |                                                                               |                |                                                                       |                                                                |                                 |   |     |  |  |  |

| [7]<br>REFSELH                                                                                                                                                                    | I In co<br>the le<br>REF<br>00=<br>01=<br>10= | onjunction w<br>evel of the in<br>SELL}; this<br>Internal Ref<br>Internal Ref | nternal voltag | bit (REFSEL<br>ge reference<br>independer<br>bled, referen<br>o 1.0V. | L) in ADC C<br>; the followir<br>at of the Com<br>ace comes fi | ng details the<br>nparator refe |   |     |  |  |  |

| [6:3]                                                                                                                                                                             |                                               | erved<br>se bits are re                                                       | eserved and    | must be pro                                                           | ogrammed to                                                    | o 0000.                         |   |     |  |  |  |

| [2:0] Input Buffer Mode Select<br>BUFMODE[2:0] 000 = Single-ended, unbuffered input.<br>001 = Single-ended, buffered input with unity gain.<br>010 = Reserved.<br>011 = Reserved. |                                               |                                                                               |                |                                                                       |                                                                |                                 |   |     |  |  |  |

#### Table 74. ADC Control/Status Register 1 (ADCCTL1)

100 = Differential, unbuffered input.101 = Differential, buffered input with unity gain.

110 = Reserved. 111 = Reserved.

# ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) Register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

# **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

# **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

# **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7           | 6      | 5      | 4 3    |        | 2      | 1      | 0      |

|---------|-------------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7      | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0           | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W R/W R/W |        | R/W    | R/W    | R/W    | R/W    | R/W    |        |

| Address |             |        |        | FF     | 9H     |        |        |        |

Table 83. Flash Sector Protect Register (FPROT)

#### Bit Description

#### [7:0] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

# **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine  $(0 \times 1000)$ . At the return from the sub-routine, the read byte resides in working register R0 and the read status byte resides in working register R1. The contents of the status byte are undefined for read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is nonzero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

# **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

# **Optimizing NVDS Memory Usage for Execution Speed**

NVDS read time can vary drastically. This discrepancy is a trade-off for minimizing the frequency of writes that require post-write page erases, as indicated in Table 107. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, plus the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1 µs up to a maximum of (511-NVDS\_SIZE)µs.

the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry and all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

# **Oscillator Control Register Definitions**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Unlock the Oscillator Control Register by writing the two-step sequence E7H followed by 18H. The register is locked at successful completion of a register write to the OSCCTL.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 0           |  |  |  |

|---------|-------|-------|-------|-------|-------|--------|-------------|--|--|--|

| Field   | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL |             |  |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0 0 0       |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W R/W R/W |  |  |  |

| Address |       |       |       | F8    | 6H    |        |             |  |  |  |

Table 113. Oscillator Control Register (OSCCTL)

| Bit          | Description                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                             |

| [6]<br>XTLEN | Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled.                            |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                         |

| [4]<br>SOFEN | System Clock Oscillator Failure Detection Enable1 = Failure detection and recovery of system clock oscillator is enabled.0 = Failure detection and recovery of system clock oscillator is disabled. |

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

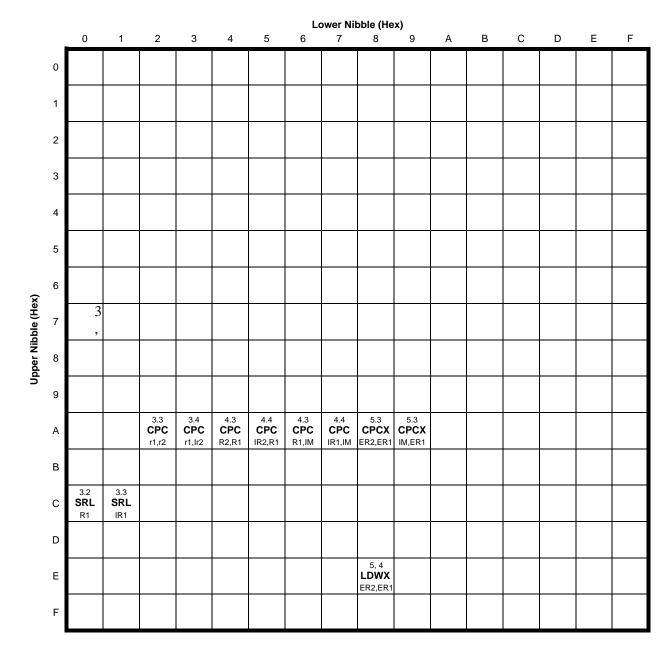

Figure 32. Second Opcode Map after 1FH

| Part Number                           | Flash    | RAM      | SDAN    | -<br>I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------|----------|----------|---------|----------------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A                   |          |          | NB Flas | sn             |            |                     |                     |                |            |                    |                     |

| Standard Temperatur<br>Z8F021APB020SG | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F021AQB020SG                        | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F021ASB020SG                        | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F021ASH020SG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F021AHH020SG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F021APH020SG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F021ASJ020SG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F021AHJ020SG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F021APJ020SG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu                    | re: –40° | °C to 10 | 5°C     |                |            |                     |                     |                |            |                    |                     |

| Z8F021APB020EG                        | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F021AQB020EG                        | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F021ASB020EG                        | 2 KB     | 512 B    | 64 B    | 6              | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F021ASH020EG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F021AHH020EG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F021APH020EG                        | 2 KB     | 512 B    | 64 B    | 17             | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F021ASJ020EG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F021AHJ020EG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F021APJ020EG                        | 2 KB     | 512 B    | 64 B    | 25             | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.