Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | ·                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082ahj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### xi

# List of Figures

| Figure 1.  | Z8 Encore! XP F082A Series Block Diagram 3                                      |

|------------|---------------------------------------------------------------------------------|

| Figure 2.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package |

| Figure 3.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package      |

| Figure 4.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package      |

| Figure 5.  | Power-On Reset Operation                                                        |

| Figure 6.  | Voltage Brown-Out Reset Operation                                               |

| Figure 7.  | GPIO Port Pin Block Diagram                                                     |

| Figure 8.  | Interrupt Controller Block Diagram                                              |

| Figure 9.  | Timer Block Diagram                                                             |

| Figure 10. | UART Block Diagram 100                                                          |

| Figure 11. | UART Asynchronous Data Format without Parity                                    |

| Figure 12. | UART Asynchronous Data Format with Parity 101                                   |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 105                           |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 107         |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                    |

| Figure 16. | Infrared Data Communication System Block Diagram                                |

| Figure 17. | Infrared Data Transmission                                                      |

| Figure 18. | IrDA Data Reception 122                                                         |

| Figure 19. | Analog-to-Digital Converter Block Diagram                                       |

| Figure 20. | Comparator Block Diagram 140                                                    |

| Figure 21. | Flash Memory Arrangement 147                                                    |

| Figure 22. | Flash Controller Operation Flow Chart 148                                       |

| Figure 23. | On-Chip Debugger Block Diagram 180                                              |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface;<br>#1 of 2 |

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

## Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

## **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

## **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### **General-Purpose Input/Output**

The Product Line MCUs feature 6 to 25 port pins (Ports A–D) for general- purpose input/ output (GPIO). The number of GPIO pins available is a function of package and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, plus factory serialization and read protection.

#### Non-Volatile Data Storage

The nonvolatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8KB of Flash memory do not include the NVDS feature.

#### Interrupt Controller

The Z8 Encore! XP F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit, or Voltage Brown-Out (VBO)

**Caution:** To avoid retriggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, Zilog recommends that the service routine continues to read from the RSTSTAT Register until the WDT bit is cleared as shown in the following example.

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests.

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 Register to determine if any interrupt requests are pending.

| Bit     | 7        | 6    | 5   | 4     | 3     | 2        | 1        | 0    |  |  |

|---------|----------|------|-----|-------|-------|----------|----------|------|--|--|

| Field   | Reserved | T1I  | TOI | U0RXI | U0TXI | Reserved | Reserved | ADCI |  |  |

| RESET   | 0        | 0    | 0   | 0     | 0     | 0        | 0        | 0    |  |  |

| R/W     | R/W      | R/W  | R/W | R/W   | R/W   | R/W      | R/W      | R/W  |  |  |

| Address |          | FC0H |     |       |       |          |          |      |  |  |

| Bit        | Description                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                               |

| [6]<br>T1I | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service. |

| [5]<br>T0I | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from Timer 0 is awaiting service. |

#### Table 39. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit          | 7                                         | 6                                                | 5           | 4             | 3             | 2        | 1        | 0      |  |  |

|--------------|-------------------------------------------|--------------------------------------------------|-------------|---------------|---------------|----------|----------|--------|--|--|

| Field        | Reserved                                  | T1ENH                                            | T0ENH       | <b>U0RENH</b> | <b>U0TENH</b> | Reserved | Reserved | ADCENH |  |  |

| RESET        | 0                                         | 0                                                | 0           | 0             | 0             | 0        | 0        | 0      |  |  |

| R/W          | R/W                                       | R/W                                              | R/W         | R/W           | R/W           | R/W      | R/W      | R/W    |  |  |

| Address      |                                           |                                                  |             | FC            | 1H            |          |          |        |  |  |

|              |                                           |                                                  |             |               |               |          |          |        |  |  |

| Bit          | Description                               | n                                                |             |               |               |          |          |        |  |  |

| [7]          | Reserved<br>This bit is re                | eserved and                                      | must be pro | ogrammed to   | o 0.          |          |          |        |  |  |

| [6]<br>T1ENH | Timer 1 Int                               | errupt Req                                       | uest Enable | e High Bit    |               |          |          |        |  |  |

| [5]<br>T0ENH | Timer 0 Interrupt Request Enable High Bit |                                                  |             |               |               |          |          |        |  |  |

|              | UART 0 Re                                 | UART 0 Receive Interrupt Request Enable High Bit |             |               |               |          |          |        |  |  |

| <b>U0RENH</b> |                                                                   |

|---------------|-------------------------------------------------------------------|

| [3]<br>UOTENH | UART 0 Transmit Interrupt Request Enable High Bit                 |

| [2:1]         | Reserved<br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                             |

| Bit     | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |

|---------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |

| RESET   | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |

| Address | FC2H     |       |              |               |               |          |          |        |  |

#### Table 40. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit          | Description                                                   |

|--------------|---------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                      |

| [5]<br>T0ENL | Timer 0 Interrupt Request Enable Low Bit                      |

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults and other system-level problems which may place the Z8 Encore! XP F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

## Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequenc |                        |  |  |

|------------------|------------------|---------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)        | Typical                                                                   | Description            |  |  |

| 000004           | 4                | 400 μs                                                                    | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                | Maximum time-out delay |  |  |

#### Table 58. Watchdog Timer Approximate Time-Out Delays

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | N/A                      | N/A                  | N/A          | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 1                        | 223.72               | -10.51       | 250.0                    | N/A                      | N/A                  | N/A          |

| 115.2                    | 2                        | 111.9                | -2.90        | 115.2                    | 1                        | 115.2                | 0.00         |

| 57.6                     | 4                        | 55.9                 | -2.90        | 57.6                     | 2                        | 57.6                 | 0.00         |

| 38.4                     | 6                        | 37.3                 | -2.90        | 38.4                     | 3                        | 38.4                 | 0.00         |

| 19.2                     | 12                       | 18.6                 | -2.90        | 19.2                     | 6                        | 19.2                 | 0.00         |

| 9.60                     | 23                       | 9.73                 | 1.32         | 9.60                     | 12                       | 9.60                 | 0.00         |

| 4.80                     | 47                       | 4.76                 | -0.83        | 4.80                     | 24                       | 4.80                 | 0.00         |

| 2.40                     | 93                       | 2.41                 | 0.23         | 2.40                     | 48                       | 2.40                 | 0.00         |

| 1.20                     | 186                      | 1.20                 | 0.23         | 1.20                     | 96                       | 1.20                 | 0.00         |

| 0.60                     | 373                      | 0.60                 | -0.04        | 0.60                     | 192                      | 0.60                 | 0.00         |

| 0.30                     | 746                      | 0.30                 | -0.04        | 0.30                     | 384                      | 0.30                 | 0.00         |

|                          |                          |                      |              |                          |                          |                      |              |

#### Table 72. UART Baud Rates (Continued)

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered down.

## **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value overwrites the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the appropriate analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect Register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select Register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the Page Select Register to unlock the Flash Controller is not necessary.

- The Page Select Register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control Register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 153

Flash Status Register: see page 155

Flash Page Select Register: see page 156

Flash Sector Protect Register: see page 157

Flash Frequency High and Low Byte Registers: see page 157

#### **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FCTL) Register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select Register. Mass Erase is enabled only through the On-Chip

## **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address |        | FF9H   |        |        |        |        |        |        |  |  |

Table 83. Flash Sector Protect Register (FPROT)

#### Bit Description

#### [7:0] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

## **Randomized Lot Identifier**

#### Table 104. Lot Identification Number (RAND\_LOT)

| Bit                                             | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------------------------------------------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field                                           | RAND_LOT                                        |     |     |     |     |     |     |     |  |  |

| RESET                                           | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W                                             | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address                                         | Interspersed throughout Information Page Memory |     |     |     |     |     |     |     |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                                 |     |     |     |     |     |     |     |  |  |

# Bit Description [7] Randomized Lot ID RAND\_LOT The randomized lot ID is a 32-byte binary value that changes for each production lot. See Table 105.

#### Table 105. Randomized Lot ID Locations

| Info Page | Memory  |                                               |

|-----------|---------|-----------------------------------------------|

| Address   | Address | Usage                                         |

| 3C        | FE3C    | Randomized Lot ID Byte 31 (most significant). |

| 3D        | FE3D    | Randomized Lot ID Byte 30.                    |

| 3E        | FE3E    | Randomized Lot ID Byte 29.                    |

| 3F        | FE3F    | Randomized Lot ID Byte 28.                    |

| 58        | FE58    | Randomized Lot ID Byte 27.                    |

| 59        | FE59    | Randomized Lot ID Byte 26.                    |

| 5A        | FE5A    | Randomized Lot ID Byte 25.                    |

| 5B        | FE5B    | Randomized Lot ID Byte 24.                    |

| 5C        | FE5C    | Randomized Lot ID Byte 23.                    |

| 5D        | FE5D    | Randomized Lot ID Byte 22.                    |

| 5E        | FE5E    | Randomized Lot ID Byte 21.                    |

| 5F        | FE5F    | Randomized Lot ID Byte 20.                    |

| 61        | FE61    | Randomized Lot ID Byte 19.                    |

| 62        | FE62    | Randomized Lot ID Byte 18.                    |

| 64        | FE64    | Randomized Lot ID Byte 17.                    |

| 65        | FE65    | Randomized Lot ID Byte 16.                    |

| 67        | FE67    | Randomized Lot ID Byte 15.                    |

| 68        | FE68    | Randomized Lot ID Byte 14.                    |

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (16 byte array)   | 875                | 9961               |

| Read (64 byte array)   | 876                | 8952               |

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

|                        |                    |                    |

#### Table 107. NVDS Read Time

If NVDS read performance is critical to your software architecture, you can optimize your code for speed. Try the first suggestion below before attempting the second.

- 1. Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- 2. Use as few unique addresses as possible to optimize the impact of refreshing, plus minimize the requirement for it.

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30°C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control Register (see the <u>Oscillator</u> <u>Control Register Definitions section on page 196</u>).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in the <u>Trim Bit Address Space</u> section on page 165.

Select one of two frequencies for the oscillator (5.53MHz and 32.8kHz) using the OSC-SEL bits in the the <u>Oscillator Control</u> chapter on page 193.

| 24 | 0 |

|----|---|

| 21 | Ö |

| Assembly     |                                                                          |     | lress<br>ode | _ Opcode(s) |     |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|--------------------------------------------------------------------------|-----|--------------|-------------|-----|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                       | dst | src          | (Hex)       |     | Ζ | S   | V   | D | Н | s              | S               |

| ORX dst, src | $dst \gets dst \ OR \ src$                                               | ER  | ER           | 48          | -   | * | *   | 0   | - | - | 4              | 3               |

|              |                                                                          | ER  | IM           | 49          | -   |   |     |     |   |   | 4              | 3               |

| POP dst      | dst ← @SP                                                                | R   |              | 50          | -   | _ | -   | -   | - | - | 2              | 2               |

|              | $SP \leftarrow SP + 1$                                                   | IR  |              | 51          | -   |   |     |     |   |   | 2              | 3               |

| POPX dst     | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER  |              | D8          | -   | _ | -   | -   | _ | - | 3              | 2               |

| PUSH src     | $SP \leftarrow SP - 1$                                                   | R   |              | 70          | -   |   | _   | -   | - | - | 2              | 2               |

|              | @SP ← src                                                                | IR  |              | 71          |     |   |     |     |   | 2 | 3              |                 |

|              |                                                                          | IM  |              | IF70        |     |   |     |     |   |   | 3              | 2               |

| PUSHX src    | $SP \leftarrow SP - 1$<br>@ $SP \leftarrow src$                          | ER  |              | C8          | _   | - | _   | -   | _ | _ | 3              | 2               |

| RCF          | C ← 0                                                                    |     |              | CF          | 0   | _ | _   | _   | _ | _ | 1              | 2               |

| RET          | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |              | AF          | _   | - | _   | _   | _ | _ | 1              | 4               |

| RL dst       | C D7D6D5D4D3D2D1D0                                                       | R   |              | 90          | * * | * | *   | *   | _ | - | 2              | 2               |

|              |                                                                          | IR  |              | 91          |     |   |     |     |   |   | 2              | 3               |

| RLC dst      | C T D7D6D5D4D3D2D1D0<br>dst                                              | R   |              | 10          | * * | * | *   | _   | _ | 2 | 2              |                 |

|              |                                                                          | IR  |              | 11          |     |   |     |     |   |   | 2              | 3               |

| RR dst       |                                                                          | R   |              | E0          | *   | * | *   | *   | _ | _ | 2              | 2               |

|              | ► D7 D6 D5 D4 D3 D2 D1 D0 C<br>dst                                       | IR  |              | E1          |     |   |     |     |   |   | 2              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# **Opcode Maps**

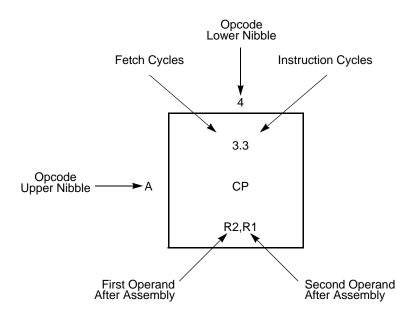

A description of the opcode map data and the abbreviations are provided in Figure 30. Figures 31 and 32 display the eZ8 CPU instructions. Table 129 lists Opcode Map abbreviations.

Figure 30. Opcode Map Cell Description

| Abbreviation | Description                         | Abbreviation                                      | Description             |

|--------------|-------------------------------------|---------------------------------------------------|-------------------------|

| b            | Bit position.                       | IRR                                               | Indirect register pair. |

| СС           | Condition code.                     | р                                                 | Polarity (0 or 1).      |

| Х            | 8-bit signed index or displacement. | r                                                 | 4-bit working register. |

| DA           | Destination address.                | R                                                 | 8-bit register.         |

| ER           | Extended addressing register.       | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address.    |

| IM           | Immediate data value.               | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address.         |

| Ir           | Indirect working register.          | RA                                                | Relative.               |

| IR           | Indirect register.                  | rr                                                | Working register pair.  |

| Irr          | Indirect working register pair.     | RR                                                | Register pair.          |

#### Table 129. Opcode Map Abbreviations

## **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 135 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                  | T <sub>A</sub> = | –40°C to +′          |         |       |                                                                                                             |  |

|------------------|------------------------------------------------------------------|------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                        | Minimum          | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                                  |  |

| V <sub>POR</sub> | Power-On Reset Voltage Thresh-<br>old                            | 2.20             | 2.45                 | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                          |  |

| V <sub>VBO</sub> | Voltage Brown-Out Reset Voltage<br>Threshold                     | 2.15             | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                          |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                  |                  | 50                   | 75      | mV    |                                                                                                             |  |

|                  | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset. | -                | $V_{SS}$             | -       | V     |                                                                                                             |  |

| T <sub>ANA</sub> | Power-On Reset Analog Delay                                      | -                | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay<br>follows T <sub>ANA</sub> |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> )             |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator disabled              |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles                                                            |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator enabled               |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>VBO</sub> | Voltage Brown-Out Pulse Rejec-<br>tion Period                    | _                | 10                   | _       | μs    | Period of time<br>in which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.                             |  |

Note: Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

# Index

## **Numerics**

10-bit ADC 6

## Α

absolute maximum ratings 226 AC characteristics 232 ADC 208 architecture 124 block diagram 125 continuous conversion 127 control register 134, 135 control register definitions 133 data high byte register 136 data low bits register 137 electrical characteristics and timing 236 operation 125 single-shot conversion 126 ADCCTL register 134, 135 ADCDH register 136 ADCDL register 137 **ADCX 208** ADD 208 add - extended addressing 208 add with carry 208 add with carry - extended addressing 208 additional symbols 207 address space 15 **ADDX 208** analog signals 11 analog-to-digital converter (ADC) 124 AND 210 **ANDX 210** arithmetic instructions 208 assembly language programming 204 assembly language syntax 205

## В

B 207

**BCLR 209** binary number suffix 207 **BIT 209** bit 206 clear 209 manipulation instructions 209 set 209 set or clear 209 swap 209 test and jump 211 test and jump if non-zero 211 test and jump if zero 211 bit jump and test if non-zero 211 bit swap 211 block diagram 3 block transfer instructions 209 **BRK 211 BSET 209** BSWAP 209, 211 BTJ 211 BTJNZ 211 **BTJZ 211**

baud rate generator, UART 110

## С

b 206

CALL procedure 211 CAPTURE mode 87, 88 CAPTURE/COMPARE mode 88 cc 206 CCF 209 characteristics, electrical 226 clear 210 CLR 210 COM 210 compare 87 compare - extended addressing 208 COMPARE mode 87 compare with carry 208

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.