# E·XFL

#### Zilog - Z8F082AHJ020EG2156 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 23                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082ahj020eg2156 |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Revision History                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                        |

| List of Tables                                                                                                                                                                                         |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview410-Bit Analog-to-Digital Converter4Low-Power Operational Amplifier4Internal Precision Oscillator5Temperature Sensor5  |

| Analog Comparator5External Crystal Oscillator5Low Voltage Detector5On-Chip Debugger5Universal Asynchronous Receiver/Transmitter5Timers5General-Purpose Input/Output6Direct LED Drive6Flash Controller6 |

| Non-Volatile Data Storage       6         Interrupt Controller       6         Reset Controller       6                                                                                                |

| Pin Description8Available Packages8Pin Configurations8Signal Descriptions10Pin Characteristics12                                                                                                       |

| Address Space15Register File15Program Memory15Data Memory17Flash Information Area17                                                                                                                    |

| Register Map                                                                                                                                                                                           |

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 119. | Additional Symbols 207                                                |

|------------|-----------------------------------------------------------------------|

| Table 120. | Arithmetic Instructions                                               |

| Table 121. | Bit Manipulation Instructions                                         |

| Table 122. | Block Transfer Instructions                                           |

| Table 123. | CPU Control Instructions                                              |

| Table 124. | Load Instructions                                                     |

| Table 125. | Logical Instructions                                                  |

| Table 126. | Program Control Instructions 211                                      |

| Table 127. | Rotate and Shift Instructions 211                                     |

| Table 128. | eZ8 CPU Instruction Summary 212                                       |

| Table 129. | Opcode Map Abbreviations 223                                          |

| Table 130. | Absolute Maximum Ratings 226                                          |

| Table 131. | DC Characteristics                                                    |

| Table 132. | Power Consumption                                                     |

| Table 133. | AC Characteristics                                                    |

| Table 134. | Internal Precision Oscillator Electrical Characteristics              |

| Table 135. | Power-On Reset and Voltage Brown-Out Electrical Characteristics       |

|            | and Timing 233                                                        |

| Table 136. | Flash Memory Electrical Characteristics and Timing 234                |

| Table 137. | Watchdog Timer Electrical Characteristics and Timing 235              |

| Table 138. | Non-Volatile Data Storage                                             |

| Table 139. | Analog-to-Digital Converter Electrical Characteristics and Timing 236 |

| Table 140. | Low Power Operational Amplifier Electrical Characteristics 238        |

| Table 141. | Comparator Electrical Characteristics                                 |

| Table 142. | Temperature Sensor Electrical Characteristics                         |

| Table 143. | GPIO Port Input Timing                                                |

| Table 144. | GPIO Port Output Timing                                               |

| Table 145. | On-Chip Debugger Timing                                               |

| Table 146. | UART Timing With CTS                                                  |

| Table 147. | UART Timing Without CTS 244                                           |

| Table 148. | Z8 Encore! XP F082A Series Ordering Matrix                            |

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

## Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

## **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

## **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

## **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See the <u>Pin Configurations</u> section on page 8 to determine the signals available for the specific package styles.

| Signal Mnemonic               | I/O | Description                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| General-Purpose I/O Ports A–D |     |                                                                                                                                                                                                                                                                                                         |  |  |  |

| PA[7:0]                       | I/O | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |

| PB[7:0]                       | I/O | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |  |  |  |

| PC[7:0]                       | I/O | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |  |  |  |

| PD[0]                         | I/O | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |  |  |  |

| UART Controllers              |     |                                                                                                                                                                                                                                                                                                         |  |  |  |

| TXD0                          | 0   | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |  |  |  |

| RXD0                          | Ι   | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |  |  |  |

| CTS0                          | Ι   | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |  |  |  |

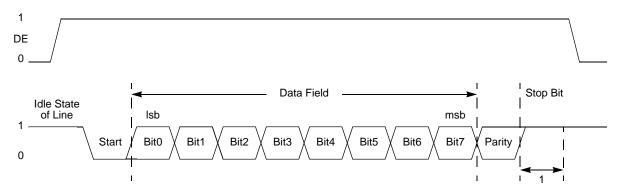

| DE                            | 0   | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |  |  |  |

| Timers                        |     |                                                                                                                                                                                                                                                                                                         |  |  |  |

| T0OUT/T1OUT                   | 0   | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |  |  |  |

| T0OUT/T1OUT                   | 0   | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |  |  |  |

| T0IN/T1IN                     | Ι   | Timer Input 0–1. These signals are used as the capture, gating and coun-<br>ter inputs.                                                                                                                                                                                                                 |  |  |  |

| Comparator                    |     |                                                                                                                                                                                                                                                                                                         |  |  |  |

| CINP/CINN                     | Ι   | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |  |  |  |

| COUT                          | 0   | Comparator Output.                                                                                                                                                                                                                                                                                      |  |  |  |

#### **Table 2. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

| Signal Mnemonic  | I/O | Description                                                                                                                                                                                                           |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset            |     |                                                                                                                                                                                                                       |

| RESET            | I/O | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply     |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>  | Ι   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>  | Ι   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub> | Ι   | Analog Ground.                                                                                                                                                                                                        |

| Notes:           |     |                                                                                                                                                                                                                       |

#### Table 2. Signal Descriptions (Continued)

inotes

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

## **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note: All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

| Address (Hex)    | Register Description                 | Mnemonic      | Reset (Hex) | Page       |

|------------------|--------------------------------------|---------------|-------------|------------|

| Timer 1          |                                      |               |             |            |

| F08              | Timer 1 High Byte                    | T1H           | 00          | <u>90</u>  |

| F09              | Timer 1 Low Byte                     | T1L           | 01          | <u>90</u>  |

| F0A              | Timer 1 Reload High Byte             | T1RH          | FF          | <u>91</u>  |

| Timer 1 (cont'd) |                                      |               |             |            |

| F0B              | Timer 1 Reload Low Byte              | T1RL          | FF          | <u>91</u>  |

| F0C              | Timer 1 PWM High Byte                | T1PWMH        | 00          | <u>92</u>  |

| F0D              | Timer 1 PWM Low Byte                 | T1PWML        | 00          | <u>92</u>  |

| F0E              | Timer 1 Control 0                    | T1CTL0        | 00          | <u>85</u>  |

| F0F              | Timer 1 Control 1                    | T1CTL1        | 00          | <u>86</u>  |

| F10–F6F          | Reserved                             | —             | XX          |            |

| UART             |                                      |               |             |            |

| F40              | UART Transmit/Receive Data registers | TXD, RXD      | XX          | <u>115</u> |

| F41              | UART Status 0 Register               | U0STAT0       | 00          | <u>114</u> |

| F42              | UART Control 0 Register              | U0CTL0        | 00          | <u>110</u> |

| F43              | UART Control 1 Register              | U0CTL1        | 00          | <u>110</u> |

| F44              | UART Status 1 Register               | U0STAT1       | 00          | <u>115</u> |

| F45              | UART Address Compare Register        | <b>U0ADDR</b> | 00          | <u>116</u> |

| F46              | UART Baud Rate High Byte Register    | U0BRH         | FF          | <u>117</u> |

| F47              | UART Baud Rate Low Byte Register     | U0BRL         | FF          | <u>117</u> |

| Analog-to-Digita | al Converter (ADC)                   |               |             |            |

| F70              | ADC Control 0                        | ADCCTL0       | 00          | <u>134</u> |

| F71              | ADC Control 1                        | ADCCTL1       | 80          | <u>136</u> |

| F72              | ADC Data High Byte                   | ADCD_H        | XX          | <u>137</u> |

| F73              | ADC Data Low Byte                    | ADCD_L        | XX          | 137        |

| F74–F7F          | Reserved                             |               | XX          |            |

| Low Power Con    | trol                                 |               |             |            |

| F80              | Power Control 0                      | PWRCTL0       | 80          | <u>34</u>  |

| F81              | Reserved                             | —             | XX          |            |

| LED Controller   |                                      |               |             |            |

| F82              | LED Drive Enable                     | LEDEN         | 00          | <u>53</u>  |

| F83              | LED Drive Level High Byte            | LEDLVLH       | 00          | <u>53</u>  |

| F84              | LED Drive Level Low Byte             | LEDLVLL       | 00          | <u>54</u>  |

#### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

**Note:** Asserting any power control bit disables the targeted block regardless of any enable bits contained in the target block's control registers.

>

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit     | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|------|------|-------|-----|------|------|------|------|

| Field   |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H |      |       |     |      |      |      |      |

| Table 37. | Interrupt | Request 2 | Register | (IRQ2) |

|-----------|-----------|-----------|----------|--------|

|-----------|-----------|-----------|----------|--------|

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [7:4]   | Reserved                                                             |  |

|         | These bits are reserved and must be programmed to 0000.              |  |

| [3:0]   | Port C Pin <i>x</i> Interrupt Request                                |  |

| PCxI    | 0 = No interrupt request is pending for GPIO Port C pin $x$ .        |  |

|         | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: x | c indicates the specific GPIO Port C pin number (0–3).               |  |

## **IRQ0 Enable High and Low Bit Registers**

Table 38 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register.

| IRQ0ENH[x]                           | IRQ0ENL[x] | Priority | Description |  |  |

|--------------------------------------|------------|----------|-------------|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |

Table 38. IRQ0 Enable and Priority Encoding

| Bit     | 7       | 6                           | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|-----------------------------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENH | PA6CENH                     | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0       | 0                           | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W R/W R/W R/W R/W R/W R/W |        |        |               |        |        |        |

| Address |         | FC4H                        |        |        |               |        |        |        |

| Bit             | Description                                                   |

|-----------------|---------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] or LVD Interrupt Request Enable High Bit        |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit |

| [5:0]<br>PAxENH | Port A Bit[ <i>x</i> ] Interrupt Request Enable High Bit      |

See the <u>Shared Interrupt Select Register (IRQSS) Register</u> on page 68 for selection of either the LVD or the comparator as the interrupt source.

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |         | FC5H    |        |        |               |        |        |        |

| Bit             | Description                                                  |

|-----------------|--------------------------------------------------------------|

| [7]<br>PA7VENL  | Port A Bit[7] or LVD Interrupt Request Enable Low Bit        |

| [6]<br>PA6CENL  | Port A Bit[6] or Comparator Interrupt Request Enable Low Bit |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |

### **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 44 and 45, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register. The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

#### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, plus the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable-to-Start bit setup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

Rate Generator to function as an additional counter if the UART functionality is not employed.

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

## **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

### **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

#### **Compensation Steps:**

1. Correct for Offset:

| ADC MSB    | ADC LSB    |  |  |

|------------|------------|--|--|

| _          |            |  |  |

| Offset MSB | Offset LSB |  |  |

| =          |            |  |  |

| #1 MSB     | #1 LSB     |  |  |

|            |            |  |  |

2. Compute the absolute value of the offset-corrected ADC value *if negative*; the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB | #2 LSB |

|--------|--------|

|--------|--------|

Also compute the absolute value of the gain correction word, if negative.

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by the Gain Correction Word. If operating in DIFFERENTIAL Mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Use the appropriate Gain Correction Word based on the sign computed by byte #2.

| #2 MSB | #2 LSB |

|--------|--------|

|        |        |

| AGain MSB | AGain LSB |

|-----------|-----------|

|           |           |

=

The following code example illustrates how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

nop         ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definition**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit     | 7      | 6      | 5      | 4   | 3   | 2   | 1                                       | 0   |

|---------|--------|--------|--------|-----|-----|-----|-----------------------------------------|-----|

| Field   | INPSEL | INNSEL | REFLVL |     |     |     | Reserved (20-/28-pin)<br>REFLVL (8-pin) |     |

| RESET   | 0      | 0      | 0      | 1   | 0   | 1   | 0                                       | 0   |

| R/W     | R/W    | R/W    | R/W    | R/W | R/W | R/W | R/W                                     | R/W |

| Address |        | F90H   |        |     |     |     |                                         |     |

Table 77. Comparator Control Register (CMP0)

| Bit    | Description                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]    | Signal Select for Positive Input                                                                                                                                       |

| INPSEL | 0 = GPIO pin used as positive comparator input.                                                                                                                        |

|        | 1 = Temperature sensor used as positive comparator input.                                                                                                              |

| [6]    | Signal Select for Negative Input                                                                                                                                       |

| INNSEL | <ul> <li>0 = Internal reference disabled, GPIO pin used as negative comparator input.</li> <li>1 = Internal reference enabled as negative comparator input.</li> </ul> |

# Flash Memory

The products in the Z8 Encore! XP F082A Series feature a nonvolatile Flash memory of 8KB (8192), 4 KB (4096), 2 KB (2048 bytes), or 1 KB (1024) with read/write/erase capability. The Flash Memory can be programmed and erased in-circuit by user code or through the On-Chip Debugger. The features include:

- User controlled read and write protect capability

- Sector-based write protection scheme

- Additional protection schemes against accidental program and erasure

#### Architecture

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program or data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F082A Series, these sectors are either 1024 bytes (in the 8KB devices) or 512 bytes (all other memory sizes) in size. Page and sector sizes are not generally equal.

The first 2 bytes of Flash Program memory are used as Flash option bits. For more information about their operation, see the <u>Flash Option Bits</u> chapter on page 159.

Table 78 describes the Flash memory configuration for each device in the Z8 Encore! XP F082A Series. Figure 21 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (Bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08xA     | 8 (8192)                 | 16             | 0000H-1FFFH                 | 1024                         |

| Z8F04xA     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02xA     | 2 (2048)                 | 4              | 0000H-07FFH                 | 512                          |

| Z8F01xA     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

Table 78. Z8 Encore! XP F082A Series Flash Memory Configurations

Serial Break leaves the device in DEBUG Mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

## OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

- Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the <u>On-Chip Debugger Commands</u> section on page 186).

- **Caution:** Between <u>Steps 3</u> and <u>4</u>, there is an interval during which the 8-pin device is neither in RE-SET nor DEBUG Mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this value as an illegal instruction; therefore some irregular behavior can occur before entering DEBUG Mode, and the register values after entering DEBUG Mode will differ from their specified reset values. However, none of these irregularities prevent the programming of Flash memory. Before beginning system debug, Zilog recommends that some legal code be programmed into the 8-pin device and that a RESET occurs.

### **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If Breakpoints are not

in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

## **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP F082A Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

| Bit   | 7       | 6     | 5      | 4        | 3 | 2 | 1 | 0   |

|-------|---------|-------|--------|----------|---|---|---|-----|

| Field | DBGMODE | BRKEN | DBGACK | Reserved |   |   |   | RST |

| RESET | 0       | 0     | 0      | 0        | 0 | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R        | R | R | R | R/W |

Table 110. OCD Control Register (OCDCTL)

#### Bit Description

#### [7] **DEBUG Mode** DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0. 0 = The Z8 Encore! XP F082A Series device is operating in NORMAL Mode. 1 = The Z8 Encore! XP F082A Series device is in DEBUG Mode. [6] **Breakpoint Enable** BRKEN This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL Register is automatically set to 1. 0 = Breakpoints are disabled. 1 = Breakpoints are enabled.

|                                                        | V <sub>DD</sub> = 2.7 V to 3.6 V                                                                                                                                                                         |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                                                                                                         | Conditions                                                                                                                                                                                                                                                                                                                      |  |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                                                                            | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |  |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                                                                            | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |

| Band Gap Supply<br>Current                             | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                                                                            | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |  |

|                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                               | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |  |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ParameterTypical1Maximum<br>Std Temp2Maximum<br>Ext Temp3ADC Internal Ref-<br>erence Supply Cur-<br>rent000Comparator sup-<br>ply Current150180190Low-Power Opera-<br>tional Amplifier<br>Supply Current355Temperature Sen-<br>sor Supply Current6000Band Gap Supply320480500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |  |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

#### 240

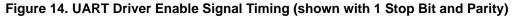

#### General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### Figure 34. Port Input Sample Timing

#### Table 143. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1 μs       |         |  |

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.