Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | - ·                                                          |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | - · · · · · · · · · · · · · · · · · · ·                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082aph020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

### Features

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20MHz

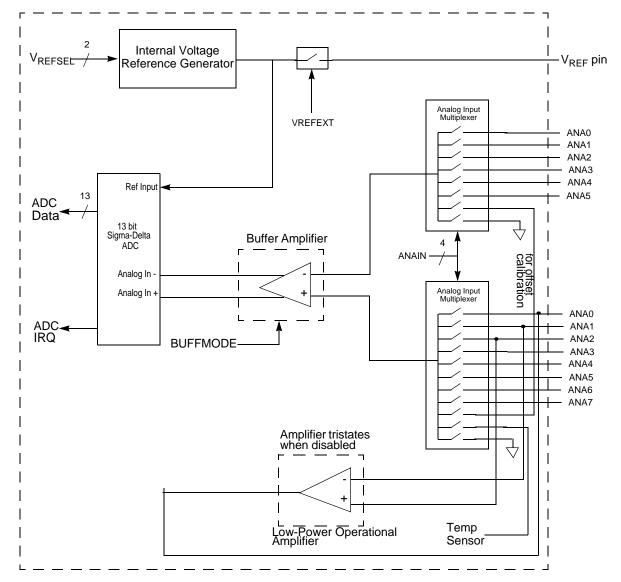

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| Bit     | 7          | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------------|------------------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   | PADDR[7:0] |                        |     |     |     |     |     |     |  |  |

| RESET   |            | 00H                    |     |     |     |     |     |     |  |  |

| R/W     | R/W        | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |            | FD0H, FD4H, FD8H, FDCH |     |     |     |     |     |     |  |  |

### Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit                                                                                                                                                                 | Description  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| []                                                                                                                                                                  | Port Address |  |  |  |  |  |  |  |

| PADDRx The Port Address selects one of the subregisters accessible through the Port Control Register.<br>Note: x indicates the specific GPIO port pin number (7–0). |              |  |  |  |  |  |  |  |

### Table 19. Port A–D GPIO Address Registers by Bit Description

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control Registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

## Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                            | 4                                              | 3              | 2           | 1            | 0          |  |  |

|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------|----------------|-------------|--------------|------------|--|--|

| Field          | TMODEHI             | TICONFIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              | Reserved                                       |                | PWMD        |              | INPCAP     |  |  |

| RESET          | 0                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                            | 0                                              | 0              | 0           | 0            | 0          |  |  |

| R/W            | R/W                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                          | R/W                                            | R/W            | R/W         | R/W          | R          |  |  |

| Address        |                     | F06H, F0EH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                                                |                |             |              |            |  |  |

| Bit            | Descript            | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                                                |                |             |              |            |  |  |

| [7]<br>TMODEHI | This bit, a mode of | the timer. The timer the timer the time | ne TMODE f<br>nis bit is the | field in the T<br>most signific<br>Control Reg | cant bit of th | e Timer moo | de selection | value. See |  |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

### Bit Description (Continued)

### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the Timer Input signal.

- 1 = Count occurs on the falling edge of the Timer Input signal.

### **PWM SINGLE OUTPUT Mode**

- 0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload.

- 1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload.

### CAPTURE Mode

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

### COMPARE Mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TH         |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     | F00H, F08H |     |     |     |     |     |     |  |  |  |

### Table 52. Timer 0–1 High Byte Register (TxH)

### Table 53. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|---------|-----|-----|-----|-------|------|-----|-----|-----|--|--|

| Field   | TL  |     |     |       |      |     |     |     |  |  |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |  |  |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| Address |     |     |     | F01H, | F09H |     |     |     |  |  |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

| Bit          | 7                                                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                                                                               | 4                                                                                                                       | 3                                                                                                        | 2                                                                        | 1                                                              | 0                         |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------|--|--|--|

| Field        | MPMD[1]                                                                                               | MPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MPMD[0]                                                                                                                                         | MPBT                                                                                                                    | DEPOL                                                                                                    | BRGCTL                                                                   | RDAIRQ                                                         | IREN                      |  |  |  |

| RESET        | 0                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                               | 0                                                                                                                       | 0                                                                                                        | 0                                                                        | 0                                                              | 0                         |  |  |  |

| R/W          | R/W                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                             | R/W                                                                                                                     | R/W                                                                                                      | R/W                                                                      | R/W                                                            | R/W                       |  |  |  |

| Address      |                                                                                                       | F43H                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |                                                                                                                         |                                                                                                          |                                                                          |                                                                |                           |  |  |  |

| Bit          | Descript                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |                                                                                                                         |                                                                                                          |                                                                          |                                                                |                           |  |  |  |

| [6]<br>MPEN  | 01 = The<br>10 = The<br>valu<br>an a<br>11 = The<br>reco<br><b>MULTIP</b><br>This bit is<br>0 = Disal | UART gen<br>UART gen<br>ue stored in<br>address mis<br>UART gen<br>ent address<br><b>ROCESSO</b> I<br>s used to er<br>ble MULTIP                                                                                                                                                                                                                                                                                                                              | erates an inf<br>erates an inf<br>the Address<br>match occur<br>erates an int<br>byte matche<br><b>R (9-bit) Ena</b><br>nable MULTI<br>ROCESSOF | terrupt reque<br>terrupt reque<br>compare R<br>rs.<br>errupt reque<br>ed the value<br>able<br>PROCESSC<br>R (9-bit) Moc | est only on r<br>est when a r<br>Register and<br>est on all reco<br>in the Addro<br>DR (9-bit) Mo<br>le. | eceived add<br>eceived add<br>on all succe<br>eived data b<br>ess Compar | lress bytes.<br>lress byte m<br>essive data b<br>ytes for whic | atches the<br>oytes until |  |  |  |

| [4]<br>MPBT  | Multipro<br>This bit is<br>used by<br>tion.<br>0 = Send                                               | <ul> <li>1 = Enable MULTIPROCESSOR (9-bit) Mode.</li> <li>Multiprocessor Bit Transmit This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data informa- tion. 0 = Send a 0 in the multiprocessor bit location of the data stream (data byte). 1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li></ul> |                                                                                                                                                 |                                                                                                                         |                                                                                                          |                                                                          |                                                                |                           |  |  |  |

| [3]<br>DEPOL | <b>Driver E</b><br>0 = DE s                                                                           | <ul> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> <li>Driver Enable Polarity</li> <li>0 = DE signal is Active High.</li> <li>1 = DE signal is Active Low.</li> </ul>                                                                                                                                                                                                                                           |                                                                                                                                                 |                                                                                                                         |                                                                                                          |                                                                          |                                                                |                           |  |  |  |

### Table 64. UART Control 1 Register (U0CTL1)

| Bit       | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-----------|------------|---|---|----|----|---|---|---|--|--|

| Field     | TXD        |   |   |    |    |   |   |   |  |  |

| RESET     | Х          | Х | Х | Х  | Х  | Х | Х | Х |  |  |

| R/W       | W          | W | W | W  | W  | W | W | W |  |  |

| Address   | 1          |   |   | F4 | OH | I | I |   |  |  |

| Note: X = | Undefined. |   |   |    |    |   |   |   |  |  |

### Table 67. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68 | . UART | Receive | Data | Register | (U0RXD) |

|----------|--------|---------|------|----------|---------|

|----------|--------|---------|------|----------|---------|

| Bit                  | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|----------------------|------------|---|---|---|---|---|---|---|--|--|--|--|

| Field                | RXD        |   |   |   |   |   |   |   |  |  |  |  |

| RESET                | Х          | Х | Х | Х | Х | Х | Х | Х |  |  |  |  |

| R/W                  | R          | R | R | R | R | R | R | R |  |  |  |  |

| Address              | F40H       |   |   |   |   |   |   |   |  |  |  |  |

| Note: X = Undefined. |            |   |   |   |   |   |   |   |  |  |  |  |

| Bit                  | Descriptio | n |   |   |   |   |   |   |  |  |  |  |

| Dit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

### **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

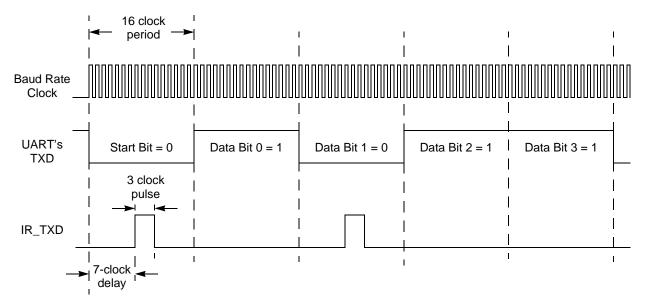

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

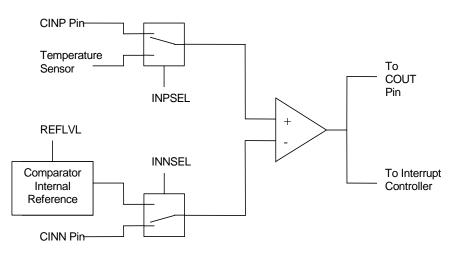

# **Comparator**

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | FF | 8H |   |   |   |

### Table 80. Flash Control Register (FCTL)

| Bit Description |

|-----------------|

|-----------------|

[7:0] Flash Command

FCMD 73H = First unlock command.

8CH = Second unlock command.

95H = Page Erase command (must be third command in sequence to initiate Page Erase).

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase).

5EH = Enable Flash Sector Protect Register Access

### Flash Status Register

The Flash Status (FSTAT) Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the Write-only Flash Control Register.

### Table 81. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5 | 4  | 3  | 2   | 1 | 0 |

|---------|------|-------|---|----|----|-----|---|---|

| Field   | Rese | erved |   |    | FS | TAT |   |   |

| RESET   | 0    | 0     | 0 | 0  | 0  | 0   | 0 | 0 |

| R/W     | R    | R     | R | R  | R  | R   | R | R |

| Address |      |       |   | FF | 8H |     |   |   |

| Bit            | Description                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]          | These bits are reserved and must be programmed to 00.                                                                                                                                                                                            |

| [5:0]<br>FSTAT | Flash Controller Status000000 = Flash Controller locked.000001 = First unlock command received (73H written).000010 = Second unlock command received (8CH written).000011 = Flash Controller unlocked.000100 = Sector protect register selected. |

|                | 001xxx = Program operation in progress.<br>010xxx = Page erase operation in progress.<br>100xxx = Mass erase operation in progress.                                                                                                              |

## **Flash Page Select Register**

The Flash Page Select (FPS) Register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

| Bit     | 7       | 6   |     |     |      |     |     |     |  |  |

|---------|---------|-----|-----|-----|------|-----|-----|-----|--|--|

| Field   | INFO_EN |     |     |     | PAGE |     |     |     |  |  |

| RESET   | 0       | 0   | 0   | 0   | 0    | 0   | 0   | 0   |  |  |

| R/W     | R/W     | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |  |  |

| Address |         |     |     | FF  | 9H   |     |     |     |  |  |

### Table 82. Flash Page Select Register (FPS)

#### Bit Description

### [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

# **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        |        |        | FF     | 9H     |        |        |        |

Table 83. Flash Sector Protect Register (FPROT)

### Bit Description

### [7:0] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

# **On-Chip Debugger**

The Z8 Encore! XP F082A Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features including:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize pins available to the user (8-pin product only)

# Architecture

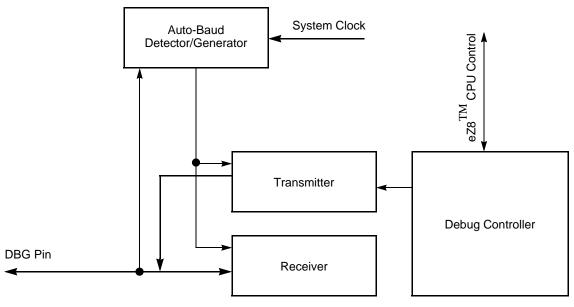

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator and debug controller. Figure 23 displays the architecture of the on-chip debugger.

Figure 23. On-Chip Debugger Block Diagram

the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry and all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

# **Oscillator Control Register Definitions**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Unlock the Oscillator Control Register by writing the two-step sequence E7H followed by 18H. The register is locked at successful completion of a register write to the OSCCTL.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |  |  |  |  |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|--|--|--|--|

| Field   | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL |     |     |  |  |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0 0 0  |     |     |  |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |  |  |  |

| Address |       |       |       | F8    | 6H    |        |     |     |  |  |  |  |

Table 113. Oscillator Control Register (OSCCTL)

| Bit          | Description                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                             |

| [6]<br>XTLEN | Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled.                            |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                         |

| [4]<br>SOFEN | System Clock Oscillator Failure Detection Enable1 = Failure detection and recovery of system clock oscillator is enabled.0 = Failure detection and recovery of system clock oscillator is disabled. |

| Assembly     |                                                                                                                   |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src         | (Hex)       |   | Ζ | S   | V   | D | Н | S              | S               |

| DA dst       | $dst \gets DA(dst)$                                                                                               | R   |             | 40          | * | * | *   | Х   | _ | _ | 2              | 2               |

|              |                                                                                                                   | IR  |             | 41          | = |   |     |     |   |   | 2              | 3               |

| DEC dst      | dst ← dst - 1                                                                                                     | R   |             | 30          | _ | * | *   | *   | _ | _ | 2              | 2               |

|              |                                                                                                                   | IR  |             | 31          | - |   |     |     |   |   | 2              | 3               |

| DECW dst     | dst ← dst - 1                                                                                                     | RR  |             | 80          | - | * | *   | *   | - | - | 2              | 5               |

|              |                                                                                                                   | IRR |             | 81          | - |   |     |     |   |   | 2              | 6               |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                          |     |             | 8F          | - | - | -   | -   | - | - | 1              | 2               |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |             | 0A-FA       | _ | _ | _   | _   | _ | - | 2              | 3               |

| EI           | $IRQCTL[7] \leftarrow 1$                                                                                          |     |             | 9F          | - | - | -   | -   | - | - | 1              | 2               |

| HALT         | Halt Mode                                                                                                         |     |             | 7F          | - | _ | _   | _   | - | - | 1              | 2               |

| INC dst      | dst ← dst + 1                                                                                                     | R   |             | 20          | - | * | *   | _   | _ | - | 2              | 2               |

|              |                                                                                                                   | IR  |             | 21          | - |   |     |     |   |   | 2              | 3               |

|              |                                                                                                                   | r   |             | 0E-FE       | - |   |     |     |   |   | 1              | 2               |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |             | A0          | - | * | *   | *   | - | - | 2              | 5               |

|              |                                                                                                                   | IRR |             | A1          | - |   |     |     |   |   | 2              | 6               |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |             | BF          | * | * | *   | *   | * | * | 1              | 5               |

| JP dst       | $PC \leftarrow dst$                                                                                               | DA  |             | 8D          | - | _ | _   | _   | _ | - | 3              | 2               |

|              |                                                                                                                   | IRR |             | C4          | = |   |     |     |   |   | 2              | 3               |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                              | DA  |             | 0D-FD       | _ | _ | _   | _   | _ | _ | 3              | 2               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly      |                                         |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|-----------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation                      | dst | src         | (Hex)       | С | Ζ | S   | ۷   | D | Н | S              | S               |

| RRC dst       |                                         | R   |             | C0          | * | * | *   | *   | _ | _ | 2              | 2               |

|               | ► <u>D7D6D5D4D3D2D1D0</u> ►_C<br>dst    | IR  |             | C1          |   |   |     |     |   |   | 2              | 3               |

| SBC dst, src  | $dst \gets dst - src - C$               | r   | r           | 32          | * | * | *   | *   | 1 | * | 2              | 3               |

|               | =                                       | r   | lr          | 33          |   |   |     |     |   |   | 2              | 4               |

|               | -                                       | R   | R           | 34          |   |   |     |     |   |   | 3              | 3               |

|               | -                                       | R   | IR          | 35          |   |   |     |     |   |   | 3              | 4               |

|               | -                                       | R   | IM          | 36          |   |   |     |     |   |   | 3              | 3               |

|               | -                                       | IR  | IM          | 37          |   |   |     |     |   |   | 3              | 4               |

| SBCX dst, src | $dst \gets dst - src - C$               | ER  | ER          | 38          | * | * | *   | *   | 1 | * | 4              | 3               |

|               | -                                       | ER  | IM          | 39          |   |   |     |     |   |   | 4              | 3               |

| SCF           | C ← 1                                   |     |             | DF          | 1 | - | _   | _   | _ | - | 1              | 2               |

| SRA dst       |                                         | R   |             | D0          | * | * | *   | 0   | - | - | 2              | 2               |

|               | $- D7 D6 D5 D4 D3 D2 D1 D0 - C^{-}$ dst | IR  |             | D1          |   |   |     |     |   |   | 2              | 3               |

| SRL dst       | 0 - D7D6D5D4D3D2D1D0 - C                | R   |             | 1F C0       | * | * | 0   | *   | _ | _ | 3              | 2               |

|               | dst                                     | IR  |             | 1F C1       |   |   |     |     |   |   | 3              | 3               |

| SRP src       | RP ← src                                |     | IM          | 01          | _ | _ | _   | _   | _ | _ | 2              | 2               |

| STOP          | STOP Mode                               |     |             | 6F          | _ | _ | _   | _   | _ | _ | 1              | 2               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

219

| Abbreviation | Description                         | Abbreviation                                      | Description             |

|--------------|-------------------------------------|---------------------------------------------------|-------------------------|

| b            | Bit position.                       | IRR                                               | Indirect register pair. |

| СС           | Condition code.                     | р                                                 | Polarity (0 or 1).      |

| Х            | 8-bit signed index or displacement. | r                                                 | 4-bit working register. |

| DA           | Destination address.                | R                                                 | 8-bit register.         |

| ER           | Extended addressing register.       | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address.    |

| IM           | Immediate data value.               | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address.         |

| Ir           | Indirect working register.          | RA                                                | Relative.               |

| IR           | Indirect register.                  | rr                                                | Working register pair.  |

| Irr          | Indirect working register pair.     | RR                                                | Register pair.          |

### Table 129. Opcode Map Abbreviations

# Index

## **Numerics**

10-bit ADC 6

# Α

absolute maximum ratings 226 AC characteristics 232 ADC 208 architecture 124 block diagram 125 continuous conversion 127 control register 134, 135 control register definitions 133 data high byte register 136 data low bits register 137 electrical characteristics and timing 236 operation 125 single-shot conversion 126 ADCCTL register 134, 135 ADCDH register 136 ADCDL register 137 **ADCX 208** ADD 208 add - extended addressing 208 add with carry 208 add with carry - extended addressing 208 additional symbols 207 address space 15 **ADDX 208** analog signals 11 analog-to-digital converter (ADC) 124 AND 210 **ANDX 210** arithmetic instructions 208 assembly language programming 204 assembly language syntax 205

# В

B 207

**BCLR 209** binary number suffix 207 **BIT 209** bit 206 clear 209 manipulation instructions 209 set 209 set or clear 209 swap 209 test and jump 211 test and jump if non-zero 211 test and jump if zero 211 bit jump and test if non-zero 211 bit swap 211 block diagram 3 block transfer instructions 209 **BRK 211 BSET 209** BSWAP 209, 211 BTJ 211 BTJNZ 211 **BTJZ 211**

baud rate generator, UART 110

# С

b 206

CALL procedure 211 CAPTURE mode 87, 88 CAPTURE/COMPARE mode 88 cc 206 CCF 209 characteristics, electrical 226 clear 210 CLR 210 COM 210 compare 87 compare - extended addressing 208 COMPARE mode 87 compare with carry 208

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**