Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | ·                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                     |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082apj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Overview

Zilog's Z8 Encore! MCU family of products eathe first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bitcrocontrollers. The Flash in-circuit programming capability allows for faster developent time and program ashges in the field. The new eZ8 CPU is upward compatible witlisting Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series maikessitable for a variety of applications including motor control, secitly systems, home appliances; rsonal electronic devices and sensors.

# Features

The key features of Z8 Encore! XP F082A Series products include:

- 20 MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memonyith in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillatorimmed to ±1% accuracy

- External crystal oscillatopperating up to 20 MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers withapture, comparend PWM capability

- Watchdog Timer (WDT) with decated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

# **Address Space**

The eZ8 CPU can access the followthgee distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral and general-pose I/O port control registers.

- The Program Memory contains addresses for memory locations having executable code and/or data.

- The Data Memory contains addresses formelmory locations that contain data only.

These three address spaces are coveredly bine he following subsections. For more information about eZ8 CPU and its address space, refer ez8hePU Core User Manual (UM0128), which is available for download onww.zilog.com

# **Register File**

The Register File address space in the Z8 Encore! MCU is 4 KB (4096 bytes). The Register File is composed of two sections: conteglisters and general-purpose registers. When instructions are executed, registers defined as sources are read and registers defined as destinations are written. The architecture ez8 CPU allows adjeneral-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals and to phorts. These registers are located at addresses from 00H to FFFH. Some of the addresses within 256 B control register section are reserved (unavailable). Reading faoreserved Register File address returns an undefined value. Writing trasserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address H in the Register File address space. The Z8 Encore!  $XP^{M}$  F082A Series devices contain 256 B to 1 KB of on-chip RAM. Reading from Register File addresses outside the advail RAM addresses (and not within the control register address space) returns an **funde** value. Writing to these Register File addresses produces no effect.

# Program Memory

The eZ8 CPU supports 64 KB of Progr**Memory** address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

# Low-Power Modes

The Z8 Encore! XP F082A Ses products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower leafepower reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented is pabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT Mode).

# **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP Mode, powering down all peripherals except the Voltage Bro@ut detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may alsisabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internate cision oscillator are stopped X and X OUT (if previously enabled) are disabled and PA0/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillatornation us to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timeogic continues to operate

- If enabled for operation in STOP Mode by the sociated Flash option bit, the Voltage Brown-Out protection circuit continues to operate

- Low-power operational amplifier continuescoperate if enabled by the Power Control Register

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $\bigcup_{C}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery and Low Voltage Detection page 22.

| Port                  | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|-----------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1,2</sup> | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                       |     | Reserved   |                                         |                                         |

|                       | PA1 | TOOUT      | Timer 0 Output                          |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA2 | DE0        | UART 0 Driver Enable                    |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA3 | CTS0       | UART 0 Clear to Send                    |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement |                                         |

|                       |     | Reserved   |                                         |                                         |

|                       | PA7 | T1OUT      | Timer 1 Output                          |                                         |

|                       |     | Reserved   |                                         |                                         |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the Port <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

| -                   |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

### Port A–D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A-D antrol Register by writing 5H to the Port A–D Address Register. Setting the bits in the Port A–D Stop de Recovery Source Enable subregisters to 1 configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enables a Stop Mode Recovery source initiates Stop Mode Recovery.

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| Field   | PSMRE7    | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Address | lf 05H ir | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |

#### Bit Description

[7:0] Port Stop Mode Recovery Source Enabled

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–C Input Data Registers

Reading from the Port A–C InpData registers, shown in Table 29, return the sampled values from the correspondingropins. The Port A-C Input Data registers are read-only. The value returned for any unusports is 0. Unused ports include those missing on the 8and 28-pin packages, as well as those missin the ADC-enabled 28-pin packages.

| Bit            | 7                | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|----------------|------------------|------|------|------|------|------|------|------|--|

| Field          | PIN7             | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET          | Х                | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W            | R                | R    | R    | R    | R    | R    | R    | R    |  |

| Address        | FD2H, FD6H, FDAH |      |      |      |      |      |      |      |  |

| X = Undefined. |                  |      |      |      |      |      |      |      |  |

Table 29. Port A–C Input Data Registers (PxIN)

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Output Data Register

The Port A–D Output Data Register, shown ible 30, controls the output data to the pins.

| Bit     | 7                      | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7                  | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0                      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FD3H, FD7H, FDBH, FDFH |       |       |       |       |       |       |       |

Table 30. Port A–D Output Data Register (P xOUT)

#### Bit Description

Port Output Data These bits contain the data to be driven to the port pins. The values are only driven if the corre-PxOUT sponding pin is configured as an output and the pin is not configured for alternate function operation. 0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

[7:0]

• Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

## Interrupt Vectors and Priority

The interrupt controller supportsree levels of interrupt jorrity. Level 3 is the highest priority, Level 2 is the second highest priority level 1 is the lowest priority. If all of the interrupts are enablewith identical interrupt prioty (all as Level 2 interrupts, for example), the interrupt prioty is assigned from highest lowest as specified <u>Trable 34</u> on page 56Level 3 interrupts are always assigning the priority than Level 2 interrupts which, in turn, always are assigned higheority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, duevel 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timerrindet (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Failrap and Illegal Instruction Trap always have highest (level 3) priority.

### Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is not solved by the eZ8 CPU, the corresponding bit in the Interrupt Requere Register is cleared until threat interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Respurce Register likewise clears the interrupt request.

Caution: Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the firstcommand and the final LDX command are lossee Example 1, which follows. The timer input can be used as a select**able**nting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, thereris timer input available.

# **Timer Control Register Definitions**

This section defines the featurestor following Timer Control registers.

<u>Timer 0–1 Control Registersee page 85</u>

<u>Timer 0–1 High and Low Byte Regist</u>essee page 89

Timer Reload High and Low Byte Registesse page 91

Timer 0–1 PWM High and Low Byte Registesse page 92

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating de. These registers each include a programmable PWM deadband delay, two bits to impufe timer interrupt definition and a status bit to identify if the most recent timertierrupt is caused by an input capture event.

| Bit                   | 7                                            | 6                                                                                                                                                                                                                                                                                                                                                                         | 5    | 4        | 3    | 2   | 1   | 0      |  |  |  |

|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|-----|-----|--------|--|--|--|

| Field                 | TMODEHI                                      | TICO                                                                                                                                                                                                                                                                                                                                                                      | NFIG | Reserved | PWMD |     |     | INPCAP |  |  |  |

| RESET                 | 0                                            | 0                                                                                                                                                                                                                                                                                                                                                                         | 0    | 0        | 0    | 0   | 0   | 0      |  |  |  |

| R/W                   | R/W                                          | R/W                                                                                                                                                                                                                                                                                                                                                                       | R/W  | R/W      | R/W  | R/W | R/W | R      |  |  |  |

| Address               |                                              | F06H, F0EH                                                                                                                                                                                                                                                                                                                                                                |      |          |      |     |     |        |  |  |  |

| Bit<br>[7]<br>TMODEHI | Timer Mo<br>This bit,<br>mode of<br>the desc | Description         Timer Mode High Bit         This bit, along with the TMODE field in the TxCTL1 Register, determines the operating         mode of the timer. This bit is the most significant bit of the Timer mode selection value. See         the description of the Timer 0–1 Control Register 1 (TxCTL1) for details about the full timer         mode decoding. |      |          |      |     |     |        |  |  |  |

| Bit            | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:3]<br>PRES  | Prescale value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the Timer is disabled. This reset ensures proper clock division each time the<br>Timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                                                                                                                                                                        |

| [2:0]<br>TMODE | Timer Mode<br>This field, along with the TMODEHI bit in the TxCTL0 Register, determines the operating mode<br>of the timer. TMODEHI is the most significant bit of the Timer mode selection value. The entire<br>operating mode bits are expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the<br>TxCTL0 Register while TMODE[2:0] is the lower 3 bits of the TxCTL1 Register.<br>0000 = ONE-SHOT Mode.<br>0001 = CONTINUOUS Mode.<br>0010 = COUNTER Mode.<br>0011 = PWM SINGLE OUTPUT Mode.<br>0100 = CAPTURE Mode.<br>0110 = GATED Mode.<br>0111 = CAPTURE/COMPARE Mode.<br>1000 = PWM DUAL OUTPUT Mode.<br>1001 = CAPTURE RESTART Mode.<br>1010 = COMPARATOR COUNTER Mode. |

### Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 52 and 53, contain the current 16-bit timeount value. When the times enabled, a read from TxH causes the value in TxL to be stored **tera**porary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from TxL read the register directly.

Writing to the Timer High and Low Byte regists while the timer is enabled is not recommended. There are no temporary holding registavailable for write perations, so simultaneous 16-bit writes are not possible. If eitthe Timer High or Low Byte registers are written during counting, the Bit written value is placed in the counter (High or Low Byte) at the next clock edge. The commontance counting from the new value.

89

107

The third scheme is enable y setting MPMD[1:0] to 1b and by writing the UART's address into the UART Address for pare Register. This mode is identical to the second scheme, except that there are no interrupted mess bytes. The first data byte of each frame remains accompanied by BWFRM assertion.

# External Driver Enable

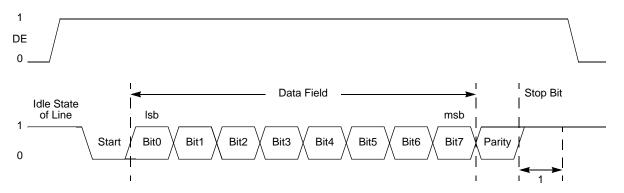

The UART provides a Driver Enable (DE)goal for off-chip bus transceivers. This feature reduces the software overhead associated using a GPIO pin to control the transceiver when communication a multi-transceiver us, such as RS-485.

Driver Enable is an active High signal theativelopes the entire transmitted data frame including parity and Stop bitas displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART TransfitData Register. The Driver Enable signal asserts at least one UART bit period and greater than two UART bit periods before the Start bit is transmitted. This allows a seturpe to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time fortadap clear the transceiver before disabling it, plus the ability to determine if anotheractacter follows the current character. In the event of back to back character(new data must be writteen the Transmit Data Register before the previous charactercompletely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UARE ontrol Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable-to-Start bit settime is calculated as follows:

$$\frac{1}{Baud Rate (Hz)^{C}} \quad DE \text{ to Start Bit Setup Time (s)} d \quad \frac{2}{Baud Rate (Hz)^{C}}$$

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register. When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

113

| 137 |  |

|-----|--|

|-----|--|

| Bit       | 7                  | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|--------------------|-------|---|---|---|---|---|---|

| Field     |                    | ADCDH |   |   |   |   |   |   |

| RESET     | Х                  | Х     | Х | Х | Х | Х | Х | Х |

| R/W       | R                  | R     | R | R | R | R | R | R |

| Address   | F72H               |       |   |   |   |   |   |   |

| X = Undef | X = Undefined.     |       |   |   |   |   |   |   |

|           |                    |       |   |   |   |   |   |   |

| Bit       | Description        |       |   |   |   |   |   |   |

| [7:0]     | ADC Data High Byte |       |   |   |   |   |   |   |

#### Table 75. ADC Data High Byte Register (ADCD\_H)

ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

## ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) Register contains the lower bits of the ADC output plus an overflow status bit. The outputaid 3-bit two's complement value. During a single-shot conversion, this values invalid. Access to the ADD ata Low Byte Register is read-only. Reading the ADC Data High Byte gister latches data in the ADC Low Bits Register.

| Bit            | 7    | 6 | 5     | 4 | 3        | 2 | 1   | 0 |

|----------------|------|---|-------|---|----------|---|-----|---|

| Field          |      |   | ADCDL |   | Reserved |   | OVF |   |

| RESET          | Х    | Х | Х     | Х | Х        | Х | Х   | Х |

| R/W            | R    | R | R     | R | R        | R | R   | R |

| Address        | F73H |   |       |   |          |   |     |   |

| X = Undefined. |      |   |       |   |          |   |     |   |

|                |      |   |       |   |          |   |     |   |

Table 76. ADC Data Low Byte Register (ADCD\_L)

| Bit            | Description                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]<br>ADCDL | ADC Data Low Bits<br>These bits are the least significant five bits of the 13-bits of the ADC output. These bits are<br>undefined after a Reset. |

| Bit    | Description (Continued)                                                                     |

|--------|---------------------------------------------------------------------------------------------|

| [5:2]  | Internal Reference Voltage Level                                                            |

| REFLVL | This reference is independent of the ADC voltage reference. Note: 8-pin devices contain two |

|        | additional LSBs for increased resolution.                                                   |

|        | For 20-/28-pin devices:                                                                     |

|        | 0000 = 0.0 V                                                                                |

|        | 0001 = 0.2 V                                                                                |

|        | 0010 = 0.4 V                                                                                |

|        | 0011 = 0.6 V                                                                                |

|        | 0100 = 0.8 V                                                                                |

|        | 0101 = 1.0 V (Default)                                                                      |

|        | 0110 = 1.2 V                                                                                |

|        | 0111 = 1.4 V                                                                                |

|        | 1000 = 1.6 V                                                                                |

|        | 1001 = 1.8 V                                                                                |

|        | 1010–1111 = Reserved                                                                        |

## Byte Read

To read a byte from the NVDS array, used conust first push the address onto the stack. User code issues CALL instruction to the address of the byte-read routine (00). At the return from the sub-routinte, read byte resides in working register R0 and the read status byte resides in working register R1. Tobuetents of the status byte are undefined for read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses by tes of stack space in addition the one byte of address pushed by the user. Sufficient memory muse available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between Advand 489 (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (the seeeding the NVDS array size) return 0xff. Illegal read operations have a secution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byteois zero, there was a corrupted value in the NVDS array at the location being read. In these, the value returned in R0 is the byte most recently written to the agrabat does not have a CRC error.

# **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. By previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byturrently being written. Abother bytes in the array are unperturbed.

# Optimizing NVDS Memory Usage for Execution Speed

NVDS read time can vary drastically. This discrepancy is a trade-off for minimizing the frequency of writes that require post-wnite ge erases, as indicated in Table 107. The NVDS read time of address N is a function the number of writes to addresses other than N since the most recent write to address N is plane number of writes since the most recent page erase. Neglecting effects used by page erases and results caused by the initial condition in which the NVDS is blank, a rule the fumb is that every write since the most recent page erase causes read times of unwritten addresses to increase play a maximum of (511-NVDS\_SIZE).

When selecting a new clock soer the system clock oscillattailure detection circuitry and the Watchdog Timer oscillator failurecciitry must be diabled. If SOFEN and WOFEN are not disabled prior to a clock swittover, it is possible to generate an interrupt for a failure of either oscillator. The ilure detection circuitry can be enabled anytime after a successful write OfSCSEL in the OSCCTL Register.

The internal precision oscillator is enabled destault. If the user code changes to a different oscillator, it may be apppriate to disable the IPOrf power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, thereanethods of recovery, as this section describes.

### System Clock Osci Ilator Failure

The Z8F04xA family devices can generate maskable interrupt-like events when the primary oscillator fails. To maintain system fution in this situation, the clock failure recovery circuitry automatidg forces the Watchdog Timersoillator to drive the system clock. The Watchdog Timer oscillator must breabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system, the CPU continues to operate, allowing execution of a kilotailure vector and software routines that either remedy the oscillator failure or issue a failure alert. This matic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (se <u>Wtatchdog Timer</u> chapter on page 93).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz ±50%. If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure detection. Under these conditions, do not enable theock failure circuitry (SOFEN must be deasserted in the OSCCTL Register).

### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar nonmaskable interrupt-like event is issued. This event does not trigggeattendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer faile, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator faile the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillatorifare detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic coss 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which

### Z8 Encore! XP <sup>®</sup> F082A Series Product Specification

202

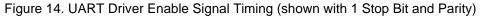

Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45k : Resistor

Caution: When using the external RC oscillator mothe oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brown-Out threshold. The oscillator resumes osticila when the supply voltage exceeds 2.7 V.

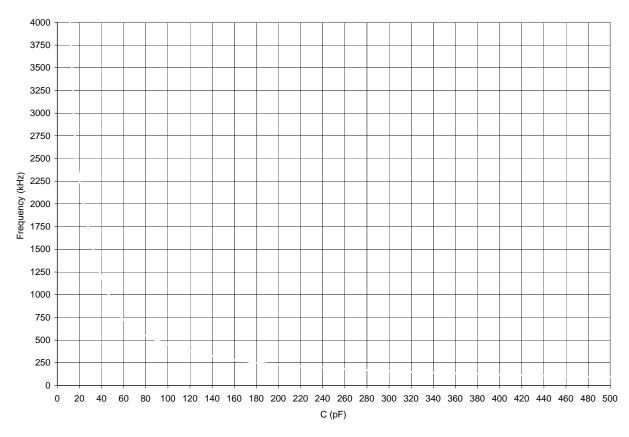

# **On-Chip Debugger Timing**

Figure 36 and Table 145 provide timing infration for the DBG pin. The DBG pin timing specifications assumed as maximum rise and fall time.

| Figure 36. | On-Chip | Debugger | Timina                                |

|------------|---------|----------|---------------------------------------|

|            | ••      |          | · · · · · · · · · · · · · · · · · · · |

|       |      | <b>A A I I</b>      | <b>.</b> | · ·    |

|-------|------|---------------------|----------|--------|

| Table | 145. | On-Chip             | Debugger | Limina |

|       |      | • · · • · · · · · · |          |        |

|                |                                              | Delay (ns) |         |  |

|----------------|----------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |  |

| DBG            |                                              |            |         |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | -          | 15      |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time             | 5          | -       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time              | 5          | -       |  |