Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082asb020sg    |

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                               | Description                                                                                                                                                                      | Page<br>No.                    |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Dec<br>2012 | 27                | Port Alternate Function Mapping (Non 8-Pin Parts), Port Alternate Function Mapping (8-Pin Parts)                              | Added missing Port D data to Table 15; corrected active Low status (set overlines) for PAO (TOOUT), PA2 (RESET) and PA5 (T1OUT) in Table 16.                                     | <u>40, 43</u>                  |

| Sep<br>2011 | 26                | LED Drive Enable Register                                                                                                     | Clarified statement surrounding the Alternate Function Register as it relates to the LED function; revised Flash Sector Protect Register description; revised Packaging chapter. | 53,<br>157,<br>245             |

| Sep<br>2008 | 25                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Added references to F042A Series back in Table 1, Table 5, Table 7 and Table 14.                                                                                                 | 2, 8,<br>16, 18,<br>36,<br>246 |

| May<br>2008 | 24                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Changed title to Z8 Encore! XP F082A Series and removed references to F042A Series in Table 1, Table 5, Table 7 and Table 14.                                                    | 2, 8,<br>16, 18,<br>36,<br>246 |

| Dec<br>2007 | 23                | Pin Description, General-Purpose Input/Output, Watchdog Timer                                                                 | Updated Figure 3, Table 15, Tables 60 through 62.                                                                                                                                | 9, <u>40,</u><br><u>97</u>     |

| Jul<br>2007 | 22                | Electrical Characteristics                                                                                                    | Updated Tables 16 and 132; power consumption data.                                                                                                                               | <u>43,</u><br><u>229</u>       |

| Jun<br>2007 | 21                | n/a                                                                                                                           | Revision number update.                                                                                                                                                          | All                            |

| LED Drive Level Low Register                             | . 54 |

|----------------------------------------------------------|------|

| GPIO Mode Interrupt Controller                           | . 55 |

| Interrupt Vector Listing                                 | . 55 |

| Architecture                                             | . 57 |

| Operation                                                | . 57 |

| Master Interrupt Enable                                  | . 57 |

| Interrupt Vectors and Priority                           | . 58 |

| Interrupt Assertion                                      | . 58 |

| Software Interrupt Assertion                             | . 59 |

| Watchdog Timer Interrupt Assertion                       | . 59 |

| Interrupt Control Register Definitions                   |      |

| Interrupt Request 0 Register                             | 60   |

| Interrupt Request 1 Register                             | 61   |

| Interrupt Request 2 Register                             |      |

| IRQ0 Enable High and Low Bit Registers                   | . 62 |

| IRQ1 Enable High and Low Bit Registers                   |      |

| IRQ2 Enable High and Low Bit Registers                   |      |

| Interrupt Edge Select Register                           |      |

| Shared Interrupt Select Register                         |      |

| Interrupt Control Register                               | 69   |

| Timers                                                   | . 70 |

| Architecture                                             | . 70 |

| Operation                                                | . 71 |

| Timer Operating Modes                                    | . 71 |

| Reading the Timer Count Values                           | . 84 |

| Timer Pin Signal Operation                               | . 84 |

| Timer Control Register Definitions                       | 85   |

| Timer 0–1 Control Registers                              | 85   |

| Timer 0–1 High and Low Byte Registers                    | . 89 |

| Timer Reload High and Low Byte Registers                 |      |

| Timer 0–1 PWM High and Low Byte Registers                | . 92 |

| Watchdog Timer                                           | 93   |

| Operation                                                |      |

| Watchdog Timer Refresh                                   |      |

| Watchdog Timer Time-Out Response                         |      |

| Watchdog Timer Reload Unlock Sequence                    |      |

| Watchdog Timer Calibration                               |      |

| Watchdog Timer Control Register Definitions              |      |

| Watchdog Timer Control Register                          |      |

| Watchdog Timer Reload Upper, High and Low Byte Registers |      |

|                                                          |      |

| Table 59. | Watchdog Timer Control Register (WDTCTL)               |

|-----------|--------------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU) 9     |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH) 9      |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL) 9       |

| Table 63. | UART Control 0 Register (U0CTL0)                       |

| Table 64. | UART Control 1 Register (U0CTL1)                       |

| Table 65. | UART Status 0 Register (U0STAT0)                       |

| Table 66. | UART Status 1 Register (U0STAT1)                       |

| Table 67. | UART Transmit Data Register (U0TXD)                    |

| Table 68. | UART Receive Data Register (U0RXD)                     |

| Table 69. | UART Address Compare Register (U0ADDR)                 |

| Table 70. | UART Baud Rate High Byte Register (U0BRH)11            |

| Table 71. | UART Baud Rate Low Byte Register (U0BRL)               |

| Table 72. | UART Baud Rates                                        |

| Table 73. | ADC Control Register 0 (ADCCTL0)                       |

| Table 74. | ADC Control/Status Register 1 (ADCCTL1)                |

| Table 75. | ADC Data High Byte Register (ADCD_H)                   |

| Table 76. | ADC Data Low Byte Register (ADCD_L)                    |

| Table 77. | Comparator Control Register (CMP0)                     |

| Table 78. | Z8 Encore! XP F082A Series Flash Memory Configurations |

| Table 79. | Flash Code Protection Using the Flash Option Bits      |

| Table 80. | Flash Status Register (FSTAT)                          |

| Table 81. | Flash Control Register (FCTL)                          |

| Table 82. | Flash Page Select Register (FPS)                       |

| Table 83. | Flash Sector Protect Register (FPROT)                  |

| Table 84. | Flash Frequency High Byte Register (FFREQH)            |

| Table 85. | Flash Frequency Low Byte Register (FFREQL)             |

| Table 86. | Trim Bit Address Register (TRMADR)                     |

| Table 87. | Trim Bit Data Register (TRMDR)                         |

| Table 88. | Flash Option Bits at Program Memory Address 0000H 16   |

**Table 2. Signal Descriptions (Continued)**

| Signal Mnemonic  | I/O | Description                                                                                                                                                                                                           |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset            |     |                                                                                                                                                                                                                       |

| RESET            | I/O | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply     |     |                                                                                                                                                                                                                       |

| $V_{DD}$         | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> | I   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>  | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub> | I   | Analog Ground.                                                                                                                                                                                                        |

#### Notes:

- PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by AV<sub>DD</sub> and AV<sub>SS</sub>.

- 2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

## **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

<u>Table 4</u> on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note:

All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

Table 7. Register File Address Map (Continued)

| Address (Hex)   | Register Description                  | Mnemonic | Reset (Hex) | Page        |

|-----------------|---------------------------------------|----------|-------------|-------------|

| FD9             | Port C Control                        | PCCTL    | 00          | <u>46</u>   |

| FDA             | Port C Input Data                     | PCIN     | XX          | <u>46</u>   |

| FDB             | Port C Output Data                    | PCOUT    | 00          | <u>46</u>   |

| GPIO Port D     |                                       |          |             |             |

| FDC             | Port D Address                        | PDADDR   | 00          | <u>44</u>   |

| FDD             | Port D Control                        | PDCTL    | 00          | <u>46</u>   |

| FDE             | Reserved                              | _        | XX          |             |

| FDF             | Port D Output Data                    | PDOUT    | 00          | <u>46</u>   |

| FE0-FEF         | Reserved                              | _        | XX          |             |

| Watchdog Time   | r (WDT)                               |          |             |             |

| FF0             | Reset Status (Read-only)              | RSTSTAT  | X0          | <u>29</u>   |

|                 | Watchdog Timer Control (Write-only)   | WDTCTL   | N/A         | <u>96</u>   |

| FF1             | Watchdog Timer Reload Upper Byte      | WDTU     | 00          | <u>97</u>   |

| FF2             | Watchdog Timer Reload High Byte       | WDTH     | 04          | <u>97</u>   |

| FF3             | Watchdog Timer Reload Low Byte        | WDTL     | 00          | <u>98</u>   |

| FF4-FF5         | Reserved                              | _        | XX          |             |

| Trim Bit Contro | I                                     |          |             |             |

| FF6             | Trim Bit Address                      | TRMADR   | 00          | <u>161</u>  |

| FF7             | Trim Bit Data                         | TRMDR    | 00          | <u>162</u>  |

| Flash Memory C  | Controller                            |          |             |             |

| FF8             | Flash Control                         | FCTL     | 00          | <u>155</u>  |

| FF8             | Flash Status                          | FSTAT    | 00          | <u>155</u>  |

| FF9             | Flash Page Select                     | FPS      | 00          | <u>156</u>  |

|                 | Flash Sector Protect                  | FPROT    | 00          | <u>157</u>  |

| FFA             | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>158</u>  |

| FFB             | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>158</u>  |

| eZ8 CPU         |                                       |          |             |             |

| FFC             | Flags                                 | _        | XX          | See         |

| FFD             | Register Pointer                      | RP       | XX          | foot-       |

| FFE             | Stack Pointer High Byte               | SPH      | XX          | -note 2     |

| FFF             | Stack Pointer Low Byte                | SPL      | XX          | <del></del> |

#### Notes:

- 1. XX = Undefined.

- 2. Refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>.

# **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see the On-Chip Debugger chapter on page 180.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the Oscillator Control Register Definitions section on page 196 for details.

## **5V Tolerance**

All six I/O pins on the 8-pin devices are 5V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

Note:

In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) Register such that the external oscillator is selected as the system clock. See the Oscillator Control Register Definitions section on page 196 for details. For 8-pin devices, use PA1 instead of PB3.

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See the GPIO Mode Interrupt Controller chapter on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data. Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

**Table 17. GPIO Port Registers and Subregisters**

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register; selects subregisters.            |

| PxCTL                     | Port A–D Control Register; provides access to subregisters. |

| PxIN                      | Port A–D Input Data Register.                               |

| P <i>x</i> OUT            | Port A–D Output Data Register.                              |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction.                                             |

| PxAF                      | Alternate Function.                                         |

| PxOC                      | Output Control (Open-Drain).                                |

| PxHDE                     | High Drive Enable.                                          |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable.                           |

| P <i>x</i> PUE            | Pull-up Enable.                                             |

| PxAFS1                    | Alternate Function Set 1.                                   |

| PxAFS2                    | Alternate Function Set 2.                                   |

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

## Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART Control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> section on page 99.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered down state, the ADC uses 40 additional clock cycles to power up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 13-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- CEN resets to 0 to indicate the conversion is complete

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered down.

#### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value overwrites the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not immediately detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following steps for setting up the ADC and initiating continuous conversion:

- 1. Enable the appropriate analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

#### Note:

The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the multiplication must be performed before the division by  $2^{16}$ . Otherwise, the second term incorrectly evaluates to zero.

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit nonunity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

## **ADC Compensation Details**

High-efficiency assembly code that performs ADC compensation is available for download on <a href="www.zilog.com">www.zilog.com</a>. This section offers a bit-specific description of the ADC compensation process used by this code.

The following data bit definitions are used:

0-9, a-f = bit indices in hexadecimal

s = sign bit

v = overflow bit

- = unused

### **Input Data**

| MSB             | LSB                      |                                                |

|-----------------|--------------------------|------------------------------------------------|

| s b a 9 8 7 6 5 | 4 3 2 1 0 v (ADC)        | ADC Output Word; if v = 1, the data is invalid |

|                 | s 6 5 4 3 2 1 0          | Offset Correction Byte                         |

| sssss 7 6 5     | 4 3 2 1 0 0 0 0 (Offset) | Offset Byte shifted to align with ADC data     |

| ~ ~ d ~ b ~ 0 0 | 7.6.5.4.2.2.1.0. (Gain)  | Gain Correction Word                           |

| sedcba98        | 7 6 5 4 3 2 1 0 (Gain)   | Gain Correction word                           |

## Flash Program Memory Address 0001H

Table 89. Flash Options Bits at Program Memory Address 0001H

| Bit                                             | 7                    | 6   | 5   | 4      | 3            | 2   | 1   | 0   |

|-------------------------------------------------|----------------------|-----|-----|--------|--------------|-----|-----|-----|

| Field                                           | Reserved             |     |     | XTLDIS | DIS Reserved |     |     |     |

| RESET                                           | U                    | U   | U   | U      | U            | U   | U   | U   |

| R/W                                             | R/W                  | R/W | R/W | R/W    | R/W          | R/W | R/W | R/W |

| Address                                         | Program Memory 0001H |     |     |        |              |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |     |     |        |              |     |     |     |

| Bit    | Description                                                                                               |

|--------|-----------------------------------------------------------------------------------------------------------|

| [7:5]  | Reserved                                                                                                  |

|        | These bits are reserved and must be programmed to 111.                                                    |

| [4]    | State of the Crystal Oscillator at Reset                                                                  |

| XTLDIS | This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually. |

|        | 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing.                         |

1 = Crystal oscillator is disabled during reset, resulting in shorter reset timing.

**Caution:** Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless further debugging or Flash programming is not required.

### [3:0] Reserved

These bits are reserved and must be programmed to 1111.

# Crystal Oscillator

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{\rm IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{\rm OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{\rm IN}$  input pin determines the frequency of the system clock.

Note:

Although the  $X_{IN}$  pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

## **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)</li>

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

# Internal Precision Oscillator

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

# **Operation**

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30°C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control Register (see the <u>Oscillator Control Register Definitions section on page 196</u>).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in the <u>Trim Bit Address Space</u> section on page 165.

Select one of two frequencies for the oscillator (5.53 MHz and 32.8 kHz) using the OSC-SEL bits in the the Oscillator Control chapter on page 193.

### **Assembly Language Source Program Example**

JP START ; Everything after the semicolon is a comment.

START: ; A label called 'START'. The first instruction (JP START) in this

; example causes program execution to jump to the point within the

; program where the START label occurs.

LD R4, R7; A Load (LD) instruction with two operands. The first operand,

; Working Register R4, is the destination. The second operand, ; Working Register R7, is the source. The contents of R7 is

; written into R4.

LD 234H, #%01; Another Load (LD) instruction with two operands.

; The first operand, Extended Mode Register Address  $234 \mathrm{H}$ , ; identifies the destination. The second operand, Immediate Data ; value  $01 \mathrm{H}$ , is the source. The value  $01 \mathrm{H}$  is written into the

; Register at address 234H.

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1.** If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 116. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | H80 | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2.** In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 117. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing

$V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$   $T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ (unless otherwise stated)

| Symbol                   | Parameter                                                 | Minimum    | Typical      | Maximum    | Units                          | Conditions                                                                          |

|--------------------------|-----------------------------------------------------------|------------|--------------|------------|--------------------------------|-------------------------------------------------------------------------------------|

|                          | Resolution                                                | 10         |              | _          | bits                           |                                                                                     |

|                          | Differential Nonlinearity (DNL)                           | -1.0       | -            | 1.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |

|                          | Integral Nonlinearity (INL)                               | -3.0       | -            | 3.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |

|                          | Offset Error with Calibration                             |            | <u>+</u> 1   |            | LSB <sup>3</sup>               |                                                                                     |

|                          | Absolute Accuracy with Calibration                        |            | <u>+</u> 3   |            | LSB <sup>3</sup>               |                                                                                     |

| V <sub>REF</sub>         | Internal Reference Voltage                                | 1.0<br>2.0 | 1.1<br>2.2   | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                              |

| V <sub>REF</sub>         | Internal Reference Variation with Temperature             |            | <u>+</u> 1.0 |            | %                              | Temperature variation with V <sub>DD</sub> = 3.0                                    |

| V <sub>REF</sub>         | Internal Reference Voltage Variation with V <sub>DD</sub> |            | <u>+</u> 0.5 |            | %                              | Supply voltage variation with T <sub>A</sub> = 30°C                                 |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output Impedance                         |            | 850          |            | W                              | When the internal reference is buffered and driven out to the VREF pin (REFOUT = 1) |

|                          | Single-Shot Conversion<br>Time                            | -          | 5129         | -          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                             |

|                          |                                                           |            | 10258        |            |                                | Temperature sensor measurement                                                      |

#### Notes:

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD} = 3.3 \,\text{V}$  and  $T_A = +30 \,^{\circ}\text{C}$ , so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

**Table 142. Temperature Sensor Electrical Characteristics**

|                   | Parameter         | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$ |              |            |       |                                                                   |

|-------------------|-------------------|--------------------------------------------|--------------|------------|-------|-------------------------------------------------------------------|

| Symbol            |                   | Minimum                                    | Typical      | Maximum    | Units | Conditions                                                        |

| T <sub>AERR</sub> | Temperature Error |                                            | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20°C to +30°C (as measured by ADC).1              |

|                   |                   |                                            | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0°C to +70°C (as measured by ADC).                |

|                   |                   |                                            | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0°C to +105°C (as measured by ADC).               |

|                   |                   |                                            | <u>+</u> 7   |            | °C    | Over the range -40°C to +105°C (as measured by ADC).              |

| t <sub>WAKE</sub> | Wakeup Time       |                                            | 80           | 100        | μS    | Time required for Temperature Sensor to stabilize after enabling. |

Note: Devices are factory calibrated at for maximal accuracy between +20°C and +30°C, so the sensor is maximally accurate in that range. User recalibration for a different temperature range is possible and increases accuracy near the new calibration point.

# **General Purpose I/O Port Output Timing**

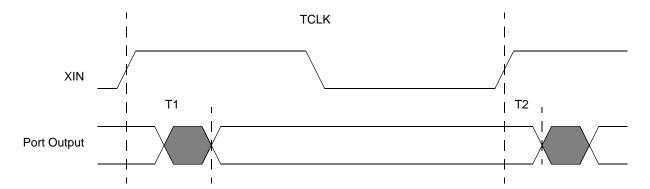

Figure 35 and Table 144 provide timing information for GPIO port pins.

Figure 35. GPIO Port Output Timing

**Table 144. GPIO Port Output Timing**

|                |                                                 | Delay (ns) |         |  |

|----------------|-------------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |

| GPIO port pi   | ns                                              |            |         |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |

| read program memory (0BH) 189                       | power supply signals 12                          |

|-----------------------------------------------------|--------------------------------------------------|

| read program memory CRC (0EH) 190                   | Power-on and Voltage Brownout electrical charac- |

| read register (09H) 189                             | teristics and timing 233                         |

| read runtime counter (03H) 187                      | Power-On Reset (POR) 24                          |

| step instruction (10H) 190                          | program control instructions 211                 |

| stuff instruction (11H) 190                         | program counter 207                              |

| write data memory (0CH) 189                         | program memory 15                                |

| write OCD control register (04H) 188                | PUSH 210                                         |

| write program counter (06H) 188                     | push using extended addressing 210               |

| write program memory (0AH) 189                      | PUSHX 210                                        |

| write register (08H) 188                            | PWM mode 87, 88                                  |

| on-chip debugger (OCD) 180                          | PxADDR register 45                               |

| on-chip debugger signals 11                         | PxCTL register 46                                |

| on-chip oscillator 198                              |                                                  |

| ONE-SHOT mode 87                                    | _                                                |

| opcode map                                          | R                                                |

| abbreviations 223                                   | R 206                                            |

| cell description 222                                | r 206                                            |

| first 224                                           | RA                                               |

| second after 1FH 225                                | register address 206                             |

| Operational Description 22, 32, 36, 55, 70, 93, 99, | RCF 209, 210                                     |

| 120, 124, 139, 140, 144, 146, 159, 176, 180, 193,   | receive                                          |

| 198, 203                                            | IrDA data 122                                    |

| OR 210                                              | receiving UART data-interrupt-driven method 104  |

| ordering information 246                            | receiving UART data-polled method 103            |

| ORX 210                                             | register 206                                     |

| oscillator signals 11                               | ADC control (ADCCTL) 134, 135                    |

|                                                     | ADC data high byte (ADCDH) 136                   |

| _                                                   | ADC data low bits (ADCDL) 137                    |

| P                                                   | flash control (FCTL) 155, 161, 162               |

| p 206                                               | flash high and low byte (FFREQH and FRE-         |

| Packaging 245                                       | EQL) 157                                         |

| part selection guide 2                              | flash page select (FPS) 156, 157                 |

| PC 207                                              | flash status (FSTAT) 155                         |

| peripheral AC and DC electrical characteristics 233 | GPIO port A-H address (PxADDR) 45                |

| pin characteristics 12                              | GPIO port A-H alternate function sub-registers   |

| Pin Descriptions 8                                  | 47                                               |

| polarity 206                                        | GPIO port A-H control address (PxCTL) 46         |

| POP 210                                             | GPIO port A-H data direction sub-registers 46    |

| pop using extended addressing 210                   | OCD control 191                                  |

| POPX 210                                            | OCD status 192                                   |

| port availability, device 36                        | UARTx baud rate high byte (UxBRH) 117            |

| port input timing (GPIO) 240                        | UARTx baud rate low byte (UxBRL) 117             |

| port output timing, GPIO 241                        | UARTx Control 0 (UxCTL0) 111, 117                |

## Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2