# E·XFL

### Zilog - Z8F082ASH020EG2156 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 17                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | ·                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 7x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | 20-SOIC                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082ash020eg2156 |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1.  | Z8 Encore! XP F082A Series Family Part Selection Guide 2           |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Signal Descriptions                                                |

| Table 3.  | Pin Characteristics (20- and 28-pin Devices) 13                    |

| Table 4.  | Pin Characteristics (8-Pin Devices) 14                             |

| Table 5.  | Z8 Encore! XP F082A Series Program Memory Maps 16                  |

| Table 6.  | Z8 Encore! XP F082A Series Flash Memory Information Area Map 17    |

| Table 7.  | Register File Address Map 18                                       |

| Table 8.  | Reset and Stop Mode Recovery Characteristics and Latency 23        |

| Table 9.  | Reset Sources and Resulting Reset Type 24                          |

| Table 10. | Stop Mode Recovery Sources and Resulting Action                    |

| Table 11. | Reset Status Register (RSTSTAT)                                    |

| Table 12. | Reset and Stop Mode Recovery Bit Descriptions                      |

| Table 13. | Power Control Register 0 (PWRCTL0)                                 |

| Table 14. | Port Availability by Device and Package Type                       |

| Table 15. | Port Alternate Function Mapping (Non 8-Pin Parts) 40               |

| Table 16. | Port Alternate Function Mapping (8-Pin Parts)                      |

| Table 17. | GPIO Port Registers and Subregisters                               |

| Table 18. | Port A–D GPIO Address Registers (PxADDR)                           |

| Table 19. | Port A–D GPIO Address Registers by Bit Description                 |

| Table 20. | Port A–D Control Registers (PxCTL)                                 |

| Table 21. | Port A–D Data Direction Subregisters (PxDD) 46                     |

| Table 22. | Port A–D Alternate Function Subregisters (PxAF)                    |

| Table 23. | Port A–D Output Control Subregisters (PxOC)                        |

| Table 24. | Port A–D High Drive Enable Subregisters (PxHDE)                    |

| Table 25. | Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE) 49 |

| Table 26. | Port A–D Pull-Up Enable Subregisters (PxPUE)                       |

| Table 27. | Port A–D Alternate Function Set 2 Subregisters (PxAFS2) 51         |

| Table 28. | Port A–D Alternate Function Set 1 Subregisters (PxAFS1) 51         |

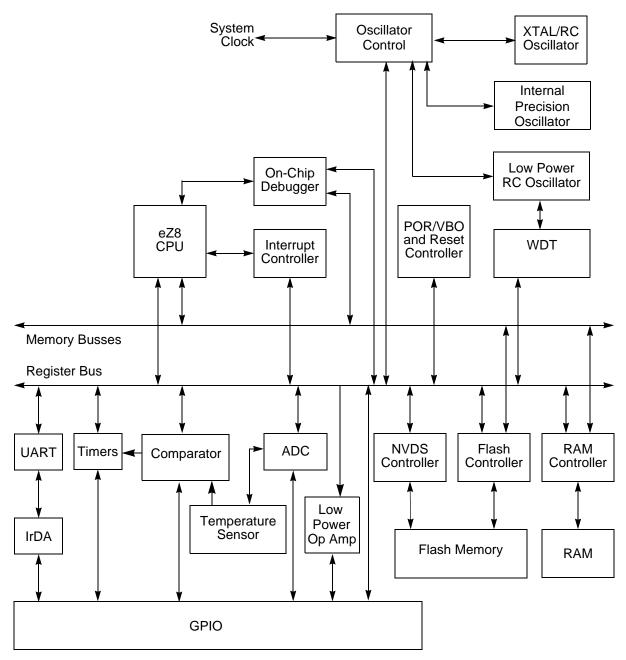

# **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP F082A Series devices.

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See the <u>Pin Configurations</u> section on page 8 to determine the signals available for the specific package styles.

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                                             |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/0 | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PD[0]               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |

| UART Controllers    |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                | Ι       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 Register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers              |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |

| T0OUT/T1OUT         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and coun-<br>ter inputs.                                                                                                                                                                                                                 |

| Comparator          |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |

#### **Table 2. Signal Descriptions**

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |  |  |  |  |

|------------------------------|------------------------------|--|--|--|--|

| Z8F082A and Z8F081A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-1FFF                    | Program Memory               |  |  |  |  |

| Z8F042A and Z8F041A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-0FFF                    | Program Memory               |  |  |  |  |

| Z8F022A and Z8F021A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-07FF                    | Program Memory               |  |  |  |  |

| Z8F012A and Z8F011A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

|                              |                              |  |  |  |  |

### Table 5. Z8 Encore! XP F082A Series Program Memory Maps

Note: \*See Table 32 on page 56 for a list of the interrupt vectors.

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

### Table 12. Reset and Stop Mode Recovery Bit Descriptions

| Port                  | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|-----------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1,2</sup> | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA1 | TOOUT      | Timer 0 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA2 | DE0        | UART 0 Driver Enable                    | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA3 | CTS0       | UART 0 Clear to Send                    | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA7 | T1OUT      | Timer 1 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the Port <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

# **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7                      | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------------------|-------------------------|---|---|---|---|---|---|--|

| Field   | PCTL                   |                         |   |   |   |   |   |   |  |

| RESET   | 00H                    |                         |   |   |   |   |   |   |  |

| R/W     | R/W                    | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD1H, FD5H, FD9H, FDDH |                         |   |   |   |   |   |   |  |

### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7                                                                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | DD7                                                                                   | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

# **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit          | 7                                                                                                                                                                                                       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field        | PA7VS PA6CS Reserved                                                                                                                                                                                    |     |     |     |     |     |     |     |

| RESET        | 0                                                                                                                                                                                                       | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W          | R/W                                                                                                                                                                                                     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address      |                                                                                                                                                                                                         |     |     | FC  | EH  |     |     |     |

| Bit          | Description                                                                                                                                                                                             |     |     |     |     |     |     |     |

| [7]<br>PA7VS | <ul> <li><b>PA7/LVD Selection</b></li> <li>0 = PA7 is used for the interrupt for PA7VS interrupt request.</li> <li>1 = The LVD is used for the interrupt for PA7VS interrupt request.</li> </ul>        |     |     |     |     |     |     |     |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator is used for the interrupt for PA6CS interrupt request.</li> </ul> |     |     |     |     |     |     |     |

| [5:0]        | Reserved                                                                                                                                                                                                |     |     |     |     |     |     |     |

#### Table 48. Shared Interrupt Select Register (IRQSS)

These bits are reserved and must be programmed to 000000.

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

# **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit                  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|------|---|---|---|---|---|---|---|

| Field                | TXD  |   |   |   |   |   |   |   |

| RESET                | Х    | Х | Х | Х | Х | Х | Х | Х |

| R/W                  | W    | W | W | W | W | W | W | W |

| Address              | F40H |   |   |   |   |   |   |   |

| Note: X = Undefined. |      |   |   |   |   |   |   |   |

#### Table 67. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68 | . UART | Receive | Data | Register | (U0RXD) |

|----------|--------|---------|------|----------|---------|

|----------|--------|---------|------|----------|---------|

| Bit                  | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|------------|-----|---|---|---|---|---|---|

| Field                |            | RXD |   |   |   |   |   |   |

| RESET                | Х          | Х   | Х | Х | Х | Х | Х | Х |

| R/W                  | R          | R   | R | R | R | R | R | R |

| Address              | F40H       |     |   |   |   |   |   |   |

| Note: X = Undefined. |            |     |   |   |   |   |   |   |

| Bit                  | Descriptio | n   |   |   |   |   |   |   |

| Dit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

## **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

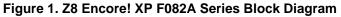

# Infrared Encoder/Decoder

Z8 Encore! XP F082A Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (endec). The infrared endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! XP MCU and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

### 150

#### Table 79. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Mem-<br>ory. In user code programming, Page Erase and Mass Erase are all<br>disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                   |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the target page. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. See Figure 22 on page 148 for details.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F082A Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 78</u> on page 146.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Regis-

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

### **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the <u>Third-Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download on <u>www.zilog.com</u>.

| LVD_TRIM | LVD Threshold (V)<br>Typical | Description             |

|----------|------------------------------|-------------------------|

| 00000    | 3.60                         | Maximum LVD threshold   |

| 00001    | 3.55                         |                         |

| 00010    | 3.50                         |                         |

| 00010    | 3.45                         |                         |

| 00100    | 3.40                         |                         |

| 00100    | 3.35                         |                         |

| 00101    | 3.30                         |                         |

| 00110    | 3.25                         |                         |

| 01000    | 3.20                         |                         |

|          |                              |                         |

| 01001    | 3.15                         |                         |

| 01010    | 3.10                         | Default on Reset        |

| 01011    | 3.05                         |                         |

| 01100    | 3.00                         |                         |

| 01101    | 2.95                         |                         |

| 01110    | 2.90                         |                         |

| 01111    | 2.85                         |                         |

| 10000    | 2.80                         |                         |

| 10001    | 2.75                         |                         |

| 10010    | 2.70                         |                         |

| 10011    | 2.70                         |                         |

| to       | to                           | Minimum LVD there shall |

| 11111    | 1.65                         | Minimum LVD threshold   |

### Table 94. LVD Trim Values

| Debug Command           | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter   | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter    | 07H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control Register. |

| Read Register           | 09H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory    | 0AH             | -                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory     | 0BH             | -                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory       | 0CH             | -                                     | Yes.                                                                                                                                                                      |

| Read Data Memory        | 0DH             | _                                     | -                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | -                                     | _                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled.                                                                                                                                                                 |

| Stuff Instruction       | 11H             | _                                     | Disabled.                                                                                                                                                                 |

| Execute Instruction     | 12H             | _                                     | Disabled.                                                                                                                                                                 |

| Reserved                | 13H–FFH         | _                                     | -                                                                                                                                                                         |

### Table 109. Debug Command Enable/Disable (Continued)

In the list of OCD commands that follows, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

DBG  $\leftarrow$  02H DBG  $\rightarrow$  OCDSTAT[7:0]

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory,

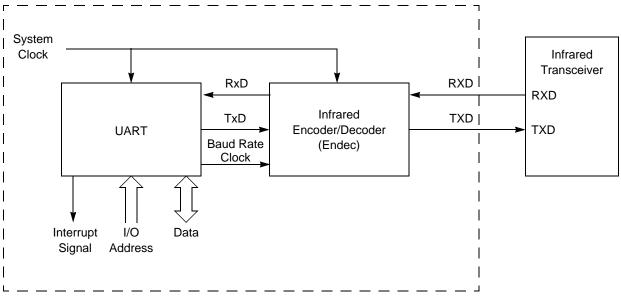

# **Oscillator Operation with an External RC Network**

Figure 28 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

#### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45 \text{ k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$

Figure 29 displays the typical  $(3.3 \text{ V} \text{ and } 25^{\circ}\text{C})$  oscillator frequency as a function of the capacitor (C, in pF) employed in the RC network assuming a  $45 \text{ K}\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended.

### Table 123. CPU Control Instructions (Continued)

| Mnemonic Operands |     | Instruction            |

|-------------------|-----|------------------------|

| RCF               | —   | Reset Carry Flag       |

| SCF               | —   | Set Carry Flag         |

| SRP               | SIC | Set Register Pointer   |

| STOP              | —   | STOP Mode              |

| WDT               | —   | Watchdog Timer Refresh |

### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | SIC         | Push using Extended Addressing                                          |

### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

### 242

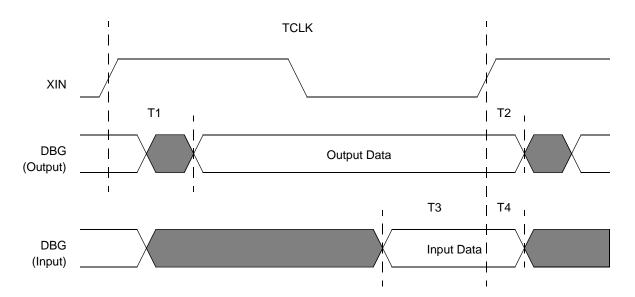

# **On-Chip Debugger Timing**

Figure 36 and Table 145 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                              | Delay (ns) |         |

|----------------|----------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |

| DBG            |                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time             | 5          | -       |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time              | 5          | _       |

### Table 145. On-Chip Debugger Timing

| Part Number                                | Flash | RAM | SDVN  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|--------------------------------------------|-------|-----|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A Series with 4 KB Flash |       |     |       |           |            |                     |                     |                |            |                    |                     |

| Standard Temperatu                         |       |     |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020SG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020SG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020SG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020SG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020SG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020SG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020SG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020SG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020SG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C       |       |     |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020EG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020EG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020EG                             | 4 KB  | 1KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020EG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020EG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020EG                             | 4 KB  | 1KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020EG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020EG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020EG                             | 4 KB  | 1KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix