## E·XFL

#### Zilog - Z8F082ASJ020EG2156 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ8                                                           |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 20MHz                                                         |

| Connectivity               | IrDA, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT  |

| Number of I/O              | 23                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | ·                                                             |

| RAM Size                   | 1K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                   |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | 28-SOIC                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082asj020eg2156 |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brown-Out (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO and LVD

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- 8-, 20- and 28-pin packages

- $0^{\circ}$ C to  $+70^{\circ}$ C and  $-40^{\circ}$ C to  $+105^{\circ}$ C for operating temperature ranges

## **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP F082A Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Mateau         |               |            |                          |      |            |                                 |               |                    |

#### Table 1. Z8 Encore! XP F082A Series Family Part Selection Guide

Notes:

1. Non-volatile data storage.

2. Advanced Analog includes ADC, temperature sensor and low-power operational amplifier.

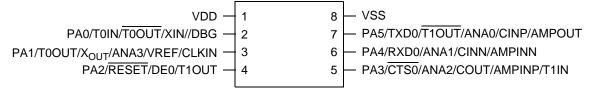

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

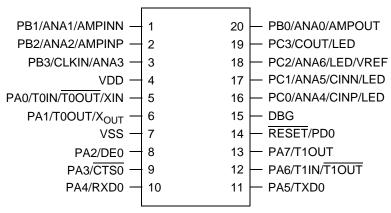

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

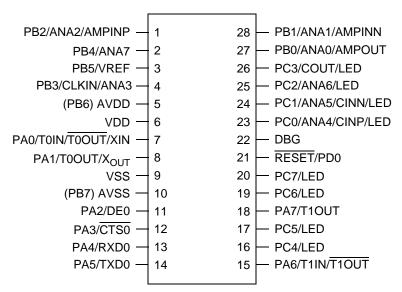

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

| Signal Mnemonic  | I/O | Description                                                                                                                                                                                                           |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset            |     |                                                                                                                                                                                                                       |

| RESET            | I/O | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply     |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>  | Ι   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub> | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>  | Ι   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub> | Ι   | Analog Ground.                                                                                                                                                                                                        |

| Notes:           |     |                                                                                                                                                                                                                       |

#### Table 2. Signal Descriptions (Continued)

inotes

1. PB6 and PB7 are only available in 28-pin packages without ADC. In 28-pin packages with ADC, they are replaced by  $AV_{DD}$  and  $AV_{SS}$ .

2. The AV<sub>DD</sub> and AV<sub>SS</sub> signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

## **Pin Characteristics**

Table 3 describes the characteristics for each pin available on the Z8 Encore! XP F082A Series 20- and 28-pin devices. Data in Table 3 is sorted alphabetically by the pin symbol mnemonic.

Table 4 on page 14 provides detailed information about the characteristics for each pin available on the Z8 Encore! XP F082A Series 8-pin devices.

Note: All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 3 below describes 5 V-tolerance for the 20- and 28-pin packages only.

## **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See the <u>GPIO Mode Interrupt Controller</u> chapter on page 55 for more information about interrupts using the GPIO pins.

## **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data. Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register; selects subregisters.            |

| P <i>x</i> CTL            | Port A–D Control Register; provides access to subregisters. |

| PxIN                      | Port A–D Input Data Register.                               |

| P <i>x</i> OUT            | Port A–D Output Data Register.                              |

| Port Subregister Mnemonic | Port Register Name                                          |

| P <i>x</i> DD             | Data Direction.                                             |

| P <i>x</i> AF             | Alternate Function.                                         |

| P <i>x</i> OC             | Output Control (Open-Drain).                                |

| P <i>x</i> HDE            | High Drive Enable.                                          |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable.                           |

| P <i>x</i> PUE            | Pull-up Enable.                                             |

| PxAFS1                    | Alternate Function Set 1.                                   |

| PxAFS2                    | Alternate Function Set 2.                                   |

Table 17. GPIO Port Registers and Subregisters

• Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap and Illegal Instruction Trap always have highest (level 3) priority.

#### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

#### Table 62. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit        | 7                                                                                            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|----------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|--|

| Field      | WDTL                                                                                         |   |   |   |   |   |   |   |  |

| RESET      | 00H                                                                                          |   |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                         |   |   |   |   |   |   |   |  |

| Address    | FF3H                                                                                         |   |   |   |   |   |   |   |  |

| Note: A re | Note: A read returns the current WDT count value; a write sets the appropriate reload value. |   |   |   |   |   |   |   |  |

| Bit        | Descriptio                                                                                   | n |   |   |   |   |   |   |  |

| Dit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                           |

| WDTL  | Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

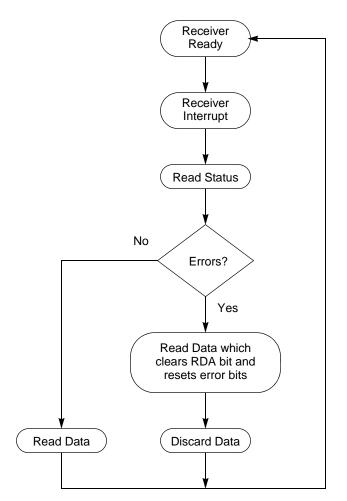

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

Figure 15. UART Receiver Interrupt Service Routine Flow

#### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud

Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

## **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

## **Transmitting IrDA Data**

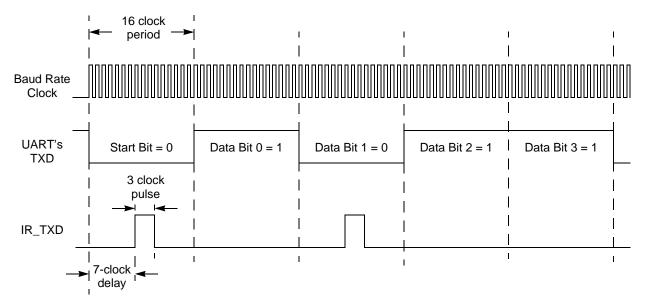

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

## **ADC Control Register 0**

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |                                                              |                           | •                                    | -                            |                             |                              |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|--------------------------------------|------------------------------|-----------------------------|------------------------------|

| Bit                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                 | 5                                                            | 4                         | 3                                    | 2                            | 1                           | 0                            |

| Field               | CEN REFSELL REFOUT CONT ANAIN[3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                   |                                                              |                           |                                      |                              |                             |                              |

| RESET               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                 | 0                                                            | 0                         | 0                                    | 0                            | 0                           | 0                            |

| R/W                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                               | R/W                                                          | R/W                       | R/W                                  | R/W                          | R/W                         | R/W                          |

| Address             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |                                                              | F7                        | 0H                                   |                              |                             |                              |

| Bit                 | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tion                                                                                              |                                                              |                           |                                      |                              |                             |                              |

| [7]<br>CEN          | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                                                                                                                                                                     |                                                                                                   |                                                              |                           |                                      |                              |                             |                              |

| [6]<br>REFSELL      | <ul> <li>Voltage Reference Level Select Low Bit</li> <li>In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REF-SELH, REFSELL}; note that this reference is independent of the Comparator reference.</li> <li>00 = Internal Reference Disabled, reference comes from external pin.</li> <li>01 = Internal Reference set to 1.0 V.</li> <li>10 = Internal Reference set to 2.0 V (default).</li> <li>11 = Reserved.</li> </ul> |                                                                                                   |                                                              |                           |                                      |                              |                             |                              |

| [5]<br>REFOUT       | Internal Reference Output Enable<br>0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions.<br>1 = The internal ADC reference is buffered and driven out to the $V_{REF}$ pin.<br>Caution: When the ADC is used with an external reference ({REFSELH,REFSELL}=00),<br>the REFOUT bit must be set to 0.                                                                                                                                                                                                                       |                                                                                                   |                                                              |                           |                                      |                              |                             |                              |

| [4]<br>CONT         | <ul> <li>Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long).</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long).</li> </ul>                                                                                                                                            |                                                                                                   |                                                              |                           |                                      |                              |                             |                              |

| [3:0]<br>ANAIN[3:0] | These bi<br>all packa<br>with eacl<br>able ana                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input Select<br>ts select the<br>ages for the 2<br>h package s<br>log inputs. L<br>ntrol/Status I | analog inpu<br>Z8 Encore! ><br>tyle, see the<br>Jsage of the | KP F082A S<br>Pin Descrip | eries. For in<br><u>otion</u> chapte | formation al<br>r on page 8. | oout port pin<br>Do not ena | is available<br>ble unavail- |

Table 73. ADC Control Register 0 (ADCCTL0)

| Bit   | Description (Continued)                                                                        |

|-------|------------------------------------------------------------------------------------------------|

| [1:0] | For 8-pin devices, the following voltages can be configured; for 20- and 28-pin devices, these |

|       | bits are reserved.                                                                             |

|       | 000000 = 0.00 V                                                                                |

|       | 000001 = 0.05 V                                                                                |

|       | 000010 = 0.10 V                                                                                |

|       | 000011 = 0.15 V                                                                                |

|       | 000100 = 0.20 V                                                                                |

|       | 000101 = 0.25 V                                                                                |

|       | 000110 = 0.30 V                                                                                |

|       | 000111 = 0.35 V                                                                                |

|       | 001000 = 0.40  V                                                                               |

|       | 001001 = 0.45 V                                                                                |

|       | 001010 = 0.50  V                                                                               |

|       | 001011 = 0.55 V                                                                                |

|       | 001100 = 0.60  V                                                                               |

|       | 001101 = 0.65 V                                                                                |

|       | 001110 = 0.70 V                                                                                |

|       | 001111 = 0.75 V                                                                                |

|       | 010000 = 0.80  V                                                                               |

|       | 010001 = 0.85  V                                                                               |

|       | 010010 = 0.90  V                                                                               |

|       | 010011 = 0.95  V                                                                               |

|       | 010100 = 1.00  V (Default)                                                                     |

|       | 010101 = 1.05  V                                                                               |

|       | 010110 = 1.10 V<br>010111 = 1.15 V                                                             |

|       | 01000 = 1.20  V                                                                                |

|       | 011001 = 1.25 V                                                                                |

|       | 011010 = 1.30  V                                                                               |

|       | 011011 = 1.35 V                                                                                |

|       | 011100 = 1.40  V                                                                               |

|       | 011101 = 1.45 V                                                                                |

|       | 011110 = 1.50 V                                                                                |

|       | 011111 = 1.55 V                                                                                |

|       | 100000 = 1.60  V                                                                               |

|       | 100001 = 1.65  V                                                                               |

|       | 100010 = 1.70  V                                                                               |

|       | 100011 = 1.75 V                                                                                |

|       | 100100 = 1.80  V                                                                               |

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

## Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

## **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | FF9H   |        |        |        |        |        |        |        |

Table 83. Flash Sector Protect Register (FPROT)

#### Bit Description

#### [7:0] Sector Protection

- SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

## Nonvolatile Data Storage

The Z8 Encore! XP F082A Series devices contain a nonvolatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

## Operation

The NVDS is implemented by special purpose Zilog software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note: Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes; see the <u>Part Selection Guide</u> section on page 2 for details. Devices containing 8KB of Flash memory do not include the NVDS feature.

## **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency (see **the** <u>Flash Operation Timing Using the Flash Frequency</u> <u>Registers</u> **section on page 149**).

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series device. When this option is enabled, several of the OCD commands are disabled. See Table 109.

<u>Table 110</u> on page 191 is a summary of the on-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 110 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | _                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                    |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Table 109. Debug Command Enable/Disable | Table 109. | Debug | Command | Enable/Disable |

|-----------------------------------------|------------|-------|---------|----------------|

|-----------------------------------------|------------|-------|---------|----------------|

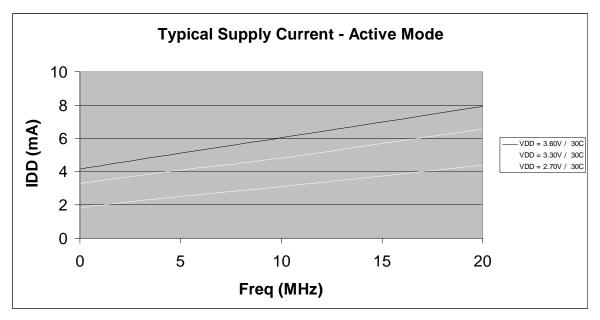

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode  $I_{\text{DD}}$  Versus System Clock Frequency

| ning (Continued) |  |

|------------------|--|

|                  |  |

#### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### $V_{DD}$ = 3.0 V to 3.6 V T<sub>A</sub> = 0°C to +70°C (unless otherwise stated)

| Symbol         | Parameter                               | Minimum | Typical | Maximum              | Units                          | Conditions                                                                                                                                                                                                                                |  |

|----------------|-----------------------------------------|---------|---------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                | Continuous Conversion<br>Time           | -       | 256     | _                    | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                                   |  |

|                |                                         |         | 512     |                      |                                | Temperature sensor measurement                                                                                                                                                                                                            |  |

|                | Signal Input Bandwidth                  | -       | 10      |                      | kHz                            | As defined by -3 dB point                                                                                                                                                                                                                 |  |

| R <sub>S</sub> | Analog Source<br>Impedance <sup>4</sup> | -       | _       | 10                   | kΩ                             | In unbuffered mode                                                                                                                                                                                                                        |  |

|                |                                         |         |         | 500                  | kΩ                             | In buffered modes                                                                                                                                                                                                                         |  |

| Zin            | Input Impedance                         | -       | 150     |                      | kΩ                             | In unbuffered mode at 20MHz <sup>5</sup>                                                                                                                                                                                                  |  |

|                |                                         | 10      | _       |                      | MΩ                             | In buffered modes                                                                                                                                                                                                                         |  |

| Vin            | Input Voltage Range                     | 0       |         | V <sub>DD</sub>      | V                              | Unbuffered Mode                                                                                                                                                                                                                           |  |

|                |                                         | 0.3     |         | V <sub>DD</sub> -1.1 | V                              | Buffered Modes<br>These values define<br>the range over which<br>the ADC performs<br>within spec; exceeding<br>these values does not<br>cause damage or insta-<br>bility; see DC Charac-<br>teristics for absolute<br>pin voltage limits. |  |

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

## **UART** Timing

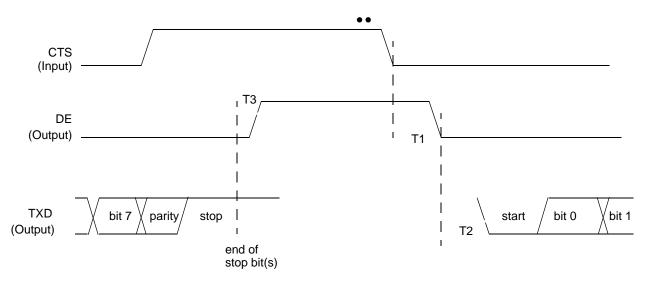

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

| Figure 37. | UART | Timing | With C | ٢S |

|------------|------|--------|--------|----|

|------------|------|--------|--------|----|

|                |                                                    | Delay (ns)                 |                                            |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | - 5                                        |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |  |  |

| Table 146. | IIART | Timina | With   | <b>CTS</b> |

|------------|-------|--------|--------|------------|

| Table 140. |       | runng  | VVILII | 613        |

| Part Number         | Flash    | RAM     | SDVN  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|----------|---------|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |          |         |       | h         |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |          |         |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | re: –40° | C to 10 | )5°C  |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix