Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K × 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082asj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Low-Power Modes

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP Mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT Mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT Mode).

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP Mode, powering down all peripherals except the Voltage Brown-Out detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; X<sub>IN</sub> and X<sub>OUT</sub> (if previously enabled) are disabled and PA0/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash option bit, the Voltage Brown-Out protection circuit continues to operate

- Low-power operational amplifier continues to operate if enabled by the Power Control Register

- All other on-chip peripherals are idle

To minimize current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see the <u>Reset, Stop Mode Recovery and Low Voltage Detection</u> chapter on page 22.

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

| Bit     | 7                                                                                     | 6                             | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|---------------------------------------------------------------------------------------|-------------------------------|------|------|------|------|------|------|

| Field   | POC7                                                                                  | POC6                          | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D) |      |      |      |      |      |      |

| R/W     | R/W                                                                                   | R/W                           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |                               |      |      |      |      |      |      |

| D:4     | Decertation                                                                           |                               |      |      |      |      |      |      |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

#### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PHDE7     | PHDE6        | PHDE5       | PHDE4         | PHDE3        | PHDE2        | PHDE1        | PHDE0    |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | lf 04H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit        | Description                                                       |

|------------|-------------------------------------------------------------------|

| [7:0]      | Port High Drive Enabled                                           |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |

|            | 1 = The port pin is configured for high output current drive.     |

| Note: x in | dicates the specific GPIO port pin number (7–0).                  |

66

| IRQ2ENH[ <i>x</i> ] | IRQ2ENL[x] | Priority | Description |

|---------------------|------------|----------|-------------|

| 0                   | 0          | Disabled | Disabled    |

| 0                   | 1          | Level 1  | Low         |

| 1                   | 0          | Level 2  | Medium      |

| 1                   | 1          | Level 3  | High        |

#### Table 44. IRQ2 Enable and Priority Encoding

#### Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|------|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |      |     |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |          | FC7H |     |     |       |       |       |       |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                  |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                  |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                  |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                  |

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

## **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

### Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                               | 6           | 5    | 4        | 3   | 2    | 1   | 0      |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------|-----|------|-----|--------|

| Field          | TMODEHI                                                                                                                                                                                                                                                                                                                                         | TICO        | NFIG | Reserved |     | PWMD |     | INPCAP |

| RESET          | 0                                                                                                                                                                                                                                                                                                                                               | 0           | 0    | 0        | 0   | 0    | 0   | 0      |

| R/W            | R/W                                                                                                                                                                                                                                                                                                                                             | R/W         | R/W  | R/W      | R/W | R/W  | R/W | R      |

| Address        |                                                                                                                                                                                                                                                                                                                                                 | F06H, F0EH  |      |          |     |      |     |        |

| Bit            | Descript                                                                                                                                                                                                                                                                                                                                        | Description |      |          |     |      |     |        |

| [7]<br>TMODEHI | <b>Timer Mode High Bit</b><br>This bit, along with the TMODE field in the TxCTL1 Register, determines the operating<br>mode of the timer. This bit is the most significant bit of the Timer mode selection value. See<br>the description of the <u>Timer 0–1 Control Register 1 (TxCTL1)</u> for details about the full timer<br>mode decoding. |             |      |          |     |      |     |        |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

#### **WDT Reset in Normal Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1. For more information about system reset, see the <u>Reset, Stop Mode</u> <u>Recovery and Low Voltage Detection</u> chapter on page 22.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following WDT time-out in STOP Mode.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. Observe the following steps to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU) with the appropriate time-out value.

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH) with the appropriate time-out value.

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL) with the appropriate time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

## Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page; see Tables 100 and 101 on page 173 for details. Loading these values

PRELIMINARY

#### Table 62. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit                                                                                          | 7          | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------------------------------------------------------------|------------|------|---|---|---|---|---|---|

| Field                                                                                        |            | WDTL |   |   |   |   |   |   |

| RESET                                                                                        |            | 00H  |   |   |   |   |   |   |

| R/W                                                                                          |            | R/W* |   |   |   |   |   |   |

| Address                                                                                      | FF3H       |      |   |   |   |   |   |   |

| Note: A read returns the current WDT count value; a write sets the appropriate reload value. |            |      |   |   |   |   |   |   |

| Bit                                                                                          | Descriptio | n    |   |   |   |   |   |   |

| Dit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Low                                                           |

| WDTL  | Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

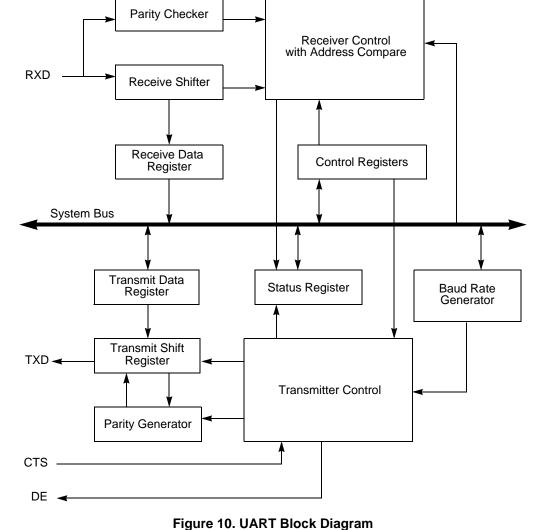

first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low start bit and ends with either 1 or 2 active High stop bits. Figures 11 and 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

### Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect Register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select Register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the Page Select Register to unlock the Flash Controller is not necessary.

- The Page Select Register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control Register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 153

Flash Status Register: see page 155

Flash Page Select Register: see page 156

Flash Sector Protect Register: see page 157

Flash Frequency High and Low Byte Registers: see page 157

### **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FCTL) Register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select Register. Mass Erase is enabled only through the On-Chip

## **Option Bit Types**

This section describes the five types of Flash option bits.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 of the program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

• Note: The trim address range is from information address 20–3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory-programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in See the <u>Flash Information Area</u> section on page 17.

#### **Serialization Bits**

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 90 through Table 95.

## Trim Bit Address 0000H

| Bit       | 7           | 6             | 5             | 4           | 3           | 2    | 1   | 0   |  |  |  |

|-----------|-------------|---------------|---------------|-------------|-------------|------|-----|-----|--|--|--|

| Field     | Reserved    |               |               |             |             |      |     |     |  |  |  |

| RESET     | U           | U             | U             | U           | U           | U    | U   | U   |  |  |  |

| R/W       | R/W         | R/W           | R/W           | R/W         | R/W         | R/W  | R/W | R/W |  |  |  |

| Address   |             |               | Infor         | mation Page | e Memory 00 | )20H |     |     |  |  |  |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | e.          |             |      |     |     |  |  |  |

| Bit       | Description |               |               |             |             |      |     |     |  |  |  |

| [7:0]     | Reserved    |               |               |             |             |      |     |     |  |  |  |

#### Table 90. Trim Options Bits at Address 0000H

These bits are reserved; altering this register may result in incorrect device operation.

### Trim Bit Address 0001H

#### Table 91. Trim Option Bits at 0001H

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| Field     | Reserved                                        |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 0021H                   |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

## Bit Description [7:0] Reserved These bits are reserved; altering this register may result in incorrect device operation.

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

DBG  $\leftarrow$  09H DBG  $\leftarrow$  {4'h0,Register Address[11:8] DBG  $\leftarrow$  Register Address[7:0] DBG  $\leftarrow$  Size[7:0] DBG  $\rightarrow$  1-256 data bytes

**Write Program Memory (0AH).** The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Write Data Memory (0CH).** The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0CH DBG  $\leftarrow$  Data Memory Address[15:8] DBG  $\leftarrow$  Data Memory Address[7:0]

#### Table 123. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

#### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

#### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

|               |                                         |                 |      | •           |       |   |   | ' |   |   |                |                 |

|---------------|-----------------------------------------|-----------------|------|-------------|-------|---|---|---|---|---|----------------|-----------------|

| Assembly      |                                         | Address<br>Mode |      | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

| Mnemonic      | Symbolic Operation                      | dst src         |      | (Hex)       |       | Ζ | S | V | D | Н | s              | s               |

| JR dst        | $PC \gets PC + X$                       | DA              |      | 8B          | _     | _ | _ | _ | _ | _ | 2              | 2               |

| JR cc, dst    | if cc is true<br>PC $\leftarrow$ PC + X | DA              |      | 0B-FB       | _     | - | - | _ | - | _ | 2              | 2               |

| LD dst, rc    | dst $\leftarrow$ src                    | r               | IM   | 0C-FC       | _     | _ | _ | _ | _ | _ | 2              | 2               |

|               |                                         | r               | X(r) | C7          | -     |   |   |   |   |   | 3              | 3               |

|               |                                         | X(r)            | r    | D7          | -     |   |   |   |   |   | 3              | 4               |

|               |                                         | r               | lr   | E3          | -     |   |   |   |   |   | 2              | 3               |

|               |                                         | R               | R    | E4          | -     |   |   |   |   |   | 3              | 2               |

|               |                                         | R               | IR   | E5          | -     |   |   |   |   |   | 3              | 4               |

|               |                                         | R               | IM   | E6          | _     |   |   |   |   |   | 3              | 2               |

|               |                                         | IR              | IM   | E7          | _     |   |   |   |   |   | 3              | 3               |

|               |                                         | lr              | r    | F3          | _     |   |   |   |   |   | 2              | 3               |

|               |                                         | IR              | R    | F5          | _     |   |   |   |   |   | 3              | 3               |

| LDC dst, src  | dst $\leftarrow$ src                    | r               | Irr  | C2          | _     | _ | _ | _ | _ | _ | 2              | 5               |

|               |                                         | lr              | Irr  | C5          | _     |   |   |   |   |   | 2              | 9               |

|               |                                         | Irr             | r    | D2          | _     |   |   |   |   |   | 2              | 5               |

| LDCI dst, src | dst ← src                               | lr              | Irr  | C3          | _     | _ | _ | _ | _ | _ | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | D3          | _     |   |   |   |   |   | 2              | 9               |

| LDE dst, src  | dst ← src                               | r               | Irr  | 82          | _     | _ | _ | _ | _ | _ | 2              | 5               |

|               |                                         | Irr             | r    | 92          | -     |   |   |   |   |   | 2              | 5               |

| LDEI dst, src | dst $\leftarrow$ src                    | lr              | Irr  | 83          | _     | - | _ | _ | _ | - | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | 93          | -     |   |   |   |   |   | 2              | 9               |

| LDWX dst, src | dst ← src                               | ER              | ER   | 1FE8        | _     | _ | _ | - | _ | _ | 5              | 4               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

#### 232

## **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                              | T <sub>A</sub> = -40°C<br>(unless c | V to 3.6V<br>to +105°C<br>otherwise<br>ted) |       |                                                                                                           |  |  |

|---------------------|------------------------------|-------------------------------------|---------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                    | Minimum                             | Maximum                                     | Units | Conditions                                                                                                |  |  |

| F <sub>SYSCLK</sub> | System Clock Frequency       | -                                   | 20.0                                        | MHz   | Read-only from Flash mem-<br>ory                                                                          |  |  |

|                     |                              | 0.032768                            | 20.0                                        | MHz   | Program or erasure of the<br>Flash memory                                                                 |  |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                   | 20.0                                        | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an exter-<br>nal clock driver |  |  |

| T <sub>XIN</sub>    | System Clock Period          | 50                                  | -                                           | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                  |  |  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                  | 30                                          | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |  |  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                  | 30                                          | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |  |  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                   | 3                                           | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |  |  |

| T <sub>XINF</sub>   | System Clock Fall Time       | _                                   | 3                                           | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |  |  |

#### Table 134. Internal Precision Oscillator Electrical Characteristics

|                    |                                                           | T <sub>A</sub> = - | = 2.7V to<br>-40°C to +<br>otherwise |            |       |                                         |

|--------------------|-----------------------------------------------------------|--------------------|--------------------------------------|------------|-------|-----------------------------------------|

| Symbol             | Parameter                                                 | Minimum            | Typical                              | Maximum    | Units | Conditions                              |

| F <sub>IPO</sub>   | Internal Precision Oscillator Fre-<br>quency (High Speed) |                    | 5.53                                 |            | MHz   | $V_{DD} = 3.3 V$<br>$T_A = 30^{\circ}C$ |

| F <sub>IPO</sub>   | Internal Precision Oscillator Fre-<br>quency (Low Speed)  |                    | 32.7                                 |            | kHz   | $V_{DD} = 3.3 V$<br>$T_A = 30^{\circ}C$ |

| F <sub>IPO</sub>   | Internal Precision Oscillator Error                       |                    | <u>+</u> 1                           | <u>+</u> 4 | %     |                                         |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time             |                    | 3                                    |            | μs    |                                         |

| Part Number         | Flash     | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|-----------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |           |         | (B Flas | sh        |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |           |         |         |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40° | C to 10 | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

#### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Jaquin<br>Munu<br>Lue<br>Z8 Encore! XP F082A | Lash<br>E<br>Series | W<br>V<br>With 11 | SO<br>N<br>(B Flas | y<br>1/0 Lines | Hit Interrupts | e 16-Bit Timers w/PWM | 6<br>4<br>10-Bit A/D Channels | ici<br>UART with IrDA | comparator | Temperature Sensor | Description         |

|----------------------------------------------|---------------------|-------------------|--------------------|----------------|----------------|-----------------------|-------------------------------|-----------------------|------------|--------------------|---------------------|

| Standard Temperatu                           |                     |                   |                    | -              |                |                       | -                             | •                     |            |                    |                     |

| Z8F012APB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu                           | re: –40'            | °C to 10          | 5°C                |                |                |                       |                               |                       |            |                    |                     |

| Z8F012APB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | PDIP 28-pin package |

#### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

# Index

### **Numerics**

10-bit ADC 6

## Α

absolute maximum ratings 226 AC characteristics 232 ADC 208 architecture 124 block diagram 125 continuous conversion 127 control register 134, 135 control register definitions 133 data high byte register 136 data low bits register 137 electrical characteristics and timing 236 operation 125 single-shot conversion 126 ADCCTL register 134, 135 ADCDH register 136 ADCDL register 137 **ADCX 208** ADD 208 add - extended addressing 208 add with carry 208 add with carry - extended addressing 208 additional symbols 207 address space 15 **ADDX 208** analog signals 11 analog-to-digital converter (ADC) 124 AND 210 **ANDX 210** arithmetic instructions 208 assembly language programming 204 assembly language syntax 205

## В

B 207

**BCLR 209** binary number suffix 207 **BIT 209** bit 206 clear 209 manipulation instructions 209 set 209 set or clear 209 swap 209 test and jump 211 test and jump if non-zero 211 test and jump if zero 211 bit jump and test if non-zero 211 bit swap 211 block diagram 3 block transfer instructions 209 **BRK 211 BSET 209** BSWAP 209, 211 BTJ 211 BTJNZ 211 **BTJZ 211**

baud rate generator, UART 110

## С

b 206

CALL procedure 211 CAPTURE mode 87, 88 CAPTURE/COMPARE mode 88 cc 206 CCF 209 characteristics, electrical 226 clear 210 CLR 210 COM 210 compare 87 compare - extended addressing 208 COMPARE mode 87 compare with carry 208

Z8 Encore! XP<sup>®</sup> F082A Series

**Product Specification**

**Product Specification**

Power-on and Voltage Brownout electrical charac-

power supply signals 12

teristics and timing 233

program counter 207

program memory 15

PWM mode 87.88

PxCTL register 46

PxADDR register 45

**PUSH 210**

PUSHX 210

R

Power-On Reset (POR) 24

program control instructions 211

push using extended addressing 210

Z8 Encore! XP<sup>®</sup> F082A Series

read program memory (0BH) 189 read program memory CRC (0EH) 190 read register (09H) 189 read runtime counter (03H) 187 step instruction (10H) 190 stuff instruction (11H) 190 write data memory (0CH) 189 write OCD control register (04H) 188 write program counter (06H) 188 write program memory (0AH) 189 write register (08H) 188 on-chip debugger (OCD) 180 on-chip debugger signals 11 on-chip oscillator 198 **ONE-SHOT** mode 87 opcode map abbreviations 223 cell description 222 first 224 second after 1FH 225 Operational Description 22, 32, 36, 55, 70, 93, 99, 120, 124, 139, 140, 144, 146, 159, 176, 180, 193, 198.203 OR 210 ordering information 246 **ORX 210** oscillator signals 11

### Ρ

p 206 Packaging 245 part selection guide 2 PC 207 peripheral AC and DC electrical characteristics 233 pin characteristics 12 **Pin Descriptions 8** polarity 206 POP 210 pop using extended addressing 210 **POPX 210** port availability, device 36 port input timing (GPIO) 240 port output timing, GPIO 241

R 206 r 206 RA register address 206 RCF 209, 210 receive IrDA data 122 receiving UART data-interrupt-driven method 104 receiving UART data-polled method 103 register 206 ADC control (ADCCTL) 134, 135 ADC data high byte (ADCDH) 136 ADC data low bits (ADCDL) 137 flash control (FCTL) 155, 161, 162 flash high and low byte (FFREQH and FRE-EQL) 157 flash page select (FPS) 156, 157 flash status (FSTAT) 155 GPIO port A-H address (PxADDR) 45 GPIO port A-H alternate function sub-registers 47 GPIO port A-H control address (PxCTL) 46 GPIO port A-H data direction sub-registers 46 OCD control 191 OCD status 192 UARTx baud rate high byte (UxBRH) 117

UARTx baud rate low byte (UxBRL) 117 UARTx Control 0 (UxCTL0) 111, 117

261