Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                   |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | 8500                                                                       |

| Number of Logic Elements/Cells | 68000                                                                      |

| Total RAM Bits                 | 1056768                                                                    |

| Number of I/O                  | 500                                                                        |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 672-BBGA                                                                   |

| Supplier Device Package        | 672-FPBGA (27x27)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfe2-70e-5f672i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP2/M Family Data Sheet Architecture

#### September 2013

Data Sheet DS1006

## **Architecture Overview**

Each LatticeECP2/M device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and rows of sys-DSP<sup>™</sup> Digital Signal Processing blocks, as shown in Figure 2-1. In addition, the LatticeECP2M family contains SERDES Quads in one or more of the corners. Figure 2-2 shows the block diagram of ECP2M20 with one quad.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional Unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

The LatticeECP2/M devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large dedicated 18K fast memory blocks. Each sysMEM block can be configured in a variety of depths and widths of RAM or ROM. In addition, LatticeECP2/M devices contain up to two rows of DSP Blocks. Each DSP block has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

The LatticeECP2M devices feature up to 16 embedded 3.125Gbps SERDES (Serializer / Deserializer) channels. Each SERDES channel contains independent 8b/10b encoding / decoding, polarity adjust and elastic buffer logic. Each group of four SERDES channels along with its Physical Coding Sub-layer (PCS) block, creates a quad. The functionality of the SERDES/PCS Quads can be controlled by memory cells set during device configuration or by registers that are addressable during device operation. The registers in every quad can be programmed by a soft IP interface, referred to as the SERDES Client Interface (SCI). These quads (up to four) are located at the corners of the devices.

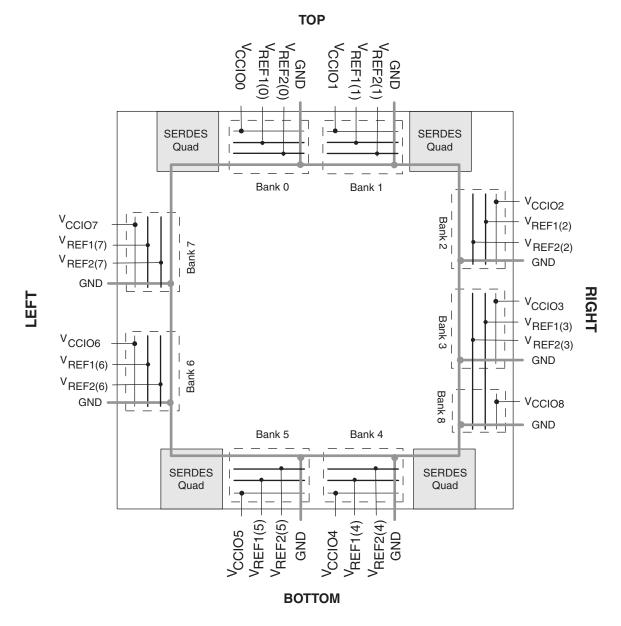

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysl/O buffers. The sysl/O buffers of the LatticeECP2/M devices are arranged in eight banks, allowing the implementation of a wide variety of I/O standards. In addition, a separate I/O bank is provided for the programming interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as SPI4.2, along with memory interfaces including DDR2.

The LatticeECP2/M registers in PFU and sysl/O can be configured to be SET or RESET. After power up and the device is configured, it enters into user mode with these registers SET/RESET according to the configuration setting, allowing the device entering to a known state for predictable system function.

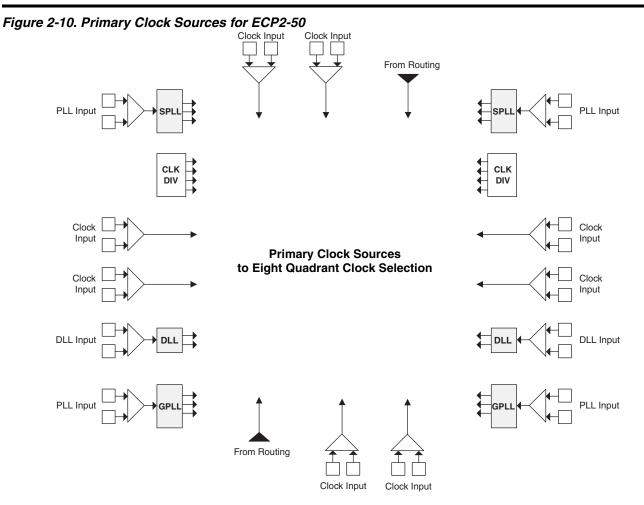

Other blocks provided include PLLs, DLLs and configuration functions. The LatticeECP2/M architecture provides two General PLLs (GPLL) and up to six Standard PLLs (SPLL) per device. In addition, each LatticeECP2/M family member provides two DLLs per device. The GPLLs and DLLs blocks are located in pairs at the end of the bottommost EBR row; the DLL block is located towards the edge of the device. The SPLL blocks are located at the end of the other EBR/DSP rows.

The configuration block that supports features such as configuration bit-stream decryption, transparent updates and dual boot support is located toward the center of this EBR row. The Ball Grid Array (BGA) package devices in the LatticeECP2/M family supports a sysCONFIG<sup>™</sup> port located in the corner between banks four and five, which allows for serial or parallel device configuration.

In addition, every device in the family has a JTAG port. This family also provides an on-chip oscillator. The LatticeECP2/M devices use 1.2V as their core voltage.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

# Routing

There are many resources provided in the LatticeECP2/M devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU). The x1 and x2 connections provide fast and efficient connections in horizontal and vertical directions. The x2 and x6 resources are buffered, allowing the routing of both short and long connections between PFUs.

The LatticeECP2/M family has an enhanced routing architecture that produces a compact design. The Diamond design software takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

# sysCLOCK Phase Locked Loops (GPLL/SPLL)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. All the devices in the LatticeECP2/M family support two General Purpose PLLs (GPLLs) which are full-featured PLLs. In addition, some of the larger devices have two to six Standard PLLs (SPLLs) that have a subset of GPLL functionality.

## General Purpose PLL (GPLL)

The architecture of the GPLL is shown in Figure 2-5. A description of the GPLL functionality follows.

CLKI is the reference frequency (generated either from the pin or from routing) for the PLL. CLKI feeds into the Input Clock Divider block. The CLKFB is the feedback signal (generated from CLKOP or from a user clock PIN/ logic). This signal feeds into the Feedback Divider. The Feedback Divider is used to multiply the reference frequency.

The Delay Adjust Block adjusts either the delays of the reference or feedback signals. The Delay Adjust Block can either be programmed during configuration or can be adjusted dynamically. The setup, hold or clock-to-out times of the device can be improved by programming a delay in the feedback or input path of the PLL, which will advance or delay the output clock with reference to the input clock.

Following the Delay Adjust Block, both the input path and feedback signals enter the Voltage Controlled Oscillator (VCO) block. In this block the difference between the input path and feedback signals is used to control the frequency and phase of the oscillator. A LOCK signal is generated by the VCO to indicate that the VCO has locked onto the input clock signal. In dynamic mode, the PLL may lose lock after a dynamic delay adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. LatticeECP2/M devices have two dedicated pins on the left and right edges of the device for connecting optional external capacitors to the VCO. This allows the PLLs to operate at a lower frequency. This is a shared resource that can only be used by one PLL (GPLL or SPLL) per side.

The output of the VCO then enters the post-scalar divider. The post-scalar divider allows the VCO to operate at higher frequencies than the clock output (CLKOP), thereby increasing the frequency range. A secondary divider takes the CLKOP signal and uses it to derive lower frequency outputs (CLKOK). The Phase/Duty Select block adjusts the phase and duty cycle of the CLKOP signal and generates the CLKOS signal. The phase/duty cycle setting can be pre-programmed or dynamically adjusted.

The primary output from the post scalar divider CLKOP along with the outputs from the secondary divider (CLKOK) and Phase/Duty select (CLKOS) are fed to the clock distribution network.

Note: This diagram shows sources for the ECP2-50 device. Smaller LatticeECP2 devices have fewer SPLLs. All LatticeECP2M devices have six SPLLs.

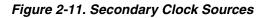

### Secondary Clock/Control Sources

LatticeECP2/M devices derive secondary clocks (SC0 through SC7) from eight dedicated clock input pads and the rest from routing. Figure 2-11 shows the secondary clock sources.

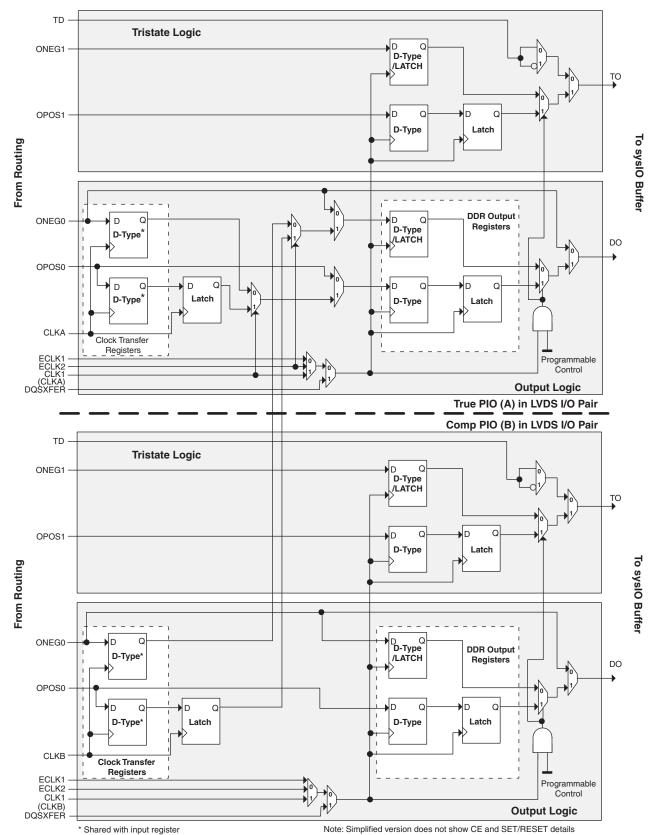

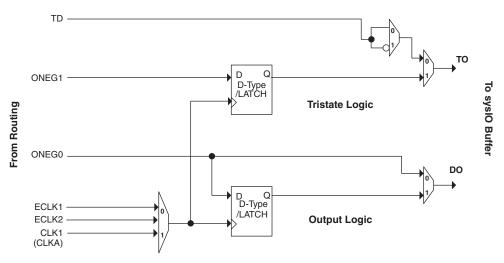

Figure 2-31. Output and Tristate Block for Left, Right and Bottom Edges

Figure 2-32. Output and Tristate Block, Top Edge

Note: Simplified version does not show CE and SET/RESET details.

## Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-31 shows the diagram of the Tristate Register Block with the Output Block for the left, right and bottom edges and Figure 2-32 shows the diagram of the Tristate Register Block with the Output Block for the top edge.

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG1 and OPOS1 are fed into registers on the positive edge of the clock. Then in the next clock the registered OPOS1 is latched. A multiplexer running off the same clock cycle selects the correct register for feeding to the output (D0).

## **Control Logic Block**

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock is selected from one of the clock signals provided from the general purpose routing, one of the edge clocks (ECLK1/ ECLK2) and a DQS signal provided from the programmable DQS pin and provided to the input register block. The clock can optionally be inverted.

# DDR Memory Support

Certain PICs have additional circuitry to allow the implementation of high speed source synchronous and DDR memory interfaces. The support varies by the edge of the device as detailed below.

## Left and Right Edges

PICs on these edges have registered elements that support DDR memory interfaces. One of every 16 PIOs contains a delay element to facilitate the generation of DQS signals. The DQS signal feeds the DQS bus that spans the set of 16 PIOs. Figure 2-33 shows the assignment of DQS pins in each set of 16 PIOs.

## **Bottom Edge**

PICs on the bottom edge have registered elements that support DDR memory interfaces. One of every 18 PIOs contains a delay element to facilitate the generation of DQS signals. The DQS signal feeds the DQS bus that spans the set of 18 PIOs. Figure 2-34 shows the assignment of DQS pins in each set of 18 PIOs.

### Figure 2-38. LatticeECP2M Banks

LatticeECP2/M devices contain two types of sysI/O buffer pairs.

#### 1. Top (Bank 0 and Bank 1) sysl/O Buffer Pairs (Single-Ended Outputs Only)

The sysl/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

#### 2. Bottom (Bank 4 and Bank 5) sysl/O Buffer Pairs (Single-Ended Outputs Only)

The sysI/O buffer pairs in the bottom banks of the device consist of two single-ended output drivers and two

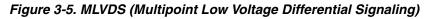

### MLVDS

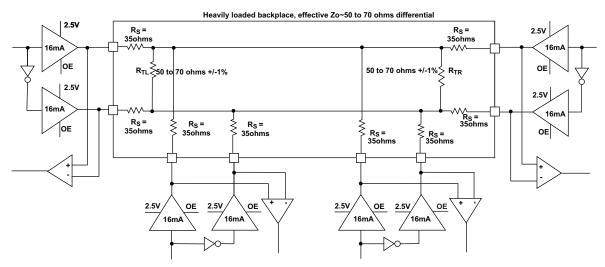

The LatticeECP2/M devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Table 3-6. MLVDS DC Conditions<sup>1</sup>

|                   |                                  | Тур            | oical          |       |

|-------------------|----------------------------------|----------------|----------------|-------|

| Parameter         | Description                      | <b>Ζο=50</b> Ω | <b>Ζο=70</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)     | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                 | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)   | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%) | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)     | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage              | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage               | 0.98           | 0.90           | V     |

| V <sub>OD</sub>   | Output Differential Voltage      | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage       | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                | 21.74          | 20.00          | mA    |

1. For input buffer, see LVDS table.

For further information about LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see the list of additional technical information at the end of this data sheet.

### Table 3-18. Reference Clock

| Symbol                         | Description                      | Test Conditions | Min. | Тур. | Max. | Units |

|--------------------------------|----------------------------------|-----------------|------|------|------|-------|

| F <sub>REFCLK</sub>            | Reference clock frequency        |                 | —    | 100  |      | MHz   |

| V <sub>CM</sub>                | Input common mode voltage        |                 | —    | 0.65 |      | V     |

| T <sub>R</sub> /T <sub>F</sub> | Clock input rise/fall time       |                 | _    | _    | 1.0  | ns    |

| V <sub>SW</sub>                | Differential input voltage swing |                 | 0.6  | —    | 1.6  | V     |

| DC <sub>REFCLK</sub>           | Input clock duty cycle           |                 | 40   | 50   | 60   | %     |

| PPM                            | Reference clock tolerance        |                 | -300 | _    | +300 | ppm   |

# LFE2-6E/SE and LFE2-12E/SE Logic Signal Connections: 144 TQFP (Cont.)

|               |                     | LFE2 | -6E/SE            |              |                     | L    | FE2-12E/12SE      |              |

|---------------|---------------------|------|-------------------|--------------|---------------------|------|-------------------|--------------|

| Pin<br>Number | Pin/Pad<br>Function | Bank | Dual Function     | Differential | Pin/Pad<br>Function | Bank | Dual<br>Function  | Differential |

| 91            | PR20B               | 3    | RLM0_GPLLC_IN_A** | C (LVDS)*    | PR20B               | 3    | RLM0_GPLLC_IN_A** | C (LVDS)*    |

| 92            | PR20A               | 3    | RLM0_GPLLT_IN_A** | T (LVDS)*    | PR20A               | 3    | RLM0_GPLLT_IN_A** | T (LVDS)*    |

| 93            | RLM0_PLLCAP         | 3    |                   |              | RLM0_PLLCAP         | 3    |                   |              |

| 94            | VCC                 | -    |                   |              | VCC                 | -    |                   |              |

| 95            | GND                 | -    |                   |              | GND                 | -    |                   |              |

| 96            | PR17B               | 3    | RLM0_GDLLC_IN_A** | C (LVDS)*    | PR17B               | 3    | RLM0_GDLLC_IN_A** | C (LVDS)*    |

| 97            | PR17A               | 3    | RLM0_GDLLT_IN_A** | T (LVDS)*    | PR17A               | 3    | RLM0_GDLLT_IN_A** | T (LVDS)*    |

| 98            | PR16B               | 3    | VREF2_3           | С            | PR16B               | 3    | VREF2_3           | С            |

| 99            | PR16A               | 3    | VREF1_3           | Т            | PR16A               | 3    | VREF1_3           | Т            |

| 100           | PR15B               | 3    | PCLKC3_0          | C (LVDS)*    | PR15B               | 3    | PCLKC3_0          | C (LVDS)*    |

| 101           | PR15A               | 3    | PCLKT3_0          | T (LVDS)*    | PR15A               | 3    | PCLKT3_0          | T (LVDS)*    |

| 102           | VCC                 | -    |                   |              | VCC                 | -    |                   |              |

| 103           | PR13B               | 2    | PCLKC2_0/RDQ10    | С            | PR13B               | 2    | PCLKC2_0/RDQ10    | С            |

| 104           | PR13A               | 2    | PCLKT2_0/RDQ10    | Т            | PR13A               | 2    | PCLKT2_0/RDQ10    | Т            |

| 105           | GND                 | -    |                   |              | GND                 | -    |                   |              |

| 106           | VCCIO2              | 2    |                   |              | VCCIO2              | 2    |                   |              |

| 107           | PR2B                | 2    | VREF2_2           | C (LVDS)*    | PR2B                | 2    | VREF2_2           | C (LVDS)*    |

| 108           | PR2A                | 2    | VREF1_2           | T (LVDS)*    | PR2A                | 2    | VREF1_2           | T (LVDS)*    |

| 109           | PT28B               | 1    | VREF2_1           | С            | PT55B               | 1    | VREF2_1           | С            |

| 110           | PT28A               | 1    | VREF1_1           | Т            | PT55A               | 1    | VREF1_1           | Т            |

| 111           | PT26B               | 1    |                   | С            | PT54B               | 1    |                   | С            |

| 112           | PT26A               | 1    |                   | Т            | PT54A               | 1    |                   | Т            |

| 113           | PT24B               | 1    |                   | С            | PT52B               | 1    |                   | С            |

| 114           | PT24A               | 1    |                   | Т            | PT52A               | 1    |                   | Т            |

| 115           | PT22B               | 1    |                   | С            | PT50B               | 1    |                   | С            |

| 116           | PT22A               | 1    |                   | Т            | PT50A               | 1    |                   | Т            |

| 117           | VCCIO1              | 1    |                   |              | VCCIO1              | 1    |                   |              |

| 118           | PT20B               | 1    |                   | С            | PT48B               | 1    |                   | С            |

| 119           | PT20A               | 1    |                   | Т            | PT48A               | 1    |                   | Т            |

| 120           | GND                 | -    |                   |              | GND                 | -    |                   |              |

| 121           | PT18B               | 1    |                   | С            | PT44B               | 1    |                   | С            |

| 122           | PT18A               | 1    |                   | Т            | PT44A               | 1    |                   | Т            |

| 123           | PT16A               | 1    |                   |              | PT40B               | 1    |                   | С            |

| 124           | NC                  | 1    |                   |              | PT40A               | 1    |                   | Т            |

| 125           | PT14B               | 1    |                   | С            | PT34B               | 1    |                   | С            |

| 126           | PT14A               | 1    |                   | Т            | PT34A               | 1    |                   | Т            |

| 127           | NC                  | 1    |                   |              | NC                  | 1    |                   |              |

| 128           | VCC                 | -    |                   |              | VCC                 | -    |                   |              |

| 129           | PT12B               | 1    | PCLKC1_0          | С            | PT30B               | 1    | PCLKC1_0          | С            |

| 130           | PT12A               | 1    | PCLKT1_0          | Т            | PT30A               | 1    | PCLKT1_0          | Т            |

| 131           | PT10B               | 0    | PCLKC0_0          | С            | PT28B               | 0    | PCLKC0_0          | С            |

| 132           | XRES                | 0    |                   |              | XRES                | 0    |                   |              |

| 133           | GND                 | -    |                   |              | GND                 | -    |                   |              |

| 134           | PT10A               | 0    | PCLKT0_0          | Т            | PT28A               | 0    | PCLKT0_0          | Т            |

| 135           | VCC                 | -    |                   |              | VCC                 | -    |                   |              |

# LFE2-20E/SE Logic Signal Connections: 256 fpBGA (Cont.)

|                |             | LFE2-2            | 20E/SE |               |              |

|----------------|-------------|-------------------|--------|---------------|--------------|

| Ball<br>Number | Ball Number | Ball/Pad Function | Bank   | Dual Function | Differential |

| VCCIO          | VCCIO       | VCCIO1            | 1      |               |              |

| D12            | D12         | PT62A             | 1      |               | Т            |

| B14            | B14         | PT61B             | 1      |               | С            |

| C14            | C14         | PT60B             | 1      |               | С            |

| A14            | A14         | PT61A             | 1      |               | Т            |

| D13            | D13         | PT60A             | 1      |               | Т            |

| C13            | C13         | PT59B             | 1      |               | С            |

| GND            | GND         | GNDIO1            | -      |               |              |

| A13            | A13         | PT58B             | 1      |               | С            |

| B13            | B13         | PT59A             | 1      |               | Т            |

| VCCIO          | VCCIO       | VCCIO1            | 1      |               |              |

| A12            | A12         | PT58A             | 1      |               | Т            |

| B11            | B11         | PT57B             | 1      |               | С            |

| D11            | D11         | PT56B             | 1      |               | С            |

| A11            | A11         | PT57A             | 1      |               | Т            |

| C11            | C11         | PT56A             | 1      |               | Т            |

| -              | GND         | GNDIO1            | 1      |               |              |

| -              | VCC         | VCCIO             | 1      |               |              |

| D10            | D10         | PT46B             | 1      |               | С            |

| C10            | C10         | PT46A             | 1      |               | Т            |

| GND            | GND         | GNDIO1            | -      |               |              |

| B10            | B10         | PT45B             | 1      |               | С            |

| A9             | A9          | PT44B             | 1      |               | С            |

| A10            | A10         | PT45A             | 1      |               | Т            |

| B9             | B9          | PT44A             | 1      |               | Т            |

| VCCIO          | VCCIO       | VCCIO1            | 1      |               |              |

| A8             | A8          | PT43B             | 1      |               | С            |

| D9             | D9          | PT42B             | 1      |               | С            |

| B8             | B8          | PT43A             | 1      |               | т            |

| C9             | C9          | PT42A             | 1      |               | Т            |

| GND            | GND         | GNDIO1            | -      |               |              |

| B7             | B7          | PT41B             | 1      |               | С            |

| E9             | E9          | PT40B             | 1      |               | C            |

| A7             | A7          | PT41A             | 1      |               | T            |

| D8             | D8          | PT40A             | 1      |               | T            |

| VCCIO          | VCCIO       | VCCIO1            | 1      |               | · ·          |

| A6             | A6          | PT39B             | 1      | PCLKC1_0      | С            |

| B6             | B6          | PT39A             | 1      | PCLKT1_0      | T            |

| E6             | E6          | XRES              | 1      |               | · ·          |

| F8             | <br>F8      | PT37B             | 0      | PCLKC0_0      | С            |

| GND            | GND         | GNDIO0            | -      |               |              |

| E8             | E8          | PT37A             | 0      | PCLKT0_0      | т            |

# LFE2-12E/SE and LFE2-20E/SE Logic Signal Connections: 484 fpBGA (Cont.)

|                |                      | LFE2- | 12E/12SE       |              |                      |      | LFE2-20E/20SE  |              |

|----------------|----------------------|-------|----------------|--------------|----------------------|------|----------------|--------------|

| Ball<br>Number | Ball/Pad<br>Function | Bank  | Dual Function  | Differential | Ball/Pad<br>Function | Bank | Dual Function  | Differential |

| T7             | PL29B                | 6     | LDQ28          | С            | PL43B                | 6    | LDQ42          | С            |

| Т6             | PL26B                | 6     | LDQ28          | C (LVDS)*    | PL40B                | 6    | LDQ42          | C (LVDS)*    |

| AA2            | PL31A                | 6     | LDQ28          | Т            | PL45A                | 6    | LDQ42          | Т            |

| VCCIO          | VCCIO6               | 6     |                |              | VCCIO6               | 6    |                |              |

| Y1             | PL28A                | 6     | LDQS28         | T (LVDS)*    | PL42A                | 6    | LDQS42         | T (LVDS)*    |

| AA1            | PL31B                | 6     | LDQ28          | С            | PL45B                | 6    | LDQ42          | С            |

| W1             | PL28B                | 6     | LDQ28          | C (LVDS)*    | PL42B                | 6    | LDQ42          | C (LVDS)*    |

| V3             | PL30B                | 6     | LDQ28          | C (LVDS)*    | PL44B                | 6    | LDQ42          | C (LVDS)*    |

| GNDIO          | GNDIO6               | -     |                |              | GNDIO                | -    |                |              |

| V4             | PL30A                | 6     | LDQ28          | T (LVDS)*    | PL44A                | 6    | LDQ42          | T (LVDS)*    |

| U5             | TDI                  | -     |                |              | TDI                  | -    |                |              |

| U7             | TCK                  | -     |                |              | ТСК                  | -    |                |              |

| V6             | TDO                  | -     |                |              | TDO                  | -    |                |              |

| V5             | TMS                  | -     |                |              | TMS                  | -    |                |              |

| Т8             | VCCJ                 | -     |                |              | VCCJ                 | -    |                |              |

| W4             | PB3A                 | 5     | BDQ6           | Т            | PB3A                 | 5    | BDQ6           | Т            |

| Y3             | PB2A                 | 5     | VREF2_5/BDQ6   | Т            | PB2A                 | 5    | VREF2_5/BDQ6   | Т            |

| W3             | PB3B                 | 5     | BDQ6           | С            | PB3B                 | 5    | BDQ6           | С            |

| Y2             | PB2B                 | 5     | VREF1_5/BDQ6   | С            | PB2B                 | 5    | VREF1_5/BDQ6   | С            |

| AB3            | PB5A                 | 5     | BDQ6           | Т            | PB5A                 | 5    | BDQ6           | Т            |

| VCCIO          | VCCIO5               | 5     |                |              | VCCIO5               | 5    |                |              |

| W5             | PB4A                 | 5     | BDQ6           | Т            | PB4A                 | 5    | BDQ6           | Т            |

| AB2            | PB5B                 | 5     | BDQ6           | С            | PB5B                 | 5    | BDQ6           | С            |

| W6             | PB4B                 | 5     | BDQ6           | С            | PB4B                 | 5    | BDQ6           | С            |

| AB5            | PB7A                 | 5     | BDQ6           | Т            | PB7A                 | 5    | BDQ6           | Т            |

| GNDIO          | GNDIO5               | -     |                |              | GNDIO                | -    |                |              |

| Y4             | PB6A                 | 5     | BDQS6          | Т            | PB6A                 | 5    | BDQS6          | Т            |

| AB4            | PB7B                 | 5     | BDQ6           | С            | PB7B                 | 5    | BDQ6           | С            |

| AA3            | PB6B                 | 5     | BDQ6           | С            | PB6B                 | 5    | BDQ6           | С            |

| AB6            | PB9A                 | 5     | BDQ6           | Т            | PB9A                 | 5    | BDQ6           | Т            |

| VCCIO          | VCCIO5               | 5     |                |              | VCCIO5               | 5    |                |              |

| AA5            | PB8A                 | 5     | BDQ6           | Т            | PB8A                 | 5    | BDQ6           | т            |

| AA6            | PB9B                 | 5     | BDQ6           | C            | PB9B                 | 5    | BDQ6           | C            |

| Y5             | PB8B                 | 5     | BDQ6           | C            | PB8B                 | 5    | BDQ6           | C            |

| GNDIO          | GNDIO5               | -     |                | -            | GNDIO                | _    |                |              |

| -              | -                    | -     |                |              | VCCI05               | 5    |                |              |

| Y6             | PB12A                | 5     | BDQ15          | Т            | PB21A                | 5    | BDQ24          | т            |

| W7             | PB11A                | 5     | BDQ15          | T            | PB20A                | 5    | BDQ24          | T            |

| Y7             | PB12B                | 5     | BDQ15          | C            | PB21B                | 5    | BDQ24          | C            |

| W8             | PB11B                | 5     | BDQ15          | C            | PB20B                | 5    | BDQ24          | C            |

| U8             | PB14A                | 5     | BDQ15<br>BDQ15 | Т            | PB23A                | 5    | BDQ24<br>BDQ24 | Т            |

| VCCIO          | VCCIO5               | 5     |                |              | VCCIO5               | 5    | DUQLY          |              |

| AA7            | PB13A                | 5     | BDQ15          | Т            | PB22A                | 5    | BDQ24          | Т            |

| U9             | PB14B                | 5     | BDQ15<br>BDQ15 | C            | PB23B                | 5    | BDQ24<br>BDQ24 | C            |

| 03             | 10140                | 5     | 00010          | U            | 1 0230               | 5    | 00024          | U            |

# LFE2-70E/SE Logic Signal Connections: 900 fpBGA (Cont.)

|             |                   | LFE2-70E/SE |               |             |

|-------------|-------------------|-------------|---------------|-------------|

| Ball Number | Ball/Pad Function | Bank        | Dual Function | Differentia |

| AD2         | PL90B             | 6           | LDQ88         | C (LVDS)*   |

| AD7         | PL91A             | 6           | LDQ88         | Т           |

| GND         | GNDIO6            | -           |               |             |

| AB9         | PL91B             | 6           | LDQ88         | С           |

| AD5         | TCK               | -           |               |             |

| AE7         | TDI               | -           |               |             |

| AD4         | TMS               | -           |               |             |

| AA9         | TDO               | -           |               |             |

| AD3         | VCCJ              | -           |               |             |

| AC8         | PB2A              | 5           | VREF2_5/BDQ6  | Т           |

| AE8         | PB2B              | 5           | VREF1_5/BDQ6  | С           |

| AD8         | PB3A              | 5           | BDQ6          | Т           |

| AF8         | PB3B              | 5           | BDQ6          | С           |

| AG7         | PB4A              | 5           | BDQ6          | Т           |

| VCCIO       | VCCIO5            | 5           |               |             |

| AH7         | PB4B              | 5           | BDQ6          | С           |

| AC9         | PB5A              | 5           | BDQ6          | Т           |

| AE9         | PB5B              | 5           | BDQ6          | С           |

| AD9         | PB6A              | 5           | BDQS6         | Т           |

| GND         | GNDIO5            | -           |               |             |

| AF9         | PB6B              | 5           | BDQ6          | С           |

| AB10        | PB7A              | 5           | BDQ6          | Т           |

| AA10        | PB7B              | 5           | BDQ6          | С           |

| AJ7         | PB8A              | 5           | BDQ6          | Т           |

| VCCIO       | VCCIO5            | 5           |               |             |

| AK7         | PB8B              | 5           | BDQ6          | С           |

| AC10        | PB9A              | 5           | BDQ6          | Т           |

| AE10        | PB9B              | 5           | BDQ6          | С           |

| AJ8         | PB10A             | 5           | BDQ6          | Т           |

| GND         | GNDIO5            | -           |               |             |

| AK8         | PB10B             | 5           | BDQ6          | С           |

| AF6         | PB11A             | 5           | BDQ15         | Т           |

| AF7         | PB11B             | 5           | BDQ15         | С           |

| AG5         | PB12A             | 5           | BDQ15         | т           |

| AH5         | PB12B             | 5           | BDQ15         | С           |

| AG6         | PB13A             | 5           | BDQ15         | Т           |

| AH6         | PB13B             | 5           | BDQ15         | С           |

| VCCIO       | VCCIO5            | 5           |               | -           |

| AJ4         | PB14A             | 5           | BDQ15         | т           |

| AK4         | PB14B             | 5           | BDQ15         | C           |

| GND         | GNDIO5            | -           |               |             |

| AJ5         | PB15A             | 5           | BDQS15        | T           |

| AK5         | PB15B             | 5           | BDQ15         | C           |

# LFE2M35E/SE and LFE2M50E/SE Logic Signal Connections: 672 fpBGA (Cont.)

|                |                      | L    | FE2M35E/SE                   |              |                      | L    | FE2M50E/SE      |              |

|----------------|----------------------|------|------------------------------|--------------|----------------------|------|-----------------|--------------|

| Ball<br>Number | Ball/Pad<br>Function | Bank | Dual Function                | Differential | Ball/Pad<br>Function | Bank | Dual Function   | Differential |

| P8             | PL45A                | 6    | LDQ48                        | Т            | PL49A                | 6    | LDQ52           | Т            |

| R6             | PL45B                | 6    | LDQ48                        | С            | PL49B                | 6    | LDQ52           | С            |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

| T1             | PL46A                | 6    | LDQ48                        | T (LVDS)*    | PL50A                | 6    | LDQ52           | T*           |

| U1             | PL46B                | 6    | LDQ48                        | C (LVDS)*    | PL50B                | 6    | LDQ52           | C*           |

| R7             | PL47A                | 6    | LDQ48                        | Т            | PL51A                | 6    | LDQ52           | Т            |

| T5             | PL47B                | 6    | LDQ48                        | С            | PL51B                | 6    | LDQ52           | С            |

| GNDIO          | GNDIO6               | -    |                              |              | GNDIO6               | -    |                 |              |

| U3             | PL48A                | 6    | LDQS48                       | T (LVDS)*    | PL52A                | 6    | LDQS52          | T*           |

| U4             | PL48B                | 6    | LDQ48                        | C (LVDS)*    | PL52B                | 6    | LDQ52           | C*           |

| U5             | PL49A                | 6    | LDQ48                        | Т            | PL53A                | 6    | LDQ52           | Т            |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

| U6             | PL49B                | 6    | LDQ48                        | С            | PL53B                | 6    | LDQ52           | С            |

| U2             | PL50A                | 6    | LDQ48                        | T (LVDS)*    | PL54A                | 6    | LDQ52           | T*           |

| V1             | PL50B                | 6    | LDQ48                        | C (LVDS)*    | PL54B                | 6    | LDQ52           | C*           |

| W2             | PL51A                | 6    | LDQ48                        | Т            | PL55A                | 6    | LDQ52           | Т            |

| GNDIO          | GNDIO6               | -    |                              |              | GNDIO6               | -    |                 |              |

| V2             | PL51B                | 6    | LDQ48                        | С            | PL55B                | 6    | LDQ52           | С            |

| V4             | PL55A                | 6    | LDQ57                        | T (LVDS)*    | PL59A                | 6    |                 | T*           |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

| V3             | PL55B                | 6    | LDQ57                        | C (LVDS)*    | PL59B                | 6    |                 | C*           |

| -              | -                    | -    |                              | . ,          | GNDIO6               | -    |                 |              |

| W4             | PL57A                | 6    | LLM0_GPLLT_IN_A**/LDQS57**** | T (LVDS)*    | PL62A                | 6    | LLM0_GPLLT_IN_A | T*           |

| GNDIO          | GNDIO6               | -    |                              | . ,          | GNDIO6               | -    |                 |              |

| W3             | PL57B                | 6    | LLM0_GPLLC_IN_A**/LDQ57      | C (LVDS)*    | PL62B                | 6    | LLM0_GPLLC_IN_A | C*           |

| W1             | PL58A                | 6    | LLM0_GPLLT_FB_A/LDQ57        | T            | PL63A                | 6    | LLM0_GPLLT_FB_A | Т            |

| Y1             | PL58B                | 6    | LLM0_GPLLC_FB_A/LDQ57        | С            | PL63B                | 6    | LLM0_GPLLC_FB_A | С            |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

| AA1            | PL59A                | 6    | LLM0_GDLLT_IN_A**/LDQ57      | T (LVDS)*    | PL64A                | 6    | LLM0_GDLLT_IN_A | T*           |

| AB1            | PL59B                | 6    | LLM0_GDLLC_IN_A**/LDQ57      | C (LVDS)*    | PL64B                | 6    | LLM0_GDLLC_IN_A | C*           |

| U7             | PL60A                | 6    | LLM0_GDLLT_FB_A/LDQ57        | T            | PL65A                | 6    | LLM0_GDLLT_FB_A | Т            |

| V6             | PL60B                | 6    | LLM0_GDLLC_FB_A/LDQ57        | С            | PL65B                | 6    | LLM0_GDLLC_FB_A | С            |

| GNDIO          | GNDIO6               | -    |                              |              | GNDIO6               | -    |                 |              |

| Т8             | LLM0_PLLCAP          | 6    |                              |              | LLM0_PLLCAP          | 6    |                 |              |

| W5             | PL62A                | 6    | LDQ66                        | T (LVDS)*    | PL67A                | 6    | LDQ71           | T*           |

| Y4             | PL62B                | 6    | LDQ66                        | C (LVDS)*    | PL67B                | 6    | LDQ71           | C*           |

| U8             | PL63A                | 6    | LDQ66                        | Т            | PL68A                | 6    | LDQ71           | Т            |

| W6             | PL63B                | 6    | LDQ66                        | С            | PL68B                | 6    | LDQ71           | С            |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

| Y3             | PL64A                | 6    | LDQ66                        | T (LVDS)*    | PL69A                | 6    | LDQ71           | T*           |

| AA3            | PL64B                | 6    | LDQ66                        | C (LVDS)*    | PL69B                | 6    | LDQ71           | C*           |

| V7             | NC                   | -    |                              |              | PL70A                | 6    | LDQ71           | Т            |

| Y5             | PL65B                | 6    | LDQ66                        | С            | PL70B                | 6    | LDQ71           | С            |

| GNDIO          | GNDIO6               | -    |                              |              | GNDIO6               | -    |                 |              |

| AB2            | PL66A                | 6    | LDQS66                       | T (LVDS)*    | PL71A                | 6    | LDQS71          | T*           |

| AA4            | PL66B                | 6    | LDQ66                        | C (LVDS)*    | PL71B                | 6    | LDQ71           | C*           |

| Y6             | PL67A                | 6    | LDQ66                        | T            | PL72A                | 6    | LDQ71           | T            |

| VCCIO          | VCCIO6               | 6    |                              |              | VCCIO6               | 6    |                 |              |

# LFE2M50E/SE and LFE2M70E/SE Logic Signal Connections: 900 fpBGA (Cont.)

|                |                          | LFE2M | 50E/SE            |              |                          |      | LFE2M70E/SE             |              |

|----------------|--------------------------|-------|-------------------|--------------|--------------------------|------|-------------------------|--------------|

| Ball<br>Number | Ball/Pad<br>Function     | Bank  | Dual Function     | Differential | Ball/Pad<br>Function     | Bank | Dual Function           | Differential |

| AH25           | LRC_SQ_VCCOB1            | 13    |                   |              | LRC_SQ_VCCOB1            | 13   |                         |              |

| AJ25           | LRC_SQ_HDOUTN1           | 13    |                   | С            | LRC_SQ_HDOUTN1           | 13   |                         | С            |

| AH26           | LRC_SQ_VCCTX1            | 13    |                   |              | LRC_SQ_VCCTX1            | 13   |                         |              |

| AJ26           | LRC_SQ_HDOUTN0           | 13    |                   | С            | LRC_SQ_HDOUTN0           | 13   |                         | С            |

| AK27           | LRC_SQ_VCCOB0            | 13    |                   |              | LRC_SQ_VCCOB0            | 13   |                         |              |

| AK26           | LRC_SQ_HDOUTP0           | 13    |                   | Т            | LRC_SQ_HDOUTP0           | 13   |                         | Т            |

| AH27           | LRC_SQ_VCCTX0            | 13    |                   |              | LRC_SQ_VCCTX0            | 13   |                         |              |

| AJ29           | LRC_SQ_HDINN0            | 13    |                   | С            | LRC_SQ_HDINN0            | 13   |                         | С            |

| AJ30           | LRC_SQ_VCCIB0            | 13    |                   |              | LRC_SQ_VCCIB0            | 13   |                         |              |

| AK29           | LRC_SQ_HDINP0            | 13    |                   | Т            | LRC_SQ_HDINP0            | 13   |                         | Т            |

| AH30           | LRC_SQ_VCCRX0            | 13    |                   |              | LRC_SQ_VCCRX0            | 13   |                         |              |

| AG27           | CFG2                     | 8     |                   |              | CFG2                     | 8    |                         |              |

| AD25           | CFG1                     | 8     |                   |              | CFG1                     | 8    |                         |              |

| AG28           | CFG0                     | 8     |                   |              | CFG0                     | 8    |                         |              |

| AG30           | PROGRAMN                 | 8     |                   |              | PROGRAMN                 | 8    |                         |              |

| AG29           | CCLK                     | 8     |                   |              | CCLK                     | 8    |                         |              |

| AC24           | INITN                    | 8     |                   |              | INITN                    | 8    |                         |              |

| AF27           | DONE                     | 8     |                   |              | DONE                     | 8    |                         |              |

| GNDIO          | GNDIO8                   | -     |                   |              | GNDIO8                   | -    |                         |              |

| AF28           | WRITEN***                | 8     |                   |              | WRITEN***                | 8    |                         |              |

| AE26           | CS1N***                  | 8     |                   |              | CS1N***                  | 8    |                         |              |

| AB23           | CSN***                   | 8     |                   |              | CSN***                   | 8    |                         |              |

| AF29           | D0/SPIFASTN***           | 8     |                   |              | D0/SPIFASTN***           | 8    |                         |              |

| VCCIO          | VCCI08                   | 8     |                   |              | VCCIO8                   | 8    |                         |              |

| AF30           | D1***                    | 8     |                   |              | D1***                    | 8    |                         |              |

| AD26           | D2***                    | 8     |                   |              | D2***                    | 8    |                         |              |

| AE29           | D3***                    | 8     |                   |              | D3***                    | 8    |                         |              |

| GNDIO          | GNDIO8                   | -     |                   |              | GNDIO8                   | -    |                         |              |

| AE30           | D4***                    | 8     |                   |              | D4***                    | 8    |                         |              |

| AD29           | D5***                    | 8     |                   |              | D5***                    | 8    |                         |              |

| AC25           | D6***                    | 8     |                   |              | D6***                    | 8    |                         |              |

| AD30           | D7/SPID0***              | 8     |                   |              | D7/SPID0***              | 8    |                         |              |

| VCCIO          | VCCIO8                   | 8     |                   |              | VCCIO8                   | 8    |                         |              |

| AA22           | DI/CSSPI0N***            | 8     |                   |              | DI/CSSPI0N***            | 8    |                         |              |

| AC26           | DOUT/CSON/<br>CSSPI1N*** | 8     |                   |              | DOUT/CSON/<br>CSSPI1N*** | 8    |                         |              |

| AA23           | BUSY/SISPI***            | 8     |                   |              | BUSY/SISPI***            | 8    |                         |              |

| AB22           | RLM0_PLLCAP              | 3     |                   |              | RLM0_PLLCAP              | 3    |                         |              |

| AC27           | PR65B                    | 3     | RLM0_GDLLC_FB_A   | С            | PR85B                    | 3    | RLM0_GDLLC_FB_A/RDQ82   | С            |

| GNDIO          | GNDIO3                   | -     |                   |              | GNDIO3                   | -    |                         |              |

| AC28           | PR65A                    | 3     | RLM0_GDLLT_FB_A   | Т            | PR85A                    | 3    | RLM0_GDLLT_FB_A/RDQ82   | Т            |

| AC29           | PR64B                    | 3     | RLM0_GDLLC_IN_A** | C (LVDS)*    | PR84B                    | 3    | RLM0_GDLLC_IN_A**/RDQ82 | C (LVDS)*    |

| AC30           | PR64A                    | 3     | RLM0_GDLLT_IN_A** | T (LVDS)*    | PR84A                    | 3    | RLM0_GDLLT_IN_A**/RDQ82 | T (LVDS)*    |

| AB30           | PR63B                    | 3     | RLM0_GPLLC_IN_A** | С            | PR83B                    | 3    | RLM0_GPLLC_IN_A**/RDQ82 | С            |

| VCCIO          | VCCIO3                   | 3     |                   |              | VCCIO3                   | 3    |                         |              |

| AA30           | PR63A                    | 3     | RLM0_GPLLT_IN_A** | Т            | PR83A                    | 3    | RLM0_GPLLT_IN_A**/RDQ82 | Т            |

| AB29           | PR62B                    | 3     | RLM0_GPLLC_FB_A   | C (LVDS)*    | PR82B                    | 3    | RLM0_GPLLC_FB_A/RDQ82   | C (LVDS)*    |

| AB28           | PR62A                    | 3     | RLM0_GPLLT_FB_A   | T (LVDS)*    | PR82A                    | 3    | RLM0_GPLLT_FB_A/RDQS82  | T (LVDS)*    |

| GNDIO          | GNDIO3                   | -     |                   |              | GNDIO3                   | -    |                         |              |

# LFE2M50E/SE and LFE2M70E/SE Logic Signal Connections: 900 fpBGA (Cont.)

|                |                      | LFE2M50 | E/SE          |              | LFE2M70E/SE          |      |               |             |  |

|----------------|----------------------|---------|---------------|--------------|----------------------|------|---------------|-------------|--|

| Ball<br>Number | Ball/Pad<br>Function | Bank    | Dual Function | Differential | Ball/Pad<br>Function | Bank | Dual Function | Differentia |  |

| G7             | PL8A                 | 7       | LDQ6          | T (LVDS)*    | NC                   | -    |               |             |  |

| G8             | PL6A                 | 7       | LDQS6****     | T (LVDS)*    | NC                   | -    |               |             |  |

| G9             | PL5A                 | 7       | LDQ6          | Т            | NC                   | -    |               |             |  |

| H19            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| H20            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| H21            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| H22            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| H6             | PL8B                 | 7       | LDQ6          | C (LVDS)*    | NC                   | -    |               |             |  |

| H8             | PL5B                 | 7       | LDQ6          | С            | NC                   | -    |               |             |  |

| H9             | PL2A                 | 7       | LDQ6          | T (LVDS)*    | NC                   | -    |               |             |  |

| J10            | PL2B                 | 7       | LDQ6          | C (LVDS)*    | NC                   | -    |               |             |  |

| J20            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| J21            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| J9             | PL4A                 | 7       | LDQ6          | T (LVDS)*    | NC                   | -    |               |             |  |

| K9             | PL4B                 | 7       | LDQ6          | C (LVDS)*    | NC                   | -    |               |             |  |

| R9             | NC                   | -       |               |              | NC                   | -    |               |             |  |

| U22            | NC                   | -       |               |              | NC                   | -    |               |             |  |

| W9             | NC                   | -       |               |              | NC                   | -    |               |             |  |

| N13            | VCCPLL               | -       |               |              | VCCPLL               | -    |               |             |  |

| N18            | VCCPLL               | -       |               |              | VCCPLL               | -    |               |             |  |

| V13            | VCCPLL               | -       |               |              | VCCPLL               | -    |               |             |  |

| V18            | VCCPLL               | -       |               |              | VCCPLL               | -    |               |             |  |

\* Supports true LVDS. Other differential signals must be emulated with external resistors.

\*\* These dedicated input pins can be used for GPLLs or GDLLs within the respective quadrant.

\*\*\* These sysCONFIG pins are dedicated I/O pins for configuration. The outpus are actively driven during normal device operation.

\*\*\*\*Due to packaging bond out option, this DQS does not have all the necessary DQ pins bonded out for a full 8-bit data width.

Note: VCCIO and GND pads are used to determine the average DC current drawn by I/Os between GND/VCCIO connections, or between the last GND/VCCIO in an I/O bank and the end of an I/O bank. The substrate pads listed in the Pin Table do not necessarily have a one to one connection with a package ball or pin.

# LFE2M70E/SE and LFE2M100E/SE Logic Signal Connections: 1152 fpBGA (Cont.)

|                |                      | LFE2M70E/ | SE             |              |                      | LFE2M100 | E/SE           |              |

|----------------|----------------------|-----------|----------------|--------------|----------------------|----------|----------------|--------------|

| Ball<br>Number | Ball/Pad<br>Function | Bank      | Dual Function  | Differential | Ball/Pad<br>Function | Bank     | Dual Function  | Differential |

| GNDIO          | GNDIO5               | -         |                |              | GNDIO5               | -        |                |              |

| AE16           | PB42B                | 5         | BDQ42          | С            | PB51B                | 5        | BDQ51          | С            |

| AF15           | PB44A                | 5         | BDQ42          | Т            | PB53A                | 5        | BDQ51          | Т            |

| VCCIO          | VCCIO5               | 5         |                |              | VCCIO5               | 5        |                |              |

| AD16           | PB44B                | 5         | BDQ42          | С            | PB53B                | 5        | BDQ51          | С            |

| AK17           | PB45A                | 5         | BDQ42          | Т            | PB54A                | 5        | BDQ51          | Т            |

| AH16           | PB45B                | 5         | BDQ42          | С            | PB54B                | 5        | BDQ51          | С            |

| AN16           | PB46A                | 5         | BDQ42          | Т            | PB55A                | 5        | BDQ51          | Т            |

| GNDIO          | GNDIO5               | -         |                |              | GNDIO5               | -        |                |              |

| AP16           | PB46B                | 5         | BDQ42          | С            | PB55B                | 5        | BDQ51          | С            |

| AL17           | PB47A                | 5         | BDQ51          | Т            | PB56A                | 5        | BDQ60          | Т            |

| AM17           | PB47B                | 5         | BDQ51          | С            | PB56B                | 5        | BDQ60          | С            |

| AN17           | PB48A                | 5         | BDQ51          | Т            | PB57A                | 5        | BDQ60          | Т            |

| AP17           | PB48B                | 5         | BDQ51          | С            | PB57B                | 5        | BDQ60          | С            |

| AD17           | PB49A                | 5         | BDQ51          | Т            | PB58A                | 5        | BDQ60          | Т            |

| AE17           | PB49B                | 5         | BDQ51          | С            | PB58B                | 5        | BDQ60          | С            |

| VCCIO          | VCCIO5               | 5         |                |              | VCCIO5               | 5        |                |              |

| AL18           | PB50A                | 5         | BDQ51          | Т            | PB59A                | 5        | BDQ60          | Т            |

| AM18           | PB50B                | 5         | BDQ51          | С            | PB59B                | 5        | BDQ60          | С            |

| GNDIO          | GNDIO5               | -         |                |              | GNDIO5               | -        |                |              |

| AP18           | PB51A                | 5         | BDQS51         | Т            | PB60A                | 5        | BDQS60         | Т            |

| AN18           | PB51B                | 5         | BDQ51          | С            | PB60B                | 5        | BDQ60          | С            |

| AG17           | PB52A                | 5         | VREF2_5/BDQ51  | Т            | PB61A                | 5        | VREF2_5/BDQ60  | Т            |

| AJ17           | PB52B                | 5         | VREF1_5/BDQ51  | С            | PB61B                | 5        | VREF1_5/BDQ60  | С            |

| AF17           | PB53A                | 5         | PCLKT5_0/BDQ51 | Т            | PB62A                | 5        | PCLKT5_0/BDQ60 | т            |

| AH17           | PB53B                | 5         | PCLKC5_0/BDQ51 | С            | PB62B                | 5        | PCLKC5_0/BDQ60 | С            |

| VCCIO          | VCCIO5               | 5         |                |              | VCCIO5               | 5        |                |              |

| GNDIO          | GNDIO5               | -         |                |              | GNDIO5               | -        |                |              |

| AF18           | PB58A                | 4         | PCLKT4_0/BDQ60 | Т            | PB67A                | 4        | PCLKT4_0/BDQ69 | Т            |

| VCCIO          | VCCIO4               | 4         |                |              | VCCIO4               | 4        |                |              |

| AD18           | PB58B                | 4         | PCLKC4_0/BDQ60 | С            | PB67B                | 4        | PCLKC4_0/BDQ69 | С            |

| AP19           | PB59A                | 4         | VREF2_4/BDQ60  | Т            | PB68A                | 4        | VREF2_4/BDQ69  | Т            |

| AN19           | PB59B                | 4         | VREF1_4/BDQ60  | С            | PB68B                | 4        | VREF1_4/BDQ69  | С            |

| AP20           | PB60A                | 4         | BDQS60         | Т            | PB69A                | 4        | BDQS69         | Т            |

| GNDIO          | GNDIO4               | -         |                |              | GNDIO4               | -        |                |              |

| AM20           | PB60B                | 4         | BDQ60          | С            | PB69B                | 4        | BDQ69          | С            |

| AN20           | PB61A                | 4         | BDQ60          | Т            | PB70A                | 4        | BDQ69          | Т            |

| AM21           | PB61B                | 4         | BDQ60          | С            | PB70B                | 4        | BDQ69          | С            |

| AG18           | PB62A                | 4         | BDQ60          | Т            | PB71A                | 4        | BDQ69          | Т            |

| VCCIO          | VCCIO4               | 4         |                |              | VCCIO4               | 4        |                |              |

| AE18           | PB62B                | 4         | BDQ60          | С            | PB71B                | 4        | BDQ69          | С            |

| AJ18           | PB63A                | 4         | BDQ60          | Т            | PB72A                | 4        | BDQ69          | Т            |

| AH18           | PB63B                | 4         | BDQ60          | С            | PB72B                | 4        | BDQ69          | С            |

| AK18           | PB64A                | 4         | BDQ60          | Т            | PB73A                | 4        | BDQ69          | Т            |

| GNDIO          | GNDIO4               | -         |                |              | GNDIO4               | -        |                |              |

| AK19           | PB64B                | 4         | BDQ60          | С            | PB73B                | 4        | BDQ69          | С            |

| AP21           | PB65A                | 4         | BDQ69          | Т            | PB74A                | 4        | BDQ78          | Т            |

| AN21           | PB65B                | 4         | BDQ69          | С            | PB74B                | 4        | BDQ78          | С            |

| AL20           | PB66A                | 4         | BDQ69          | Т            | PB75A                | 4        | BDQ78          | т            |

| Part Number       | I/Os | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|-------------------|------|---------|-------|-----------------|------|-------|----------|

| LFE2-20SE-5QN208I | 131  | 1.2V    | -5    | Lead-Free PQFP  | 208  | Ind   | 20       |

| LFE2-20SE-6QN208I | 131  | 1.2V    | -6    | Lead-Free PQFP  | 208  | Ind   | 20       |

| LFE2-20SE-5FN256I | 193  | 1.2V    | -5    | Lead-Free fpBGA | 256  | Ind   | 20       |

| LFE2-20SE-6FN256I | 193  | 1.2V    | -6    | Lead-Free fpBGA | 256  | Ind   | 20       |

| LFE2-20SE-5FN484I | 331  | 1.2V    | -5    | Lead-Free fpBGA | 484  | Ind   | 20       |

| LFE2-20SE-6FN484I | 331  | 1.2V    | -6    | Lead-Free fpBGA | 484  | Ind   | 20       |

| LFE2-20SE-5FN672I | 402  | 1.2V    | -5    | Lead-Free fpBGA | 672  | Ind   | 20       |

| LFE2-20SE-6FN672I | 402  | 1.2V    | -6    | Lead-Free fpBGA | 672  | Ind   | 20       |

| Part Number       | I/Os | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|-------------------|------|---------|-------|-----------------|------|-------|----------|

| LFE2-35SE-5FN484I | 331  | 1.2V    | -5    | Lead-Free fpBGA | 484  | Ind   | 35       |

| LFE2-35SE-6FN484I | 331  | 1.2V    | -6    | Lead-Free fpBGA | 484  | Ind   | 35       |

| LFE2-35SE-5FN672I | 450  | 1.2V    | -5    | Lead-Free fpBGA | 672  | Ind   | 35       |

| LFE2-35SE-6FN672I | 450  | 1.2V    | -6    | Lead-Free fpBGA | 672  | Ind   | 35       |

| Part Number       | I/Os | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|-------------------|------|---------|-------|-----------------|------|-------|----------|

| LFE2-50SE-5FN484I | 339  | 1.2V    | -5    | Lead-Free fpBGA | 484  | Ind   | 50       |

| LFE2-50SE-6FN484I | 339  | 1.2V    | -6    | Lead-Free fpBGA | 484  | Ind   | 50       |

| LFE2-50SE-5FN672I | 500  | 1.2V    | -5    | Lead-Free fpBGA | 672  | Ind   | 50       |

| LFE2-50SE-6FN672I | 500  | 1.2V    | -6    | Lead-Free fpBGA | 672  | Ind   | 50       |

| Part Number       | I/Os | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|-------------------|------|---------|-------|-----------------|------|-------|----------|

| LFE2-70SE-5FN672I | 500  | 1.2V    | -5    | Lead-Free fpBGA | 672  | Ind   | 70       |

| LFE2-70SE-6FN672I | 500  | 1.2V    | -6    | Lead-Free fpBGA | 672  | Ind   | 70       |

| LFE2-70SE-5FN900I | 583  | 1.2V    | -5    | Lead-Free fpBGA | 900  | Ind   | 70       |

| LFE2-70SE-6FN900I | 583  | 1.2V    | -6    | Lead-Free fpBGA | 900  | Ind   | 70       |

| Part Number         | I/Os | Voltage | Grade | Package         | Pins | Temp. | LUTs (K) |

|---------------------|------|---------|-------|-----------------|------|-------|----------|

| LFE2M100SE-5FN1152C | 520  | 1.2V    | -5    | Lead-Free fpBGA | 1152 | Com   | 100      |

| LFE2M100SE-6FN1152C | 520  | 1.2V    | -6    | Lead-Free fpBGA | 1152 | Com   | 100      |

| LFE2M100SE-7FN1152C | 520  | 1.2V    | -7    | Lead-Free fpBGA | 1152 | Com   | 100      |

| LFE2M100SE-5FN900C  | 416  | 1.2V    | -5    | Lead-Free fpBGA | 900  | Com   | 100      |

| LFE2M100SE-6FN900C  | 416  | 1.2V    | -6    | Lead-Free fpBGA | 900  | Com   | 100      |

| LFE2M100SE-7FN900C  | 416  | 1.2V    | -7    | Lead-Free fpBGA | 900  | Com   | 100      |

# LatticeECP2/M Family Data Sheet Supplemental Information

July 2012

Data Sheet DS1006

## **For Further Information**

A variety of technical notes for the LatticeECP2/M family are available on the Lattice web site at <u>www.latticesemi.com</u>.

- TN1102, LatticeECP2/M sysIO Usage Guide

- TN1103, LatticeECP2/M sysCLOCK PLL Design and Usage Guide

- TN1104, LatticeECP2/M Memory Usage Guide

- TN1105, LatticeECP2/M High-Speed I/O Interface

- TN1106, Power Estimation and Management for LatticeECP2/M Devices

- TN1107, LatticeECP2/M sysDSP Usage Guide

- TN1108, LatticeECP2/M sysCONFIG Usage Guide

- TN1109, LatticeECP2/M Configuration Encryption Usage Guide

- TN1113, LatticeECP2/M Soft Error Detection (SED) Usage Guide

- TN1124, LatticeECP2M SERDES/PCS Usage Guide

- TN1162, LatticeECP2/M Hardware Checklist

For further information about interface standards refer to the following web sites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: <u>www.pcisig.com</u>

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.