Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627-04e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7                       | Bit 6           | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1      | Bit 0     | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|-----------------------------|-----------------|-----------------|----------------|---------------|----------------|------------|-----------|-----------------------------------------|--------------------|

| Bank 0  |         |                             |                 |                 |                |               |                |            |           |                                         |                    |

| 00h     | INDF    | Addressir                   | ng this locatio | l register)     | xxxx xxxx      | 25            |                |            |           |                                         |                    |

| 01h     | TMR0    | Timer0 M                    | odule's Regis   | ter             |                |               |                |            | • /       | xxxx xxxx                               | 43                 |

| 02h     | PCL     | Program                     | Counter's (PC   | ) Least Sign    | ificant Byte   |               |                |            |           | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP                         | RP1             | RP0             | TO             | PD            | Z              | DC         | С         | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d                  | ata memory a    | ddress point    | er             |               |                |            | -         | xxxx xxxx                               | 25                 |

| 05h     | PORTA   | RA7                         | RA6             | RA5             | RA4            | RA3           | RA2            | RA1        | RA0       | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7                         | RB6             | RB5             | RB4            | RB3           | RB2            | RB1        | RB0       | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | _                                       |                    |

| 08h     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | _                                       |                    |

| 09h     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | _                                       |                    |

| 0Ah     | PCLATH  | _                           | _               | _               | Write buffer   | for upper 5 b | oits of progra | im counter |           | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE                         | PEIE            | T0IE            | INTE           | RBIE          | T0IF           | INTF       | RBIF      | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF                        | CMIF            | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF     | TMR1IF    | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | —                                       | _                  |

| 0Eh     | TMR1L   | Holding r                   | egister for the | Least Signif    | icant Byte of  | the 16-bit TN | 1R1            |            |           | XXXX XXXX                               | 46                 |

| 0Fh     | TMR1H   | Holding r                   | egister for the | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |            |           | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _                           | _               | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS     | TMR10N    | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo                     | odule's registe | r               |                |               |                |            |           | 0000 0000                               | 50                 |

| 12h     | T2CON   | _                           | TOUTPS3         | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1    | T2CKPS0   | -000 0000                               | 50                 |

| 13h     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | _                                       | _                  |

| 14h     | —       | Unimplen                    | nented          |                 |                |               |                |            |           | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0                   | Compare/PWN     | /I register (LS | SB)            |               |                |            |           | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0                   | Compare/PWN     | /I register (M  | SB)            |               |                |            |           | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _                           | —               | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1     | CCP1M0    | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN                        | RX9             | SREN            | CREN           | ADEN          | FERR           | OERR       | RX9D      | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T                     | ransmit data    | register        |                |               |                |            |           | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART Receive data register |                 |                 |                |               |                |            | 0000 0000 | 77                                      |                    |

| 1Bh     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | —                                       | _                  |

| 1Ch     | _       | Unimplen                    | nented          |                 |                |               |                |            |           | —                                       | _                  |

| 1Dh     | —       | Unimplen                    | nented          |                 |                |               |                |            |           | —                                       | —                  |

| 1Eh     | —       | Unimplen                    | nented          |                 | 1              | 1             |                |            | 1         | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT                       | C10UT           | C2INV           | C1INV          | CIS           | CM2            | CM1        | CM0       | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

# 4.0 GENERAL DESCRIPTION

The PIC16F62X are 18-Pin FLASH-based members of the versatile PIC16CXX family of low cost, high performance, CMOS, fully static, 8-bit microcontrollers.

All PICmicro<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F62X have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16F62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F62X has eight oscillator configurations. The single pin ER oscillator provides a low cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, INTRC is a self-contained internal oscillator. The HS is for High Speed crystals. The EC mode is for an external clock source. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external interrupts, internal interrupts, and RESETS.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

Table 4-1 shows the features of the PIC16F62X midrange microcontroller families.

A simplified block diagram of the PIC16F62X is shown in Figure 2.1.

The PIC16F62X series fits in applications ranging from battery chargers to low power remote sensors. The FLASH technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F62X very versatile.

# 4.1 Development Support

The PIC16F62X family is supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627                        | PIC16F628                        | PIC16LF627                       | PIC16LF628                       |

|-------------|--------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

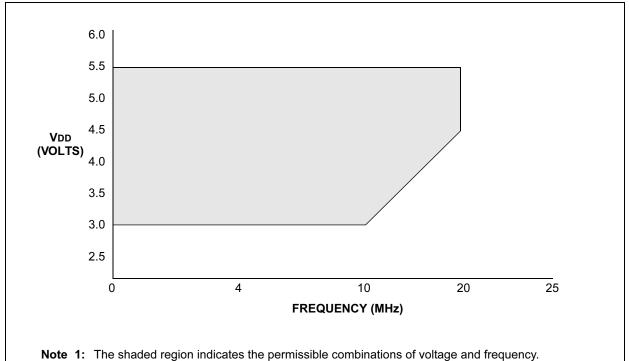

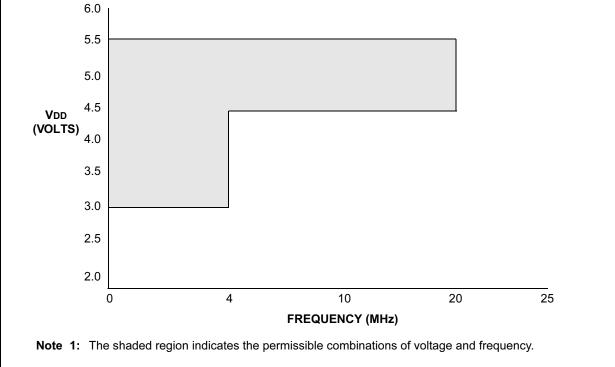

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 4                                | 4                                |

|             | FLASH Program Memory (words)         | 1024                             | 2048                             | 1024                             | 2048                             |

| Memory      | RAM Data Memory (bytes)              | 224                              | 224                              | 224                              | 224                              |

|             | EEPROM Data Memory (bytes)           | 128                              | 128                              | 128                              | 128                              |

|             | Timer Module(s)                      | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 |

|             | Comparator(s)                        | 2                                | 2                                | 2                                | 2                                |

| Peripherals | Capture/Compare/PWM modules          | 1                                | 1                                | 1                                | 1                                |

|             | Serial Communications                | USART                            | USART                            | USART                            | USART                            |

|             | Internal Voltage Reference           | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Interrupt Sources                    | 10                               | 10                               | 10                               | 10                               |

|             | I/O Pins                             | 16                               | 16                               | 16                               | 16                               |

| Features    | Voltage Range (Volts)                | 3.0-5.5                          | 3.0-5.5                          | 2.0-5.5                          | 2.0-5.5                          |

|             | Brown-out Detect                     | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Packages                             | 18-pin DIP, SOIC,<br>20-pin SSOP |

# TABLE 4-1:PIC16F62X FAMILY OF DEVICES

All PICmicro® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F62X Family devices use serial programming with clock pin RB6 and data pin RB7.

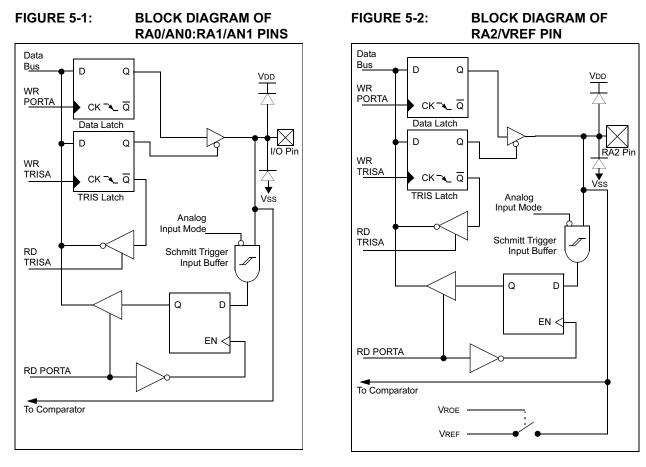

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3 PIN

| Name                                    | Function | Input Type     | Output<br>Type                 | Description                                                                                                                                                                       |

|-----------------------------------------|----------|----------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                                 | RB0      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | INT      | ST             | _                              | External interrupt.                                                                                                                                                               |

| RB1/RX/DT                               | RB1      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | RX       | ST             | _                              | USART Receive Pin                                                                                                                                                                 |

|                                         | DT       | ST             | CMOS                           | Synchronous data I/O                                                                                                                                                              |

| RB2/TX/CK                               | RB2      | TTL            | CMOS                           | Bi-directional I/O port                                                                                                                                                           |

|                                         | ТХ       | _              | CMOS                           | USART Transmit Pin                                                                                                                                                                |

|                                         | СК       | ST             | CMOS                           | Synchronous Clock I/O. Can be software programmed for internal weak pull-up.                                                                                                      |

| RB3/CCP1                                | RB3      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed fo internal weak pull-up.                                                                                                     |

|                                         | CCP1     | ST             | CMOS                           | Capture/Compare/PWM/I/O                                                                                                                                                           |

| RB4/PGM                                 | RB4      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed fo internal weak pull-up.                                                                                                     |

|                                         | PGM      | ST             | _                              | Low voltage programming input pin. Interrupt-on-pin<br>change. When low voltage programming is enabled, the<br>interrupt-on-pin change and weak pull-up resistor are<br>disabled. |

| RB5                                     | RB5      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

| RB6/T1OSO/T1CKI/<br>PGC                 | RB6      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T10SO    | _              | XTAL                           | Timer1 Oscillator Output                                                                                                                                                          |

|                                         | T1CKI    | ST             | —                              | Timer1 Clock Input                                                                                                                                                                |

|                                         | PGC      | ST             | _                              | ICSP Programming Clock                                                                                                                                                            |

| RB7/T1OSI/PGD                           | RB7      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T1OSI    | XTAL           | _                              | Timer1 Oscillator Input                                                                                                                                                           |

|                                         | PGD      | ST             | CMOS                           | ICSP Data I/O                                                                                                                                                                     |

| Legend: O = Out<br>— = Not<br>TTL = TTL | used     | CM(<br>I<br>OD | OS = CMOS<br>= Input<br>= Open | S Output P = Power<br>ST = Schmitt Trigger Input<br>Drain Output AN = Analog                                                                                                      |

PORTR FUNCTIONS

SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup> TABLE 5-4:

| Address   | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h, 106h | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h, 186h | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h, 181h | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTB.

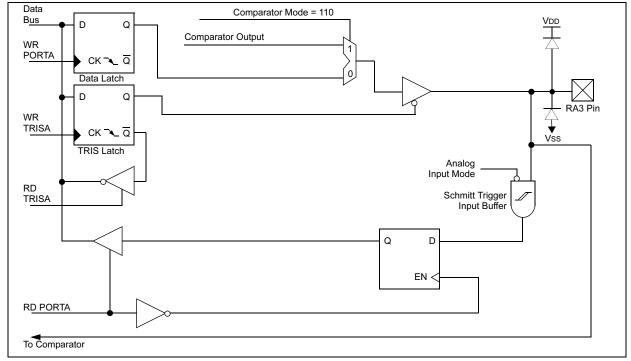

### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

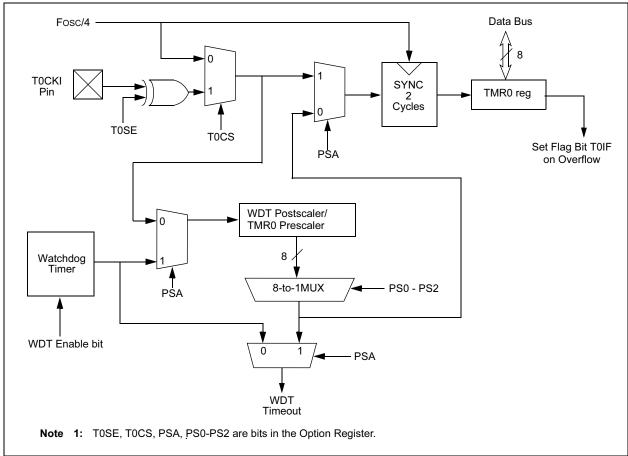

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

# 7.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq    | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

**Note 1:** These values are for design guidance only. Consult AN826 (DS00826A) for further information on Crystal/Capacitor Selection.

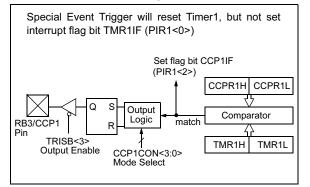

# 7.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The spe | cial e | event | trigg | ers from tl | he CC | CP1 |

|-------|---------|--------|-------|-------|-------------|-------|-----|

|       | module  | will   | not   | set   | interrupt   | flag  | bit |

|       | TMR1IF  | (PIR   | 1<0>  | ).    |             |       |     |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

# 7.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other RESET except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

# 7.7 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7      | Bit 6       | Bit 5         | Bit 4          | Bit 3           | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|------------|-------------|---------------|----------------|-----------------|-------------|--------|--------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE        | PEIE        | TOIE          | INTE           | RBIE            | T0IF        | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF       | CMIF        | RCIF          | TXIF           | I               | CCP1IF      | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE       | CMIE        | RCIE          | TXIE           | I               | CCP1IE      | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 0Eh                   | TMR1L  | Holding re | egister for | the Least Sig | gnificant Byte | of the 16-bit   | TMR1 regist | er     |        | xxxx xxxx       | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding re | gister for  | the Most Sig  | nificant Byte  | of the 16-bit T | MR1 registe | er     |        | xxxx xxxx       | uuuu uuuu                       |

| 10h                   | T1CON  | _          | _           | T1CKPS1       | T1CKPS0        | T1OSCEN         | T1SYNC      | TMR1CS | TMR10N | 00 0000         | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

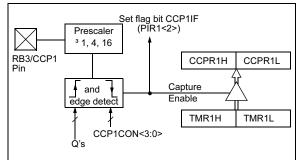

# 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the Interrupt Request Flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 11.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# TABLE 11-2:CAPTURE MODE OPERATION<br/>BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 11-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

### 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 11-1: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 11.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an output by clearing the TRISB<3> bit.

Note: Clearing the CCP1CON register will force the RB3/CCP1 compare output latch to the default low level. This is not the data latch.

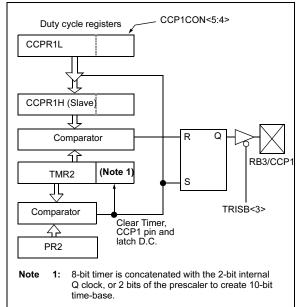

# 11.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTB I/O data |

|       | latch.                                    |

Figure 11-2 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 11.3.3.

#### FIGURE 11-2: SIMPLIFIED PWM BLOCK DIAGRAM

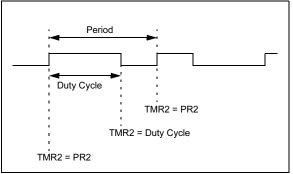

A PWM output (Figure 11-3) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 11-3: PWM OUTPUT

### 11.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • Tosc • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 8.0) is not used in the determination of the PWM frequency. The postscaler could be used to have an interrupt occur at a different frequency than the PWM output.

| BAUD     | Fosc = 20 M | Hz     | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz | SPBRG  |                    |

|----------|-------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615       | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230      | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878      | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818      | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636     | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250         | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625         | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250        | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 MHz<br>KBAUD ERROR |        | SPBRG              | 5.068 MHz |         | SPBRG              | 4 MHz    | SPBRG   |                    |

|----------|--------------------------------|--------|--------------------|-----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) |                                |        | value<br>(decimal) | KBAUD     | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520                          | -0.83% | 46                 | 9598.485  | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454                         | +1.32% | 22                 | 18632.35  | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286                         | -2.90% | 11                 | 39593.75  | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930                         | -2.90% | 7                  | 52791.67  | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860                        | -2.90% | 3                  | 105583.3  | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA                             | _      | _                  | 316750    | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA                             | _      | _                  | NA        | _       | _                  | NA       | _       | _                  |

| 1250000  | NA                             |        | —                  | NA        | —       | _                  | NA       | —       |                    |

| BAUD        | Fosc = 3.579 | 9 MHz    | SPBRG              | 1 MHz   |          | SPBRG              | 32.768 MHz |       | SPBRG              |

|-------------|--------------|----------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600        | 9725.543     | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200       | 18640.63     | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400       | 37281.25     | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600       | 55921.88     | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200      | 111243.8     | -2.913%  | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000      | 223687.5     | -10.525% | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000      | NA           | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000     | NA           | —        | —                  | NA      | —        | —                  | NA         | NA    | NA                 |

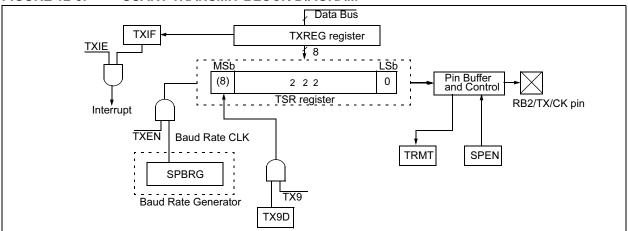

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

#### 13.3 READING THE EEPROM DATA MEMORY

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

## EXAMPLE 13-1: DATA EEPROM READ

| BSF   | STATUS, RPO | ; Bank 1          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | ;                 |

| MOVWF | EEADR       | ; Address to read |

| BSF   | EECON1, RD  | ; EE Read         |

| MOVF  | EEDATA, W   | ; W = EEDATA      |

| BCF   | STATUS, RPO | ; Bank 0          |

### 13.4 WRITING TO THE EEPROM DATA MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

# EXAMPLE 13-2: DATA EEPROM WRITE

| WOVWW       SSN       ;         MOVWF       EECON2       ;         Write       SSN       ;         MOVWF       EECON2       ;         WOVWF       EECON2       ;         Write       AAh       ;         BSF       EECON1,WR       ;         BSF       EECON1,WR       ;         BSF       INTCON, GIE       ;         Enable       INTs. | Required<br>Sequence | MOVLW AAh<br>MOVWF EECON2<br>BSF EECON1,WR | ;<br>; Write AAh<br>; Set WR bit<br>; begin write |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will cause the data not to be written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit in the PIR1 registers must be cleared by software.

# 13.5 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 13-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

#### EXAMPLE 13-3: WRITE VERIFY

```

BSF

STATUS, RP0 ; Bank 1

MOVF

EEDATA, W

BSF

EECON1, RD

; Read the

; value written

; Is the value written (in W reg) and

; read (in EEDATA) the same?

SUBWF EEDATA, W

BCF STATUS, RPO ; Bank0

BTFSS STATUS, Z

; Is difference 0?

GOTO WRITE ERR

; NO, Write error

; YES, Good write

:

; Continue program

.

```

# 13.6 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence, and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

### 13.7 DATA EEPROM OPERATION DURING CODE PROTECT

When the device is code protected, the CPU is able to read and write unscrambled data to the Data EEPROM.

#### 14.2.6 INTERNAL 4 MHz OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

#### 14.2.7 CLKOUT

The PIC16F62X can be configured to provide a clock out signal by programming the configuration word. The oscillator frequency, divided by 4 can be used for test purposes or to synchronize other logic.

## 14.3 Special Feature: Dual Speed Oscillator Modes

A software programmable Dual Speed Oscillator mode is provided when the PIC16F62X is configured in either ER or INTRC Oscillator modes. This feature allows users to dynamically toggle the oscillator speed between 4 MHz and 37 kHz. In ER mode, the 4 MHz setting will vary depending on the value of the external resistor. Also in ER mode, the 37 kHz operation is fixed and does not vary with resistor value. Applications that require low current power savings, but cannot tolerate putting the part into SLEEP, may use this mode.

The OSCF bit in the PCON register is used to control Dual Speed mode. See Section 3.2.2.6, Register 3-4.

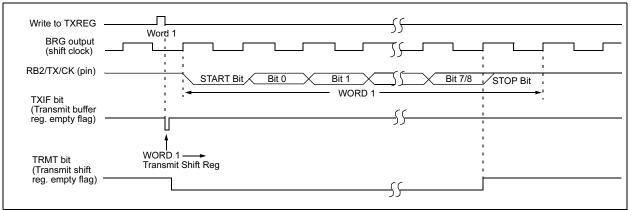

### 14.4 RESET

The PIC16F62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT Wake-up (SLEEP)

- f) Brown-out Detect (BOD)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT Wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 14-5. These bits are used in software to determine the nature of the RESET. See Table 14-8 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 14-6.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 17-6 for pulse width specification.

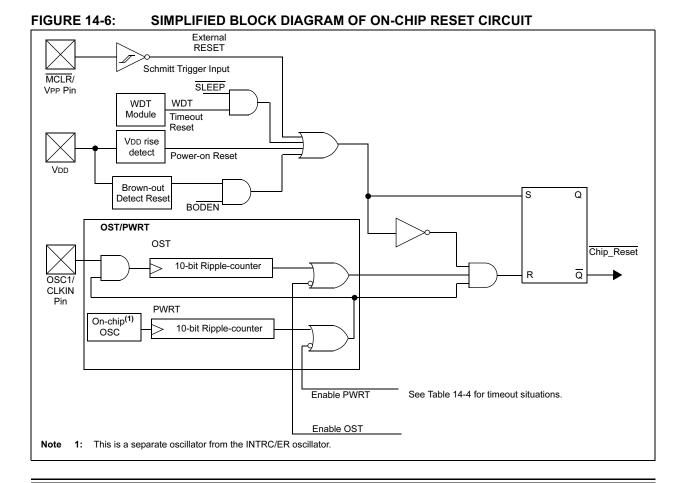

# 15.0 INSTRUCTION SET SUMMARY

Each PIC16F62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F62X instruction set summary in Table 15-2 lists byte-oriented, bitoriented, and literal and control operations. Table 15-1 shows the opcode field descriptions.

For byte-oriented instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For bit-oriented instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For literal and control operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLA<br>TH    | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| то            | Timeout bit                                                                                                                                                                    |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 15-1 shows the three general formats that the instructions can have.

- Note 1: Any unused opcode is reserved. Use of any reserved opcode may cause unexpected operation.

- 2: To maintain upward compatibility with future PICmicro<sup>®</sup> products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

## TABLE 15-2: PIC16F62X INSTRUCTION SET

| Mnemonic,<br>Operands |         | Description                  |                  | 14-Bit Opcode |      |      |       | Status   | Notes |

|-----------------------|---------|------------------------------|------------------|---------------|------|------|-------|----------|-------|

|                       |         |                              |                  | MSb           |      |      | LSb   | Affected | Notes |

| BYTE-ORIE             | NTED F  | ILE REGISTER OPERATIONS      |                  |               |      |      |       |          |       |

| ADDWF                 | f, d    | Add W and f                  | 1                | 00            | 0111 | dfff | ffff  | C,DC,Z   | 1,2   |

| ANDWF                 | f, d    | AND W with f                 | 1                | 00            | 0101 | dfff | ffff  | Z        | 1,2   |

| CLRF                  | f       | Clear f                      | 1                | 00            | 0001 | lfff | ffff  | Z        | 2     |

| CLRW                  | _       | Clear W                      | 1                | 00            | 0001 | 0000 | 0011  | Z        |       |

| COMF                  | f, d    | Complement f                 | 1                | 00            | 1001 | dfff | ffff  | Z        | 1,2   |

| DECF                  | f, d    | Decrement f                  | 1                | 00            | 0011 | dfff | ffff  | Z        | 1,2   |

| DECFSZ                | f, d    | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 00            | 1011 | dfff | ffff  |          | 1,2,3 |

| INCF                  | f, d    | Increment f                  | 1                | 00            | 1010 | dfff | ffff  | Z        | 1,2   |

| INCFSZ                | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 00            | 1111 | dfff | ffff  |          | 1,2,3 |

| IORWF                 | f, d    | Inclusive OR W with f        | 1                | 00            | 0100 | dfff | ffff  | Z        | 1,2   |

| MOVF                  | f, d    | Move f                       | 1                | 00            | 1000 | dfff | ffff  | Z        | 1,2   |

| MOVWF                 | f       | Move W to f                  | 1                | 00            | 0000 | lfff | ffff  |          |       |

| NOP                   | _       | No Operation                 | 1                | 00            | 0000 | 0xx0 | 0000  |          |       |

| RLF                   | f, d    | Rotate Left f through Carry  | 1                | 00            | 1101 | dfff | ffff  | С        | 1,2   |

| RRF                   | f, d    | Rotate Right f through Carry | 1                | 00            | 1100 | dfff | ffff  | С        | 1,2   |

| SUBWF                 | f, d    | Subtract W from f            | 1                | 0.0           | 0010 | dfff | ffff  | C,DC,Z   | 1,2   |

| SWAPF                 | f, d    | Swap nibbles in f            | 1                | 0.0           | 1110 | dfff | ffff  | -, -,    | 1,2   |

| XORWF                 | f, d    | Exclusive OR W with f        | 1                | 00            | 0110 | dfff | ffff  | Z        | 1,2   |

| BIT-ORIENT            | ED FILE | EREGISTER OPERATIONS         |                  |               |      |      |       |          |       |

| BCF                   | f, b    | Bit Clear f                  | 1                | 01            | 00bb | bfff | ffff  |          | 1,2   |

| BSF                   | f, b    | Bit Set f                    | 1                | 01            | 01bb | bfff | ffff  |          | 1,2   |

| BTFSC                 | f, b    | Bit Test f, Skip if Clear    | 1 <sup>(2)</sup> | 01            | 10bb | bfff | ffff  |          | 3     |

| BTFSS                 | f, b    | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 01            | 11bb |      | ffff  |          | 3     |

| LITERAL AN            | ND CON  | TROL OPERATIONS              |                  |               |      |      |       |          |       |

| ADDLW                 | k       | Add literal and W            | 1                | 11            | 111x | kkkk | kkkk  | C,DC,Z   |       |

| ANDLW                 | k       | AND literal with W           | 1                | 11            | 1001 | kkkk | kkkk  | Z        |       |

| CALL                  | k       | Call subroutine              | 2                | 10            | 0kkk | kkkk | kkkk  |          |       |

| CLRWDT                | _       | Clear Watchdog Timer         | 1                | 00            | 0000 | 0110 | 0100  | TO,PD    |       |

| GOTO                  | k       | Go to address                | 2                | 10            | 1kkk | kkkk | kkkk  | ,        |       |

| IORLW                 | k       | Inclusive OR literal with W  | 1                | 11            | 1000 | kkkk | kkkk  | Z        |       |

| MOVLW                 | k       | Move literal to W            | 1                | 11            | 00xx | kkkk | kkkk  |          |       |

| RETFIE                | _       | Return from interrupt        | 2                | 0.0           | 0000 | 0000 | 1001  |          |       |

| RETLW                 | k       | Return with literal in W     | 2                | 11            | 01xx | kkkk | kkkk  |          |       |

| RETURN                | _       | Return from Subroutine       | 2                | 00            | 0000 | 0000 | 1000  |          |       |

| SLEEP                 | _       | Go into Standby mode         | 1                | 00            | 0000 | 0110 | 0011  | TO, PD   |       |

| SUBLW                 | k       | Subtract W from literal      | 1                | 11            | 110x | kkkk | kkkk  | C,DC,Z   |       |

| XORLW                 | k       | Exclusive OR literal with W  | 1                | 11            | 1010 | kkkk | kkkk  | Z        |       |

|                       | IX.     |                              |                  | **            | T0T0 | VVVV | VIVIV | -        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# PIC16F62X

# 17.1 DC Characteristics: PIC16F62X-04 (Commercial, Industrial, Extended) PIC16F62X-20 (Commercial, Industrial, Extended) PIC16LF62X-04 (Commercial, Industrial)

| PIC16LF62X-04<br>(Commercial, Industrial)                          |                                    |                                                                                                                                                                  | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ for industrial and} \\ & 0^{\circ}C \leq Ta \leq +70^{\circ}C \mbox{ for commercial} \end{array}$ |                                                      |                           |                      |                                                                                    |  |  |

|--------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|----------------------|------------------------------------------------------------------------------------|--|--|

| PIC16F62X-04<br>PIC16F62X-20<br>(Commercial, Industrial, Extended) |                                    |                                                                                                                                                                  |                                                                                                                                                                                                                                                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                           |                      |                                                                                    |  |  |

| Param<br>No.                                                       | Sym                                | Characteristic/Device                                                                                                                                            | Min Typ† Max Units Conditions                                                                                                                                                                                                                                       |                                                      |                           |                      |                                                                                    |  |  |

|                                                                    | IPD                                | Power Down Current* <sup>(2), (3)</sup>                                                                                                                          |                                                                                                                                                                                                                                                                     |                                                      |                           |                      |                                                                                    |  |  |

| D020                                                               |                                    | PIC16LF62X                                                                                                                                                       | _                                                                                                                                                                                                                                                                   | 0.20<br>0.20                                         | 2.0<br>2.2                | μΑ<br>μΑ             | VDD = 2.0<br>VDD = 5.5                                                             |  |  |

| D020                                                               |                                    | PIC16F62X                                                                                                                                                        |                                                                                                                                                                                                                                                                     | 0.20<br>0.20<br>0.20<br>2.70                         | 2.2<br>5.0<br>9.0<br>15.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0<br>VDD = 4.5*<br>VDD = 5.5<br>VDD = 5.5 Extended                         |  |  |

| D023                                                               | ΔIWDT<br>ΔIBOD<br>ΔICOMP<br>ΔIVREF | WDT Current <sup>(4)</sup><br>Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup><br>VREF Current <sup>(4)</sup> | <br>                                                                                                                                                                                                                                                                | 6.0<br>75<br>30                                      | 15<br>125<br>50<br>135    | μΑ<br>μΑ<br>μΑ       | $\frac{V_{DD}}{BOD} = 3.0V$<br>BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V |  |  |

| Daga                                                               | ∆Iwdt                              | WDT Current <sup>(4)</sup>                                                                                                                                       | _                                                                                                                                                                                                                                                                   | 6.0                                                  | 20<br>25                  | μΑ<br>μΑ             | VDD = 4.0V, Commercial,<br>Industrial<br>VDD = 4.0V, Extended                      |  |  |

| D023                                                               |                                    | Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup>                                                              | _                                                                                                                                                                                                                                                                   | 75<br>30                                             | 125<br>50                 | μΑ<br>μΑ             | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                              |  |  |

|                                                                    | $\Delta$ IVREF                     | VREF Current <sup>(4)</sup>                                                                                                                                      | —                                                                                                                                                                                                                                                                   |                                                      | 135                       | μA                   | VDD = 4.0V                                                                         |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

- 4: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 5: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 17.3 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

2. TppS

| 2. TppS  |                                        |     |              |  |

|----------|----------------------------------------|-----|--------------|--|

| т        |                                        |     |              |  |

| F        | Frequency                              | Т   | Time         |  |

| Lowercas | se subscripts (pp) and their meanings: |     |              |  |

| рр       |                                        |     |              |  |

| ck       | CLKOUT                                 | osc | OSC1         |  |

| io       | I/O port                               | tO  | TOCKI        |  |

| mc       | MCLR                                   |     |              |  |

| Uppercas | se letters and their meanings:         |     |              |  |

| S        |                                        |     |              |  |

| F        | Fall                                   | Р   | Period       |  |

| Н        | High                                   | R   | Rise         |  |

| I        | Invalid (Hi-impedance)                 | V   | Valid        |  |

| L        | Low                                    | Z   | Hi-Impedance |  |

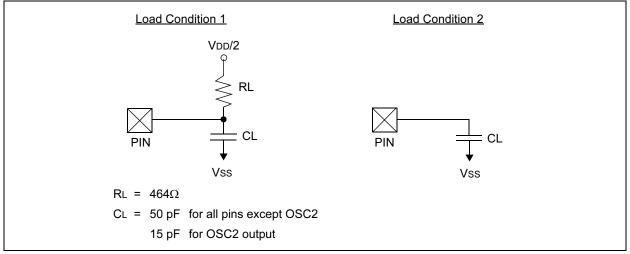

# FIGURE 17-5: LOAD CONDITIONS

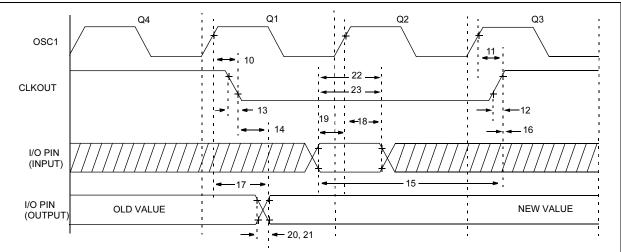

| Param<br>No. | Sym      | Characteristic                                                           |         | Min         | Тур† | Max  | Units |

|--------------|----------|--------------------------------------------------------------------------|---------|-------------|------|------|-------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                                                         | 16F62X  | —           | 75   | 200  | ns    |

| 10A*         |          |                                                                          | 16LF62X | —           | _    | 400  | ns    |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                                                         | 16F62X  | —           | 75   | 200  | ns    |

| 11A*         |          |                                                                          | 16LF62X | —           | _    | 400  | ns    |

| 12*          | TckR     | CLKOUT rise time                                                         | 16F62X  | —           | 35   | 100  | ns    |

| 12A*         |          |                                                                          | 16LF62X | —           | _    | 200  | ns    |

| 13*          | TckF     | CLKOUT fall time                                                         | 16F62X  | —           | 35   | 100  | ns    |

| 13A*         |          |                                                                          | 16LF62X | —           | _    | 200  | ns    |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid                                    |         | —           | _    | 20   | ns    |

| 15*          | TioV2ckH | Port in valid before                                                     | 16F62X  | Tosc+200 ns | _    | —    | ns    |

|              |          | CLKOUT ↑                                                                 | 16LF62X | Tosc=400 ns | _    | —    | ns    |

| 16*          | TckH2iol | Port in hold after CLKOUT $\uparrow$                                     |         | 0           | _    |      | ns    |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to                                                      | 16F62X  | —           | 50   | 150* | ns    |

|              |          | Port out valid                                                           | 16LF62X | —           | _    | 300  | ns    |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) |         | 100<br>200  | _    | —    | ns    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16F62X

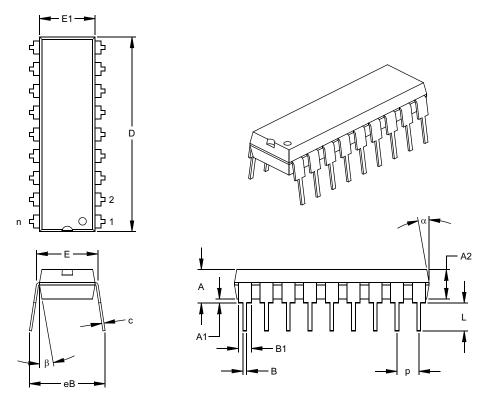

# K04-007 18-Lead Plastic Dual In-line (P) - 300 mil

| s MIN<br>.140 | NOM<br>18<br>.100                            | MAX                                                                                                                                                                                                               | MIN                                                                                                                                                                                                                                                                                                                    | NOM<br>18                                                                                                                                                                                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |