Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627-04e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

#### FIGURE 3-2: DATA MEMORY MAP OF THE PIC16F627 AND PIC16F628

| ndirect addr. <sup>(1)</sup> | 00h        | Indirect addr. <sup>(1)</sup> | 80h         | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|------------------------------|------------|-------------------------------|-------------|-------------------------------|------|-------------------------------|

| TMR0                         | 01h        | OPTION                        | 81h         | TMR0                          | 101h | OPTION                        |

| PCL                          | 02h        | PCL                           | 82h         | PCL                           | 102h | PCL                           |

| STATUS                       | 03h        | STATUS                        | 83h         | STATUS                        | 103h | STATUS                        |

| FSR                          | 04h        | FSR                           | 84h         | FSR                           | 104h | FSR                           |

| PORTA                        | 05h        | TRISA                         | 85h         |                               | 105h |                               |

| PORTB                        | 06h        | TRISB                         | 86h         | PORTB                         | 106h | TRISB                         |

|                              | 07h        |                               | 87h         |                               | 107h |                               |

|                              | 08h        |                               | 88h         |                               | 108h |                               |

|                              | 09h        |                               | 89h         |                               | 109h |                               |

| PCLATH                       | 0Ah        | PCLATH                        | 8Ah         | PCLATH                        | 10Ah | PCLATH                        |

| INTCON                       | 0Bh        | INTCON                        | 8Bh         | INTCON                        | 10Bh | INTCON                        |

| PIR1                         | 0Ch        | PIE1                          | 8Ch         |                               | 10Ch |                               |

|                              | 0Dh        |                               | 8Dh         |                               | 10Dh |                               |

| TMR1L                        | 0Eh        | PCON                          | 8Eh         |                               | 10Eh |                               |

| TMR1H                        | 0Fh        |                               | 8Fh         |                               | 10Fh |                               |

| T1CON                        | 10h        |                               | 90h         |                               |      |                               |

| TMR2                         | 11h        |                               | 91h         |                               |      |                               |

| T2CON                        | 12h        | PR2                           | 92h         |                               |      |                               |

|                              | 13h        |                               | 93h         |                               |      |                               |

|                              | 14h        |                               | 94h         |                               |      |                               |

| CCPR1L                       | 15h        |                               | 95h         |                               |      |                               |

| CCPR1H                       | 16h        |                               | 96h         |                               |      |                               |

| CCP1CON                      | 17h        |                               | 97h         |                               |      |                               |

| RCSTA                        | 18h        | TXSTA                         | 98h         |                               |      |                               |

| TXREG                        | 19h        | SPBRG                         | 99h         |                               |      |                               |

| RCREG                        | 1Ah        | EEDATA                        | 9Ah         |                               |      |                               |

| RONEO                        | 1Bh        | EEADR                         | 9Bh         |                               |      |                               |

|                              | 1Ch        | EECON1                        | 9Ch         |                               |      |                               |

|                              | 1Dh        | EECON2 <sup>(1)</sup>         | 9Dh         |                               |      |                               |

|                              | 1Eh        |                               | 9Eh         |                               |      |                               |

| CMCON                        | 1Fh        | VRCON                         | 9Fh         |                               | 11Fh |                               |

| GINOOIN                      | 20h        |                               |             | General                       | 120h |                               |

| General                      | 2011       | General                       | A0h         | Purpose                       |      |                               |

| Purpose                      |            | Purpose                       |             | Register<br>48 Bytes          | 14Fh |                               |

| Register                     |            | Register                      |             |                               | 150h |                               |

| 80 Bytes                     |            | 80 Bytes                      |             |                               |      |                               |

| -                            | 6Fh        |                               | EFh         |                               | 16Fh |                               |

|                              | 70h        |                               | F0h         |                               | 170h |                               |

| 16 Bytes                     |            | accesses                      |             | accesses                      |      | accesses                      |

|                              | 751        | 70h-7Fh                       |             | 70h-7Fh                       | 1754 | 70h - 7Fh                     |

| Bank 0                       | 7Fh        | Bank 1                        | FFh         | Bank 2                        | 17Fh | Bank 3                        |

| Burne                        |            | _and i                        |             |                               |      |                               |

| Unimplem                     | nented dat | a memory locations, i         | read as '0' |                               |      |                               |

| Address | Name   | Bit 7            | Bit 6            | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|------------------|-------------|--------------|--------------|--------------|--------------|--------------|-----------------------------------------|--------------------|

| Bank 3  |        |                  |                  |             |              |              |              |              |              |                                         |                    |

| 180h    | INDF   | Addressin ister) | ig this location | n uses cont | ents of FSF  | R to address | s data mem   | ory (not a p | hysical reg- | XXXX XXXX                               | 25                 |

| 181h    | OPTION | RBPU             | INTEDG           | TOCS        | TOSE         | PSA          | PS2          | PS1          | PS0          | 1111 1111                               | 20                 |

| 182h    | PCL    | Program (        | Counter's (PC    | ) Least Sig | nificant Byt | e            |              |              |              | 0000 0000                               | 25                 |

| 183h    | STATUS | IRP              | RP1              | RP0         | TO           | PD           | Z            | DC           | С            | 0001 1xxx                               | 19                 |

| 184h    | FSR    | Indirect da      | ata memory a     | ddress poir | nter         | . –          | -            |              | 1-           | xxxx xxxx                               | 25                 |

| 185h    | _      | Unimplem         |                  |             |              |              |              |              |              | _                                       | _                  |

| 186h    | TRISB  | TRISB7           | TRISB6           | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | 1111 1111                               | 34                 |

| 187h    | _      | Unimplem         | nented           | •           |              | •            | •            |              |              | _                                       | —                  |

| 188h    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 189h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Ah    | PCLATH | _                | _                | _           | Write buff   | er for upper | 5 bits of pr | ogram cour   | iter         | 0 0000                                  | 25                 |

| 18Bh    | INTCON | GIE              | PEIE             | T0IE        | INTE         | RBIE         | TOIF         | INTF         | RBIF         | 0000 000x                               | 21                 |

| 18Ch    | _      | Unimplem         | Unimplemented    |             |              |              |              |              |              |                                         | _                  |

| 18Dh    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Eh    |        | Unimplem         | Unimplemented    |             |              |              |              |              |              |                                         | _                  |

| 18Fh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 190h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 191h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 192h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 193h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 194h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 195h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 196h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 197h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 198h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 199h    | —      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 19Ah    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Bh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Ch    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Dh    | —      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 19Eh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Fh    | —      | Unimplem         | nented           |             |              |              |              |              |              | —                                       | —                  |

#### TABLE 3-4: SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

NOTES:

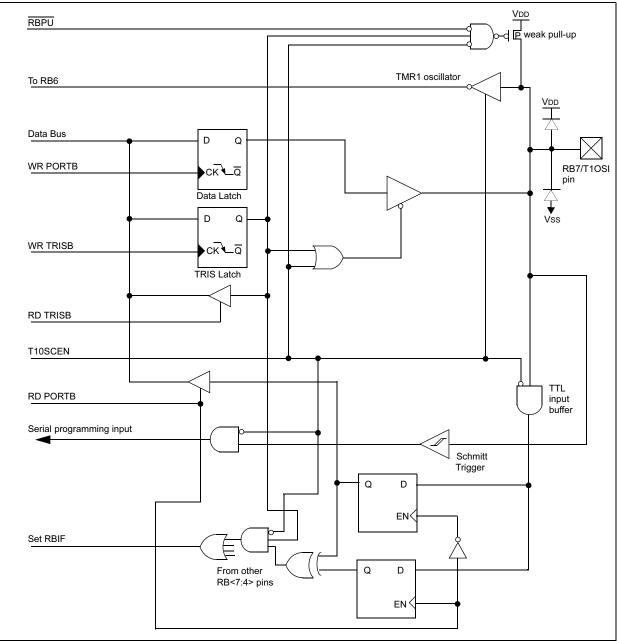

#### FIGURE 5-15: BLOCK DIAGRAM OF THE RB7/T10SI PIN

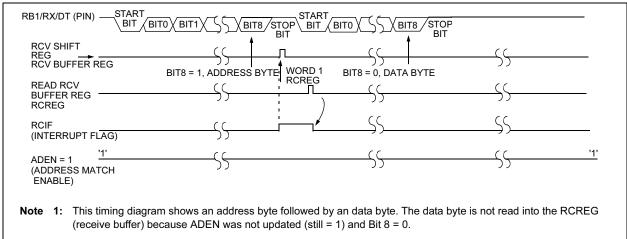

| FIGURE 12-9: | ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT |

|--------------|--------------------------------------------|

|              |                                            |

|                                                               | BIT0 X BIT1 X _ STOP<br>BIT<br>♦ |                               |          |            |

|---------------------------------------------------------------|----------------------------------|-------------------------------|----------|------------|

| RCV SHIFT REG                                                 | (                                |                               | ((       |            |

| RCV BUFFER REG                                                | ) )<br>BIT8 = 0, DATA BYTE       | BIT8 = 1, ADDRESS BYTE WORD 1 |          |            |

| READ RCV                                                      | ((                               | ( C                           | (        | п          |

| BUFFER REG<br>RCREG                                           |                                  |                               |          |            |

| RCIF<br>(INTERRUPT FLAG)                                      |                                  | <u>_</u>                      | <u> </u> | ¥          |

| ADEN = 1 <sup>'<u>1'</u><br/>(ADDRESS MATCH<br/>ENABLE)</sup> | <u>_</u>                         | <u> </u>                      | <u> </u> | <u>'1'</u> |

#### FIGURE 12-10: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

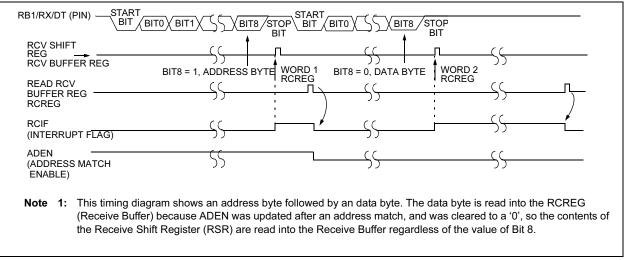

# FIGURE 12-11: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST FOLLOWED BY VALID DATA BYTE

# 13.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead it is indirectly addressed through the Special Function Registers (SFRs). There are four SFRs used to read and write this memory. These registers are:

- EECON1

- EECON2 (Not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F62X devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The writetime will vary with voltage and temperature as well as from chip to chip. Please refer to AC specifications for exact limits.

When the device is code protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the Data EEPROM is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### REGISTER 13-1: EEADR REGISTER (ADDRESS: 9Bh)

| R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

|----------|-------|-------|-------|-------|-------|-------|-------|

| Reserved | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| bit 7    |       |       |       |       |       |       | bit 0 |

#### bit 7 Unimplemented Address: Must be set to '0'

bit 6-0 **EEADR**: Specifies one of 128 locations of EEPROM Read/Write Operation

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 13.1 EEADR

The EEADR register can address up to a maximum of 256 bytes of data EEPROM. Only the first 128 bytes of data EEPROM are implemented and only seven of the eight bits in the register (EEADR<6:0>) are required.

The upper bit is address decoded. This means that this bit should always be '0' to ensure that the address is in the 128 byte memory space.

#### 13.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with five low order bits physically implemented. The upper-three bits are nonexistent and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRER<u>R bit is</u> set when a write operation is interrupted by a MCLR Reset or a WDT Timeout Reset during normal operation. In these situations, following RESET, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit EEIF in the PIR1 register is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the Data EEPROM write sequence.

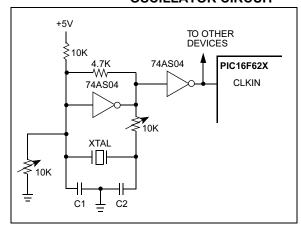

#### FIGURE 14-2: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

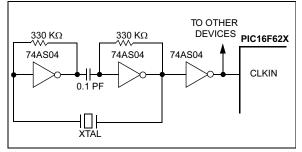

Figure 14-3 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-3: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

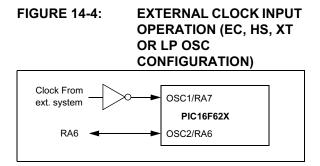

## 14.2.4 EXTERNAL CLOCK IN

For applications, where a clock is already available elsewhere, users may directly drive the PIC16F62X provided that this external clock source meets the AC/DC timing requirements listed in Section 17.4. Figure 14-4 shows how an external clock circuit should be configured.

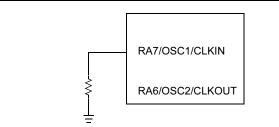

## 14.2.5 ER OSCILLATOR

For timing insensitive applications, the ER (External Resistor) Clock mode offers additional cost savings. Only one external component, a resistor to VSs, is needed to set the operating frequency of the internal oscillator. The resistor draws a DC bias current which controls the oscillation frequency. In addition to the resistance value, the oscillator frequency will vary from unit to unit, and as a function of supply voltage and temperature. Since the controlling parameter is a DC current and not a capacitance, the particular package type and lead frame will not have a significant effect on the resultant frequency.

Figure 14-5 shows how the controlling resistor is connected to the PIC16F62X. For REXT values below 10k, the oscillator operation becomes sensitive to temperature. For very high REXT values (e.g., 1M), the oscillator becomes sensitive to leakage and may stop completely. Thus, we recommend keeping REXT between 10k and 1M.

Table 14-3 shows the relationship between the resistance value and the operating frequency.

#### TABLE 14-3: RESISTANCE AND FREQUENCY RELATIONSHIP

| Resistance | Frequency |

|------------|-----------|

| 0          | 10.4 MHz  |

| 1K         | 10 MHz    |

| 10K        | 7.4 MHz   |

| 20K        | 5.3 MHz   |

| 47K        | 3 MHz     |

| 100K       | 1.6 MHz   |

| 220K       | 800 kHz   |

| 470K       | 300 kHz   |

| 1M         | 200 kHz   |

The ER Oscillator mode has two options that control the unused OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as an output providing the Fosc signal (internal clock divided by 4) for test or external synchronization purposes.

#### 14.5.5 TIMEOUT SEQUENCE

On power-up the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired. Then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in ER mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 14-8, Figure 14-9 and Figure 14-10 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16F62X device operating in parallel.

Table 14-7 shows the RESET conditions for some special registers, while Table 14-8 shows the RESET conditions for all the registers.

#### 14.5.6 POWER CONTROL (PCON) STATUS REGISTER

The Power Control/STATUS register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{BOD}$  (Brown-out).  $\overline{BOD}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOD} = 0$  indicating that a brown-out has occurred. The  $\overline{BOD}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Detect  | Wake-up    |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Reset             | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| ER, INTRC, EC            | 72 ms             | _         | 72 ms             | —          |  |

#### TABLE 14-4: TIMEOUT IN VARIOUS SITUATIONS

| IABLE 14 | TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE |    |    |                                    |  |  |  |  |  |

|----------|-----------------------------------------------------|----|----|------------------------------------|--|--|--|--|--|

| POR      | BOD                                                 | то | PD |                                    |  |  |  |  |  |

| 0        | Х                                                   | 1  | 1  | Power-on Reset                     |  |  |  |  |  |

| 0        | х                                                   | 0  | х  | Illegal, TO is set on POR          |  |  |  |  |  |

| 0        | х                                                   | х  | 0  | Illegal, PD is set on POR          |  |  |  |  |  |

| 1        | 0                                                   | Х  | Х  | Brown-out Detect Reset             |  |  |  |  |  |

| 1        | 1                                                   | 0  | u  | WDT Reset                          |  |  |  |  |  |

| 1        | 1                                                   | 0  | 0  | WDT Wake-up                        |  |  |  |  |  |

| 1        | 1                                                   | u  | u  | MCLR Reset during normal operation |  |  |  |  |  |

| 1        | 1                                                   | 1  | 0  | MCLR Reset during SLEEP            |  |  |  |  |  |

#### TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Legend: u = unchanged, x = unknown.

#### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     | _     | -     | OSCF  | Reset | POR   | BOD   | 1-0x                  | u-uq                                           |

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect Reset and Watchdog Timer Reset during normal operation.

#### TABLE 14-7: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | 1-uu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 1-uu             |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-uu             |

| Brown-out Detect Reset             | 000h                  | 000x xuuu          | 1-u0             |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note** 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on<br>Reset | <ul> <li>MCLR Reset during normal<br/>operation</li> <li>MCLR Reset during SLEEP</li> <li>WDT Reset</li> <li>Brown-out Detect Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP through<br/>interrupt</li> <li>Wake-up from SLEEP through<br/>WDT timeout</li> </ul> |

|----------|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| W        |         | xxxx xxxx         | սսսս սսսս                                                                                                                                                     | սսսս սսսս                                                                                                        |

| INDF     | 00h     | _                 | -                                                                                                                                                             | -                                                                                                                |

| TMR0     | 01h     | xxxx xxxx         | uuuu uuuu                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PCL      | 02h     | 0000 0000         | 0000 0000                                                                                                                                                     | PC + 1 <sup>(3)</sup>                                                                                            |

| STATUS   | 03h     | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                                                                                                                      | uuuq quuu <sup>(4)</sup>                                                                                         |

| FSR      | 04h     | xxxx xxxx         | սսսս սսսս                                                                                                                                                     | uuuu uuuu                                                                                                        |

| PORTA    | 05h     | xxxx 0000         | xxxx u000                                                                                                                                                     | xxxx 0000                                                                                                        |

| PORTB    | 06h     | xxxx xxxx         | uuuu uuuu                                                                                                                                                     | սսսս սսսս                                                                                                        |

| T1CON    | 10h     | 00 0000           | uu uuuu                                                                                                                                                       | uu uuuu                                                                                                          |

| T2CON    | 12h     | -000 0000         | -000 0000                                                                                                                                                     | -uuu uuuu                                                                                                        |

| CCP1CON  | 17h     | 00 0000           | 00 0000                                                                                                                                                       | uu uuuu                                                                                                          |

| RCSTA    | 18h     | 0000 -00x         | 0000 -00x                                                                                                                                                     | uuuu -uuu                                                                                                        |

| CMCON    | 1Fh     | 0000 0000         | 0000 0000                                                                                                                                                     | uu uuuu                                                                                                          |

| PCLATH   | 0Ah     | 0 0000            | 0 0000                                                                                                                                                        | u uuuu                                                                                                           |

| INTCON   | 0Bh     | 0000 000x         | 0000 000u                                                                                                                                                     | uuuu uqqq <sup>(2)</sup>                                                                                         |

| PIR1     | 0Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | -q (2,5)                                                                                                         |

| OPTION   | 81h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| TRISA    | 85h     | 11-1 1111         | 11 1111                                                                                                                                                       | uu-u uuuu                                                                                                        |

| TRISB    | 86h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PIE1     | 8Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | uuuu -uuu                                                                                                        |

| PCON     | 8Eh     | 1-0x              | 1-uq <sup>(1,6)</sup>                                                                                                                                         | uu                                                                                                               |

| TXSTA    | 98h     | 0000 -010         | 0000 -010                                                                                                                                                     | uuuu -uuu                                                                                                        |

| EECON1   | 9Ch     | x000              | q000                                                                                                                                                          | uuuu                                                                                                             |

| VRCON    | 9Fh     | 000- 0000         | 000- 0000                                                                                                                                                     | սսս- սսսս                                                                                                        |

TABLE 14-8:

INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**4**: See Table 14-7 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then Bit 6 = 1. All other interrupts generating a wake-up will cause Bit 6 = u.

6: If RESET was due to brown-out, then Bit 0 = 0. All other RESETS will cause Bit 0 = u.

| CLRW             | Clear W                                                               |                                       |           |       |   | COMF   |

|------------------|-----------------------------------------------------------------------|---------------------------------------|-----------|-------|---|--------|

| Syntax:          | [ label ]                                                             | CLRW                                  |           |       | I | Syntax |

| Operands:        | None                                                                  |                                       |           |       |   | Opera  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (V) \\ 1 \rightarrow Z \end{array}$ | W)                                    |           |       |   | Operat |

| Status Affected: | Z                                                                     |                                       |           |       |   | Status |

| Encoding:        | 00                                                                    | 0001                                  | 0000      | 0011  |   | Encod  |

| Description:     | W regist<br>(Z) is set                                                |                                       | ared. Zer | o bit | I | Descri |

| Words:           | 1                                                                     |                                       |           |       |   |        |

| Cycles:          | 1                                                                     |                                       |           |       |   |        |

| Example          | CLRW                                                                  |                                       |           |       |   | Words  |

|                  | Before In                                                             |                                       |           |       |   | Cycles |

|                  | After Ins<br>V                                                        | V = 0x<br>truction<br>V = 0x<br>Z = 1 |           |       |   | Examp  |

| COMF             | Complement f                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                               |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                        |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the<br>result is stored in W. If 'd' is 1 the<br>result is stored back in register<br>'f'. |

| Words:           | 1                                                                                                                                                        |

| Cycles:          | 1                                                                                                                                                        |

| Example          | COMF REG1, 0                                                                                                                                             |

|                  | Before Instruction<br>REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                        |

| CLRWDT                    | Clear Watchdog Timer                                                                                                                    | DECF             | Decrement f                                                                                                                                 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [label] CLRWDT                                                                                                                          | Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                   |

| Operands:                 | None                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                           |

| Operation:                | $00h \rightarrow WDT$                                                                                                                   |                  | d ∈ [0,1]                                                                                                                                   |

|                           | $0 \rightarrow \frac{\text{WDT}}{\text{TO}}$ prescaler,                                                                                 | Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |

|                           | $1 \rightarrow \underline{TO} \\ 1 \rightarrow \overline{PD}$                                                                           | Status Affected: | Z                                                                                                                                           |

| Status Affected:          | TO, PD                                                                                                                                  | Encoding:        | 00 0011 dfff ffff                                                                                                                           |

| Encoding:<br>Description: | 00000001100100CLRWDT instruction resets the<br>Watchdog Timer. It also resets                                                           | Description:     | Decrement register 'f'. If 'd' is 0<br>the result is stored in the W<br>register. If 'd' is 1 the result is<br>stored back in register 'f'. |

|                           | the prescaler of the WDT.<br>STATUS bits TO and PD are set.                                                                             | Words:           | 1                                                                                                                                           |

| Words:                    | 1                                                                                                                                       | Cycles:          | 1                                                                                                                                           |

| Cycles:                   | 1                                                                                                                                       | Example          | DECF CNT, 1                                                                                                                                 |

| Example                   | CLRWDT<br>Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = 1<br>PD = 1 |                  | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                       |

| IORLW            | Inclusive OR Literal with W                                                                                        |   |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |   |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |   |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |   |  |  |  |

| Status Affected: | Z                                                                                                                  |   |  |  |  |

| Encoding:        | 11 1000 kkkk kkk                                                                                                   | k |  |  |  |

| Description:     | The contents of the W register<br>OR'ed with the eight bit literal '<br>The result is placed in the W<br>register. |   |  |  |  |

| Words:           | 1                                                                                                                  |   |  |  |  |

| Cycles:          | 1                                                                                                                  |   |  |  |  |

| Example          | IORLW 0x35                                                                                                         |   |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 0                                           |   |  |  |  |

| MOVLW            | Move L              | iteral to           | w                                  |      |

|------------------|---------------------|---------------------|------------------------------------|------|

| Syntax:          | [ label ]           | MOVL                | Wk                                 |      |

| Operands:        | $0 \le k \le 2$     | 255                 |                                    |      |

| Operation:       | $k \rightarrow (W)$ | )                   |                                    |      |

| Status Affected: | None                |                     |                                    |      |

| Encoding:        | 11                  | 00xx                | kkkk                               | kkkk |

| Description:     | into W r            |                     | ral 'k' is lo<br>The don't<br>0's. |      |

| Words:           | 1                   |                     |                                    |      |

| Cycles:          | 1                   |                     |                                    |      |

| Example          | MOVLW               | 0x5A                |                                    |      |

|                  |                     | struction<br>= 0x5/ | 4                                  |      |

| IORWF            | Inclusive OR W with f                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                     |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                     |

| Status Affected: | Z                                                                                                                                                                     |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                     |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is<br>1 the result is placed back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                     |

| Cycles:          | 1                                                                                                                                                                     |

| Example          | IORWF REG1, 0                                                                                                                                                         |

|                  | Before Instruction<br>REG1 = 0x13 $W = 0x91$ After Instruction<br>REG1 = 0x13 $W = 0x93$ $Z = 1$                                                                      |

| MOVF             | Move f                                                                                                                                                                                                                                                                           |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                        |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                               |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                         |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                |  |  |  |

|                  | The contents of register f is<br>moved to a destination depen-<br>dent upon the status of d. If d =<br>0, destination is W register. If d<br>= 1, the destination is file regis-<br>ter f itself. d = 1 is useful to test<br>a file register since status flag Z<br>is affected. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                |  |  |  |

| Example          | MOVF REG1, 0                                                                                                                                                                                                                                                                     |  |  |  |

|                  | After Instruction<br>W= value in REG1 register<br>Z = 1                                                                                                                                                                                                                          |  |  |  |

#### TABLE 17-1: COMPARATOR SPECIFICATIONS

|              | Operating Conditions: 3.0V < VDD <5.5V, -40°C < TA < +125°C, unless otherwise stated. |        |     |      |            |          |                   |  |  |

|--------------|---------------------------------------------------------------------------------------|--------|-----|------|------------|----------|-------------------|--|--|

| Param<br>No. | Characteristics                                                                       | Sym    | Min | Тур  | Мах        | Units    | Comments          |  |  |

| D300         | Input offset voltage                                                                  | VIOFF  | _   | ±5.0 | ±10        | mV       |                   |  |  |

| D301*        | Input Common mode voltage                                                             | VICM   | 0   | —    | Vdd - 1.5  | V        |                   |  |  |

| D302*        | Common Mode Rejection Ratio                                                           | CMRR   | 55  | —    | —          | db       |                   |  |  |

| 300*<br>300A | Response Time <sup>(1)</sup>                                                          | TRESP  |     | 150  | 400<br>600 | ns<br>ns | 16F62X<br>16LF62X |  |  |

| 301          | Comparator Mode Change to<br>Output Valid*                                            | TMC2OV | _   | -    | 10         | μS       |                   |  |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

#### TABLE 17-2: VOLTAGE REFERENCE SPECIFICATIONS

|             | Operating Conditions: 3.0V < VDD < 5.5V, -40°C < TA < +125°C, unless otherwise stated. |      |        |     |        |       |                      |  |  |

|-------------|----------------------------------------------------------------------------------------|------|--------|-----|--------|-------|----------------------|--|--|

| Spec<br>No. | Characteristics                                                                        | Sym  | Min    | Тур | Мах    | Units | Comments             |  |  |

| D310        | Resolution                                                                             | VRES | Vdd/24 | —   | VDD/32 | LSb   |                      |  |  |

| D311        | Absolute Accuracy                                                                      | VRaa | _      | _   | 1/4    | LSb   | Low Range (VRR = 1)  |  |  |

|             |                                                                                        |      | —      |     | 1/2    | LSb   | High Range (VRR = 0) |  |  |

| D312*       | Unit Resistor Value (R)                                                                | VRur |        | 2k  | —      | Ω     |                      |  |  |

| 310*        | Settling Time <sup>(1)</sup>                                                           | Tset | —      | —   | 10     | μs    |                      |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

| Param<br>No. | Sym  |                      | Characteristic |         | Min                   | Тур† | Max | Units | Conditions                        |

|--------------|------|----------------------|----------------|---------|-----------------------|------|-----|-------|-----------------------------------|

| 50*          | TccL | CCP                  | No Prescaler   |         | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |      | input low time       |                | 16F62X  | 10                    | _    |     | ns    |                                   |

|              |      |                      | With Prescaler | 16LF62X | 20                    | —    | _   | ns    |                                   |

| 51*          | TccH | ССР                  | No Prescaler   |         | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |      | input high time      |                | 16F62X  | 10                    | —    | _   | ns    |                                   |

|              |      |                      | With Prescaler | 16LF62X | 20                    | —    | _   | ns    |                                   |

| 52*          | TccP | CCP input perio      | od             |         | <u>3Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR | CCP output rise time |                | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |      |                      |                | 16LF62X |                       | 25   | 45  | ns    |                                   |

| 54*          | TccF | CCP output fall t    | ime            | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |      |                      |                | 16LF62X |                       | 25   | 45  | ns    |                                   |

TABLE 17-8: CAPTURE/COMPARE/PWM REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

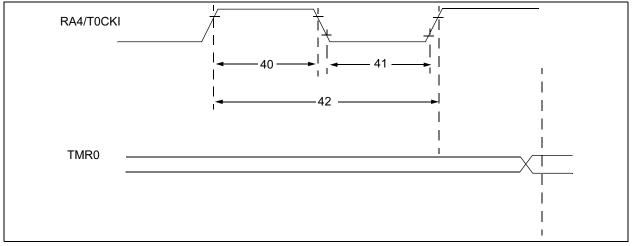

#### FIGURE 17-12: TIMER0 CLOCK TIMING

#### TABLE 17-9: TIMER0 CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Мах | Units | Conditions                            |

|--------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | —    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | _    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _    | _   | ns    | N = prescale value (1, 2,<br>4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. **Note:** The graphs and tables provided in this section are for design guidance and are not tested.

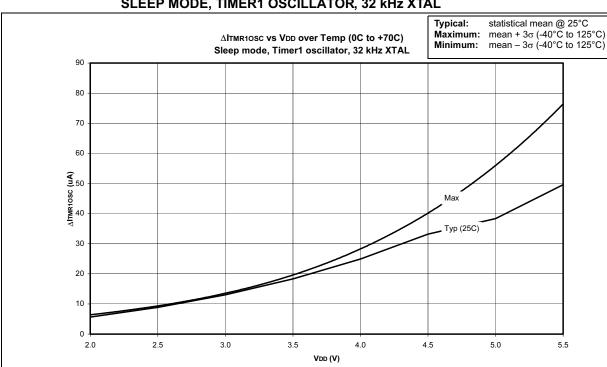

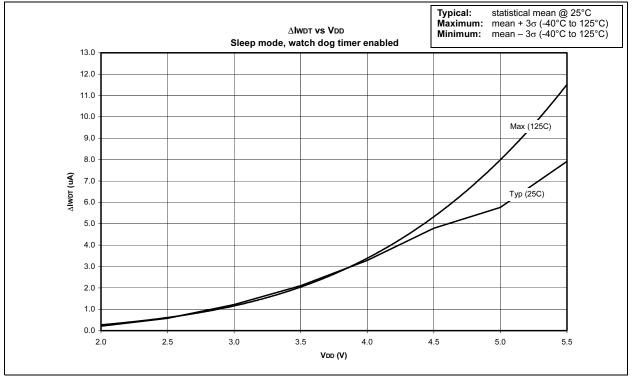

#### FIGURE 18-12: △ITMR10SC VS VDD OVER TEMP (0C to +70°C) SLEEP MODE, TIMER1 OSCILLATOR, 32 kHz XTAL

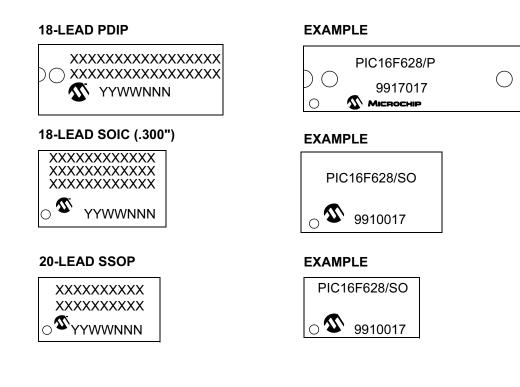

# **19.0 PACKAGING INFORMATION**

## **19.1** Package Marking Information

| Legend: MMM |     | Microchip part number information                                                                                                                                                   |  |  |  |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             | XXX | Customer specific information(1)                                                                                                                                                    |  |  |  |

|             | YY  | Year code (last 2 digits of calendar year)                                                                                                                                          |  |  |  |

|             | WW  | Week code (week of January 1 is week '01')                                                                                                                                          |  |  |  |

|             | NNN | Alphanumeric traceability code                                                                                                                                                      |  |  |  |

| Note:       |     | vent the full Microchip part number cannot be marked on one line, it will be carried<br>he next line thus limiting the number of available characters for customer specific<br>ion. |  |  |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

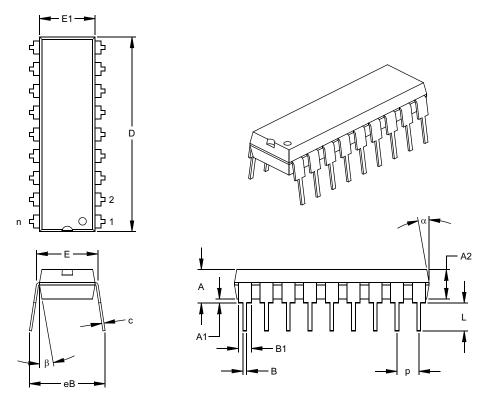

# K04-007 18-Lead Plastic Dual In-line (P) - 300 mil

| n Limits | MIN                                                                 | 11014                                                                                                                                                                                                                                                                                                           |                                                        |                                                        |                                                        |                                                        |

|----------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

|          |                                                                     | NOM                                                                                                                                                                                                                                                                                                             | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |

| n        |                                                                     | 18                                                                                                                                                                                                                                                                                                              |                                                        |                                                        | 18                                                     |                                                        |

| р        |                                                                     | .100                                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 2.54                                                   |                                                        |

| А        | .140                                                                | .155                                                                                                                                                                                                                                                                                                            | .170                                                   | 3.56                                                   | 3.94                                                   | 4.32                                                   |

| A2       | .115                                                                | .130                                                                                                                                                                                                                                                                                                            | .145                                                   | 2.92                                                   | 3.30                                                   | 3.68                                                   |

| A1       | .015                                                                |                                                                                                                                                                                                                                                                                                                 |                                                        | 0.38                                                   |                                                        |                                                        |

| E        | .300                                                                | .313                                                                                                                                                                                                                                                                                                            | .325                                                   | 7.62                                                   | 7.94                                                   | 8.26                                                   |

| E1       | .240                                                                | .250                                                                                                                                                                                                                                                                                                            | .260                                                   | 6.10                                                   | 6.35                                                   | 6.60                                                   |

| D        | .890                                                                | .898                                                                                                                                                                                                                                                                                                            | .905                                                   | 22.61                                                  | 22.80                                                  | 22.99                                                  |

| L        | .125                                                                | .130                                                                                                                                                                                                                                                                                                            | .135                                                   | 3.18                                                   | 3.30                                                   | 3.43                                                   |

| С        | .008                                                                | .012                                                                                                                                                                                                                                                                                                            | .015                                                   | 0.20                                                   | 0.29                                                   | 0.38                                                   |

| B1       | .045                                                                | .058                                                                                                                                                                                                                                                                                                            | .070                                                   | 1.14                                                   | 1.46                                                   | 1.78                                                   |

| В        | .014                                                                | .018                                                                                                                                                                                                                                                                                                            | .022                                                   | 0.36                                                   | 0.46                                                   | 0.56                                                   |

| eB       | .310                                                                | .370                                                                                                                                                                                                                                                                                                            | .430                                                   | 7.87                                                   | 9.40                                                   | 10.92                                                  |