Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 224 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627-20-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

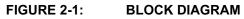

## PIC16F62X

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |

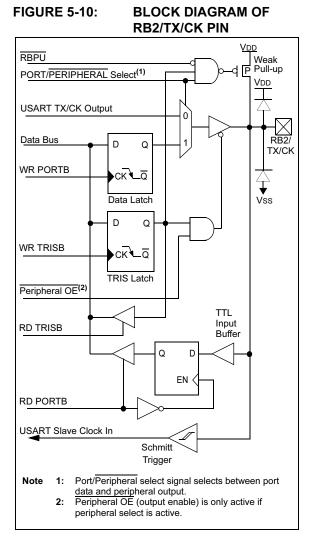

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |

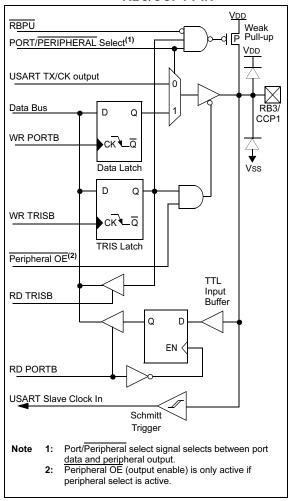

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

## 3.0 MEMORY ORGANIZATION

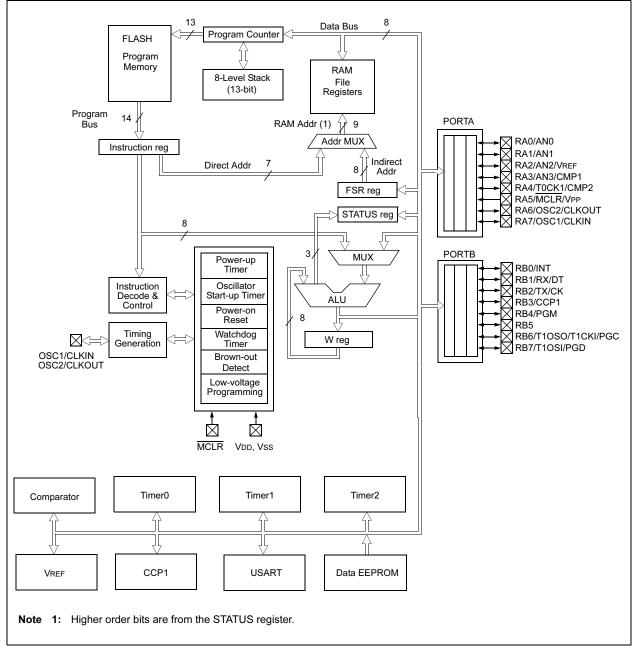

### 3.1 Program Memory Organization

The PIC16F62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) for the PIC16F627 and 2K x 14 (0000h - 07FFh) for the PIC16F628 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space (PIC16F627) or 2K x 14 space (PIC16F628). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 3-1).

FIGURE 3-1: PROGRAM MEMORY MAP AND STACK

## 3.2 Data Memory Organization

The data memory (Figure 3-2) is partitioned into four banks, which contain the general purpose registers and the Special Function Registers (SFR). The SFR's are located in the first 32 locations of each Bank. Register locations 20-7Fh, A0h-FFh, 120h-14Fh, 170h-17Fh and 1F0h-1FFh are general purpose registers implemented as static RAM.

The Table below lists how to access the four banks of registers:

|       | RP1 | RP0 |

|-------|-----|-----|

| Bank0 | 0   | 0   |

| Bank1 | 0   | 1   |

| Bank2 | 1   | 0   |

| Bank3 | 1   | 1   |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

### 3.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F62X. Each is accessed either directly or indirectly through the File Select Register FSR (See Section 3.4).

#### PIR1 Register 3.2.2.5

This register contains interrupt flag bits.

| Note: | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | 0                                                                                         |  |  |  |  |  |

|       | its corresponding enable bit or the global                                                |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User                                                         |  |  |  |  |  |

|       | software should ensure the appropriate                                                    |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                           |  |  |  |  |  |

|       | an interrupt.                                                                             |  |  |  |  |  |

| REGISTER 3-5: | PIR1 REG | ISTER (AD | DRESS: | 0Ch) |  |

|---------------|----------|-----------|--------|------|--|

|               | R/W-0    | R/W-0     | R-0    | R-0  |  |

|       | R/W-0                                                                                                                                                       | R/W-0                      | R-0                            | R-0           | U-0              | R/W-0     | R/W-0          | R/W-0  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------|---------------|------------------|-----------|----------------|--------|--|--|

|       | EEIF                                                                                                                                                        | CMIF                       | RCIF                           | TXIF          |                  | CCP1IF    | TMR2IF         | TMR1IF |  |  |

|       | bit 7                                                                                                                                                       |                            |                                |               |                  | I         |                | bit 0  |  |  |

| bit 7 | EEIF: EEP                                                                                                                                                   | ROM Write                  | Operation I                    | nterrupt Flag | a bit            |           |                |        |  |  |

|       | <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation has not completed or has not been started</li></ul> |                            |                                |               |                  |           |                |        |  |  |

| bit 6 | CMIF: Comparator Interrupt Flag bit                                                                                                                         |                            |                                |               |                  |           |                |        |  |  |

|       | <ul> <li>1 = Comparator output has changed</li> <li>0 = Comparator output has not changed</li> </ul>                                                        |                            |                                |               |                  |           |                |        |  |  |

| bit 5 | RCIF: USA                                                                                                                                                   | RT Receive                 | Interrupt F                    | lag bit       |                  |           |                |        |  |  |

|       |                                                                                                                                                             |                            | e buffer is f<br>e buffer is e |               |                  |           |                |        |  |  |

| bit 4 |                                                                                                                                                             |                            |                                |               |                  |           |                |        |  |  |

| DIL 4 |                                                                                                                                                             |                            | t Interrupt F<br>nit buffer is | -             |                  |           |                |        |  |  |

|       |                                                                                                                                                             |                            | nit buffer is                  |               |                  |           |                |        |  |  |

| bit 3 | Unimplem                                                                                                                                                    | ented: Rea                 | d as '0'                       |               |                  |           |                |        |  |  |

| bit 2 | CCP1IF: C                                                                                                                                                   | CP1 Interru                | pt Flag bit                    |               |                  |           |                |        |  |  |

|       | 0 <b>= No T</b>                                                                                                                                             | IR1 register<br>MR1 regist | r capture oc<br>er capture c   |               | at be cleared in | software) |                |        |  |  |

|       | <u>Compare Mode</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred              |                            |                                |               |                  |           |                |        |  |  |

|       | <u>PWM Mode</u><br>Unused                                                                                                                                   | <u>-</u><br>in this mode   | 9                              |               |                  |           |                |        |  |  |

| bit 1 | TMR2IF: T                                                                                                                                                   | MR2 to PR2                 | 2 Match Inte                   | errupt Flag b | it               |           |                |        |  |  |

|       | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred   |                            |                                |               |                  |           |                |        |  |  |

| bit 0 | TMR1IF: T                                                                                                                                                   | MR1 Overf                  | low Interrup                   | t Flag bit    |                  |           |                |        |  |  |

|       | <b>TMR1IF</b> : TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow        |                            |                                |               |                  |           |                |        |  |  |

|       | Legend:                                                                                                                                                     |                            |                                |               |                  |           |                |        |  |  |

|       | R = Reada                                                                                                                                                   | ble bit                    | VV = V                         | Vritable bit  | U = Unimpl       | emented b | it, read as '( | )'     |  |  |

|       | -n = Value                                                                                                                                                  | at POR                     | '1' = E                        | Bit is set    | '0' = Bit is c   | leared    | x = Bit is ur  | nknown |  |  |

## 5.0 I/O PORTS

The PIC16F62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

### 5.1 PORTA and TRISA Registers

PORTA is an 8-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. RA5 is a Schmitt Trigger input only and has no output drivers. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

Note: RA5 shares function with VPP. When VPP voltage levels are applied to RA5, the device will enter Programming mode.

- **Note 1:** On RESET, the TRISA register is set to all inputs. The digital inputs are disabled and the comparator inputs are forced to ground to reduce current consumption.

- 2: TRISA<6:7> is overridden by oscillator configuration. When PORTA<6:7> is overridden, the data reads '0' and the TRISA<6:7> bits are ignored.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

### EXAMPLE 5-1: Initializing PORTA

| CLRF  | PORTA   | ;Initialize PORTA by<br>;setting output data latches                                                     |

|-------|---------|----------------------------------------------------------------------------------------------------------|

| MOVLW |         | ;Turn comparators off and                                                                                |

| MOVWF | CMCON   | ;enable pins for I/O<br>;functions                                                                       |

| BCF   | STATUS, | RP1                                                                                                      |

| BSF   | STATUS, | RP0;Select Bank1                                                                                         |

| MOVLW | 0x1F    | ;Value used to initialize<br>;data direction                                                             |

| MOVWF | TRISA   | ;Set RA<4:0> as inputs<br>;TRISA<5> always<br>;read as `1'.<br>;TRISA<7:6><br>;depend on oscillator mode |

### FIGURE 5-11: BLOCK DIAGRAM OF RB3/CCP1 PIN

### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). Use the instruction sequences, shown in Example 6-1, when changing the prescaler assignment from Timer0 to WDT, to avoid an unintended device RESET.

### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF    | STATUS, RPO | ;Skip if already in<br>;Bank 0 |

|--------|-------------|--------------------------------|

| CLRWDT |             | ;Clear WDT                     |

|        |             | •                              |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler        |

| BSF    | STATUS, RPO | ;Bank 1                        |

| MOVLW  | '00101111'b | ;These 3 lines                 |

|        |             | ;(5, 6, 7)                     |

| MOVWF  | OPTION_REG  | ;are required only             |

|        |             | ;if desired PS<2:0>            |

|        |             | ;are                           |

| CLRWDT |             | ;000 or 001                    |

| MOVLW  | '00101xxx'b | ;Set Postscaler to             |

| MOVWF  | OPTION_REG  | ;desired WDT rate              |

| BCF    | STATUS, RPO | ;Return to Bank 0              |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                           | ;Clear WDT and<br>;prescaler                              |

|--------------|---------------------------|-----------------------------------------------------------|

| BSF          | STATUS, RPO               |                                                           |

| MOVLW        | b'xxxx0xxx'               | ;Select TMR0, new<br>;prescale value and<br>;clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS, RP0 |                                                           |

| Address               | Name                  | Bit 7    | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------------------|-----------------------|----------|-------------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h                   | TMR0                  | Timer0 m | odule regis | ster   |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE      | PEIE        | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h, 181h             | OPTION <sup>(2)</sup> | RBPU     | INTEDG      | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h                   | TRISA                 | TRISA7   | TRISA6      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**REGISTERS ASSOCIATED WITH TIMER0**

**Note 1:** Shaded bits are not used by TMR0 module.

**TABLE 6-1**:

2: Option is referred by OPTION REG in MPLAB.

## 7.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq    | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

**Note 1:** These values are for design guidance only. Consult AN826 (DS00826A) for further information on Crystal/Capacitor Selection.

## 7.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The spe           | cial e | event | trigg | ers from tl | he CC | CP1 |  |

|-------|-------------------|--------|-------|-------|-------------|-------|-----|--|

|       | module            | will   | not   | set   | interrupt   | flag  | bit |  |

|       | TMR1IF (PIR1<0>). |        |       |       |             |       |     |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

## 7.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other RESET except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

### 7.7 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7      | Bit 6       | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|------------|-------------|---------|-----------|-----------|--------|--------|--------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE        | PEIE        | TOIE    | INTE      | RBIE      | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF       | CMIF        | RCIF    | TXIF      | I         | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE       | CMIE        | RCIE    | TXIE      | I         | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 0Eh                   | TMR1L  | Holding re | egister for |         | xxxx xxxx | uuuu uuuu |        |        |        |                 |                                 |

| 0Fh                   | TMR1H  | Holding re | gister for  |         | xxxx xxxx | uuuu uuuu |        |        |        |                 |                                 |

| 10h                   | T1CON  | _          | _           | T1CKPS1 | T1CKPS0   | T1OSCEN   | T1SYNC | TMR1CS | TMR10N | 00 0000         | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

### 11.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

### 11.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

### 11.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

| Address                   | Name    | Bit 7    | Bit 6                               | Bit 5       | Bit 4         | Bit 3          | Bit 2       | Bit 1      | Bit 0  | Value on<br>POR |      | Value on<br>all other<br>RESETS |      |  |

|---------------------------|---------|----------|-------------------------------------|-------------|---------------|----------------|-------------|------------|--------|-----------------|------|---------------------------------|------|--|

| 0Bh/8Bh/<br>10Bh/<br>18Bh | INTCON  | GIE      | PEIE                                | TOIE        | INTE          | RBIE           | TOIF        | INTF       | RBIF   | 0000            | 000x | 0000                            | 000u |  |

| 0Ch                       | PIR1    | EEIF     | CMIF                                | RCIF        | TXIF          | _              | CCP1IF      | TMR2IF     | TMR1IF | 0000            | -000 | 0000                            | -000 |  |

| 8Ch                       | PIE1    | EEIE     | CMIF                                | RCIE        | TXIE          | _              | CCP1IE      | TMR2IE     | TMR1IE | 0000            | -000 | 0000                            | -000 |  |

| 87h                       | TRISB   | PORTB    | Data Dii                            | rection Reg | ister         |                |             |            |        | 1111            | 1111 | 1111                            | 1111 |  |

| 0Eh                       | TMR1L   | Holding  | register                            | for the Lea | st Significar | nt Byte of the | e 16-bit TM | R1 registe | r      | xxxx            | xxxx | uuuu                            | uuuu |  |

| 0Fh                       | TMR1H   | Holding  | register                            | for the Mos | t Significan  | t Byte of the  | 16-bit TM   | R1register |        | xxxx            | xxxx | uuuu                            | uuuu |  |

| 10h                       | T1CON   | _        |                                     | T1CKPS1     | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS     | TMR10N | 00              | 0000 | uu                              | uuuu |  |

| 15h                       | CCPR1L  | Capture/ | Compa                               | re/PWM reg  | gister1 (LSB  | 5)             |             |            |        | xxxx            | xxxx | uuuu                            | uuuu |  |

| 16h                       | CCPR1H  | Capture/ | Capture/Compare/PWM register1 (MSB) |             |               |                |             |            |        |                 |      | uuuu                            | uuuu |  |

| 17h                       | CCP1CON | _        | _                                   | CCP1X       | CCP1Y         | CCP1M3         | CCP1M2      | CCP1M1     | CCP1M0 | 00              | 0000 | 00                              | 0000 |  |

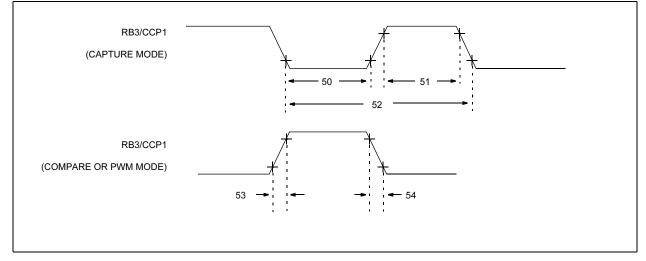

### TABLE 11-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

# PIC16F62X

| CLRW             | Clear W                                                               | COMF      |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|-----------|--|--|--|--|--|--|

| Syntax:          | [label] CLRW                                                          | Syntax    |  |  |  |  |  |  |

| Operands:        | None                                                                  | Opera     |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ | Operat    |  |  |  |  |  |  |

| Status Affected: | Z                                                                     | Status    |  |  |  |  |  |  |

| Encoding:        | 00 0001 0000 00                                                       | Encod     |  |  |  |  |  |  |

| Description:     | W register is cleared. Zero b<br>(Z) is set.                          | it Descri |  |  |  |  |  |  |

| Words:           | 1                                                                     |           |  |  |  |  |  |  |

| Cycles:          | 1                                                                     |           |  |  |  |  |  |  |

| Example          | CLRW                                                                  | Words     |  |  |  |  |  |  |

|                  | Before Instruction                                                    |           |  |  |  |  |  |  |

|                  | W = 0x5A After Instruction $W = 0x00$ $Z = 1$                         | Examp     |  |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                               |  |  |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                      |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                        |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the<br>result is stored in W. If 'd' is 1 the<br>result is stored back in register<br>'f'. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Example          | COMF REG1, 0                                                                                                                                             |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>REG1 = $0x13$<br>After Instruction<br>REG1 = $0x13$<br>W = $0xEC$                                                                  |  |  |  |  |  |  |  |  |

| CLRWDT           | Clear Wa                                           | atchdo   | g Timer   |      | DECF             | Decren                       | nent f             |                |      |  |  |

|------------------|----------------------------------------------------|----------|-----------|------|------------------|------------------------------|--------------------|----------------|------|--|--|

| Syntax:          | [ label ]                                          | CLRW     | 'DT       |      | Syntax:          | [ <i>label</i> ] DECF f,d    |                    |                |      |  |  |

| Operands:        | None                                               |          |           |      | Operands:        | $0 \le f \le f$              | 127                |                |      |  |  |

| Operation:       | $00h \rightarrow W$                                |          |           |      |                  | d ∈ [0,1                     | 1]                 |                |      |  |  |

|                  | $0 \rightarrow WD^{-1}$<br>$1 \rightarrow TO^{-1}$ | T preso  | caler,    |      | Operation:       | (f) - 1 –                    | → (dest)           |                |      |  |  |

|                  | $1 \rightarrow \frac{10}{PD}$                      |          |           |      | Status Affected: | Z                            |                    |                |      |  |  |

| Status Affected: | TO, PD                                             |          |           |      | Encoding:        | 00                           | 0011               | dfff           | ffff |  |  |

| Encoding:        | 00                                                 | 0000     | 0110      | 0100 | Description:     |                              | 0                  | ster 'f'. If ' |      |  |  |

| Description:     | CLRWDT                                             |          |           |      |                  |                              |                    | 1 the resu     |      |  |  |

|                  | Watchdo<br>the presc                               | 0        |           |      |                  | stored back in register 'f'. |                    |                |      |  |  |

|                  | STATUS                                             |          |           |      | Words:           | 1                            |                    |                |      |  |  |

| Words:           | 1                                                  |          |           |      | Cycles:          | 1                            |                    |                |      |  |  |

| Cycles:          | 1                                                  |          |           |      | Example          | DECF                         | CNT,               | 1              |      |  |  |

| Example          | CLRWDT                                             |          |           |      |                  | Before                       | Before Instruction |                |      |  |  |

| ·                | Before In                                          | structio | on        |      |                  |                              | CNT = 7 =          | 0x01<br>0      |      |  |  |

|                  | V                                                  | VDT co   | unter =   | ?    |                  | After Instruction            |                    |                |      |  |  |

|                  | After Inst                                         | truction | 1         |      |                  |                              | CNT =              |                |      |  |  |

|                  |                                                    | VDT co   |           | 0x00 |                  |                              | Z =                | 1              |      |  |  |

|                  |                                                    |          | escaler = |      |                  |                              |                    |                |      |  |  |

|                  | P                                                  | 0        | =         |      |                  |                              |                    |                |      |  |  |

|                  | Г                                                  | D        | -         | • •  |                  |                              |                    |                |      |  |  |

# PIC16F62X

| INCF             | Increment f                                                                                                                                                          | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                               |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                          |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                    | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                    |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                    | Status Affected: | None                                                                                                                                                                                                 |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                    | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result<br>is placed in the W register. If 'd'<br>is 1 the result is placed back in<br>register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result<br>is placed in the W register. If 'd'<br>is 1 the result is placed back in<br>register 'f'.<br>If the result is 0, the next |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                    |                  | instruction, which is already fetched, is discarded. A NOP is                                                                                                                                        |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                    |                  |                                                                                                                                                                                                      |  |  |  |  |  |

| Example          | INCF REG1, 1                                                                                                                                                         |                  | executed instead making it a                                                                                                                                                                         |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                   | \\/anda.         | two-cycle instruction.                                                                                                                                                                               |  |  |  |  |  |

|                  | $\begin{array}{rcl} REG1 = & 0xFF \\ 7 & = & 0 \end{array}$                                                                                                          | Words:           | 1                                                                                                                                                                                                    |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                    | Cycles:          | 1 <sup>(2)</sup>                                                                                                                                                                                     |  |  |  |  |  |

|                  | $\frac{\text{REG1} = 0x00}{\text{Z}} = 1$                                                                                                                            | Example          | HERE INCFSZ REG1, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                  |  |  |  |  |  |

|                  |                                                                                                                                                                      |                  | Before Instruction<br>PC = address HERE                                                                                                                                                              |  |  |  |  |  |

PC = address HERE After Instruction REG1 = REG1 + 1 if CNT = 0, PC = address CONTINUE if REG1≠ 0, PC = address HERE +1

-

| RETLW            | Return with Literal in W                                                                                                                                                               | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                           | Operation:       | $d \in [0,1]$<br>See description below                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                   | Status Affected: | С                                                                                                                                                                                                              |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                              |

| Description:     | The W register is loaded with<br>the eight bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0 the result<br>is placed in the W register. If 'd' is<br>1 the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      | Words:           | 1                                                                                                                                                                                                              |

| Example          | CALL TABLE;W contains table                                                                                                                                                            | Cycles:          | 1                                                                                                                                                                                                              |

|                  | <ul> <li>;offset value</li> <li>;W now has table</li> </ul>                                                                                                                            | -                |                                                                                                                                                                                                                |

|                  | value                                                                                                                                                                                  | Example          | RLF REG1, 0<br>Before Instruction                                                                                                                                                                              |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8             |                  | REG1 = 1110 0110 $C = 0$ After Instruction $REG1 = 1110 0110$ $W = 1100 1100$ $C = 1$                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

| Syntax:          | [label] RETURN                                                                                                                                                                         |                  |                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction.                             |                  |                                                                                                                                                                                                                |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Example          | RETURN                                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                            |                  |                                                                                                                                                                                                                |

### 16.9 MPLAB ICE 2000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PICmicro microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 16.10 MPLAB ICE 4000 High Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PICmicro microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory, and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 16.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low cost, run-time development tool, connecting to the host PC via an RS-232 or high speed USB interface. This tool is based on the FLASH PICmicro MCUs and can be used to develop for these and other PICmicro microcontrollers. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single-stepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PICmicro devices.

### 16.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify, and program PICmicro devices without a PC connection. It can also set code protection in this mode.

### 16.13 PICSTART Plus Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus development programmer supports most PICmicro devices up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

|          | MPLAB Integrated<br>Development Environment | MPLAB C17 C Compiler | MPLAB C18 C Compiler | MPASM Assembler/<br>MPLINK Object Linker | MPLAB C30 C Compiler | MPLAB ASM30<br>Assembler/Linker/Librarian | MPLAB ICE 2000<br>In-Circuit Emulator | MPLAB ICE 4000<br>In-Circuit Emulator | MPLAB ICD 2 In-Circuit<br>Debugger | PICSTART Plus Entry Level<br>Development Programmer | PRO MATE II<br>Universal Device Programmer | <b>PICDEM 1</b> Demonstration Board | PICDEM.net Demonstration<br>Board | PICDEM 2 Plus Demonstration<br>Board | <b>PICDEM 3 Demonstration Board</b> | PICDEM 14A Demonstration<br>Board | PICDEM 17 Demonstration<br>Board | PICDEM 18R Demonstration<br>Board | PICDEM LIN Demonstration<br>Board | PICDEM USB Demonstration<br>Board     |

|----------|---------------------------------------------|----------------------|----------------------|------------------------------------------|----------------------|-------------------------------------------|---------------------------------------|---------------------------------------|------------------------------------|-----------------------------------------------------|--------------------------------------------|-------------------------------------|-----------------------------------|--------------------------------------|-------------------------------------|-----------------------------------|----------------------------------|-----------------------------------|-----------------------------------|---------------------------------------|

| PIC12CXX | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC12FXX | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       | >                                  | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC14000 | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     | >                                 |                                  |                                   |                                   |                                       |

| PIC16C5  | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          | >                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C6  | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     | * ^                                | >                                                   | >                                          |                                     |                                   | 7                                    |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16CX) | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          | >                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C4: | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   | >                                 |                                       |

| PIC16F6  | >                                           |                      |                      | >                                        |                      |                                           | **`^                                  |                                       |                                    | **^                                                 | **/                                        |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C   | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     | *^                                 | >                                                   | >                                          | ⁺,                                  |                                   | ,                                    |                                     |                                   |                                  |                                   |                                   |                                       |