Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

PIC16F62X

# **FLASH-Based 8-Bit CMOS Microcontrollers**

#### **Devices Included in this Data Sheet:**

- PIC16F627

- PIC16F628

Referred to collectively as PIC16F62X

#### **High Performance RISC CPU:**

- · Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- · Operating speed:

- DC 20 MHz clock input

- DC 200 ns instruction cycle

|           | Memory           |             |                |  |  |  |  |

|-----------|------------------|-------------|----------------|--|--|--|--|

| Device    | FLASH<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC16F627 | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16F628 | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

• Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

#### **Peripheral Features:**

- 16 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs are externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Timer1: 16-bit timer/counter with external crystal/ clock capability

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM (CCP) module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- Universal Synchronous/Asynchronous Receiver/ Transmitter USART/SCI

- · 16 Bytes of common RAM

#### **Special Microcontroller Features:**

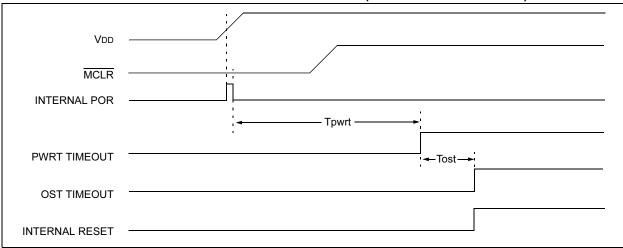

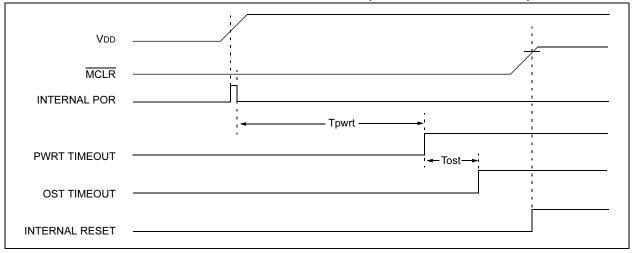

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Multiplexed MCLR-pin

- · Programmable weak pull-ups on PORTB

- · Programmable code protection

- Low voltage programming

- Power saving SLEEP mode

- · Selectable oscillator options

- FLASH configuration bits for oscillator options

- ER (External Resistor) oscillator

- · Reduced part count

- Dual speed INTRC

- Lower current consumption

- EC External Clock input

- XT Oscillator mode

- HS Oscillator mode

- LP Oscillator mode

- In-circuit Serial Programming<sup>™</sup> (via two pins)

- · Four user programmable ID locations

#### **CMOS Technology:**

- Low power, high speed CMOS FLASH technology

- Fully static design

- · Wide operating voltage range

- PIC16F627 3.0V to 5.5V

- PIC16F628 3.0V to 5.5V

- PIC16LF627 2.0V to 5.5V

- PIC16LF628 2.0V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

# PIC16F62X

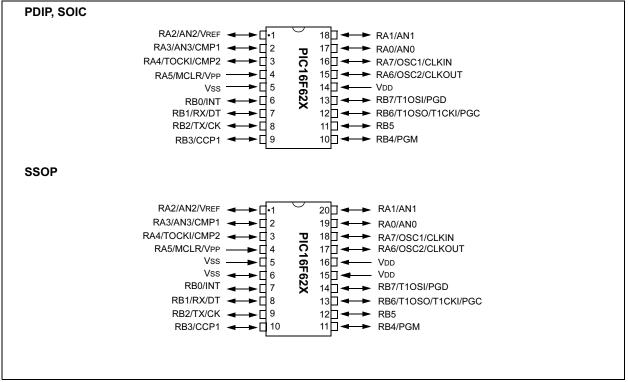

## **Pin Diagrams**

### **Device Differences**

| Device                                      | Voltage<br>Range           | Oscillator                      | Process<br>Technology<br>(Microns) |

|---------------------------------------------|----------------------------|---------------------------------|------------------------------------|

| PIC16F627                                   | 3.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16F628                                   | 3.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16LF627                                  | 2.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16LF628                                  | 2.0 - 5.5                  | (Note 1)                        | 0.7                                |

| Note 1: If you change from the application. | is device to another devic | e, please verify oscillator cha | aracteristics in your              |

# 1.0 PIC16F62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F62X Product Identification System section (Page 167) at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 1.1 FLASH Devices

FLASH devices can be erased and reprogrammed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically-erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus, or PRO MATE<sup>®</sup> II programmers.

### 1.2 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 1.3 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

# TABLE 2-1:PIC16F62X PINOUT DESCRIPTION (CONTINUED)

| Name                                                  | Function | Input Type                    | Output Type | Description                                                                                                                                                                          |

|-------------------------------------------------------|----------|-------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB4/PGM                                               | RB4      | TTL                           | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                       |

|                                                       | PGM      | ST                            | _           | Low voltage programming input pin. Interrupt-<br>on-pin change. When low voltage program-<br>ming is enabled, the interrupt-on-pin change<br>and weak pull-up resistor are disabled. |

| RB5                                                   | RB5      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

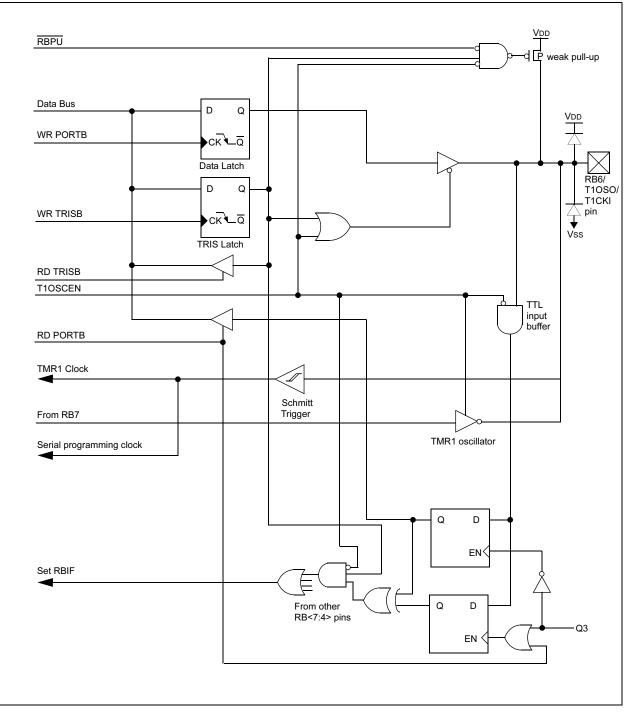

| RB6/T1OSO/T1CKI/PGC                                   | RB6      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

|                                                       | T10SO    | —                             | XTAL        | Timer1 oscillator output.                                                                                                                                                            |

|                                                       | T1CKI    | ST                            | —           | Timer1 clock input.                                                                                                                                                                  |

|                                                       | PGC      | ST                            | _           | ICSP™ Programming Clock.                                                                                                                                                             |

| RB7/T1OSI/PGD                                         | RB7      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

|                                                       | T1OSI    | XTAL                          | _           | Timer1 oscillator input. Wake-up from SLEEP<br>on pin change. Can be software programmed<br>for internal weak pull-up.                                                               |

|                                                       | PGD      | ST                            | CMOS        | ICSP Data I/O                                                                                                                                                                        |

| Vss                                                   | Vss      | Power                         | _           | Ground reference for logic and I/O pins                                                                                                                                              |

| Vdd                                                   | Vdd      | Power                         | —           | Positive supply for logic and I/O pins                                                                                                                                               |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | CMOS = CI<br>I = In<br>OD = O |             | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                               |

NOTES:

© 2003 Microchip Technology Inc.

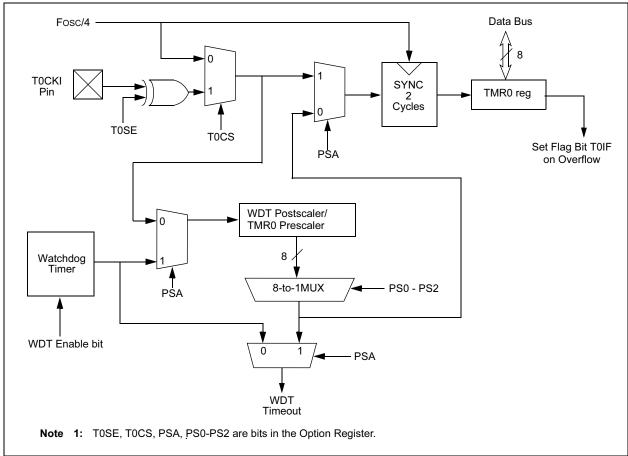

#### 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

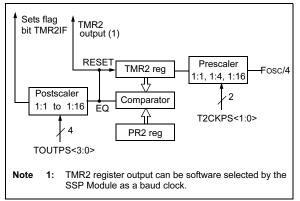

# 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit Period Register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

#### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- · A write to the TMR2 register

- · A write to the T2CON register

- Any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

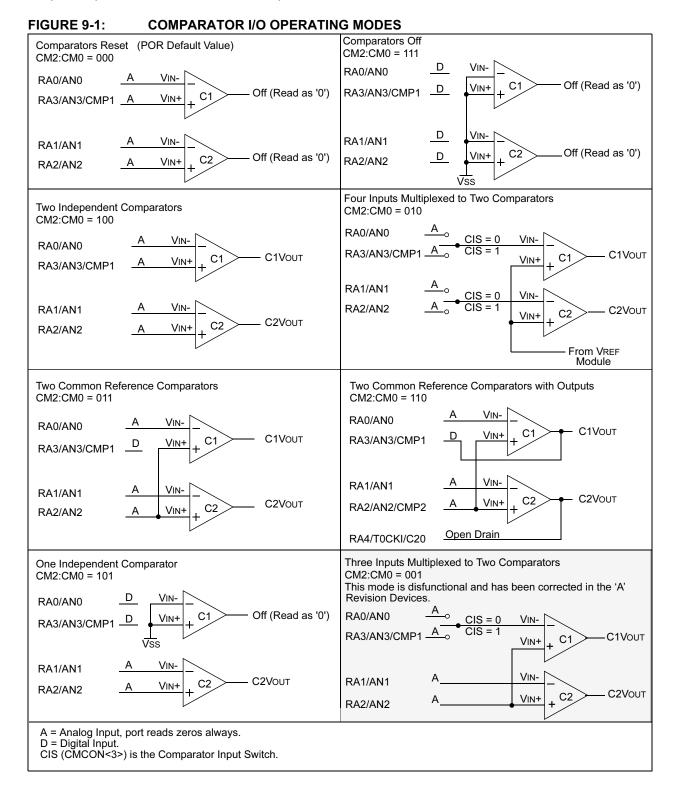

#### 9.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 9-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 17-1.

Note: Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

#### 10.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

#### 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

## 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

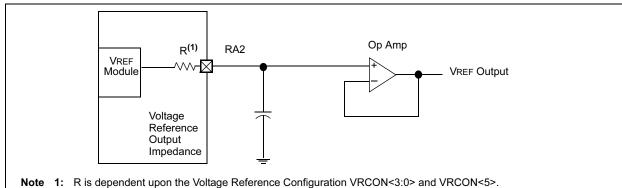

#### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

#### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

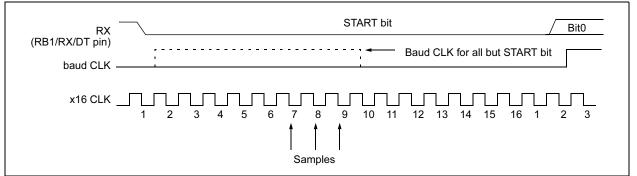

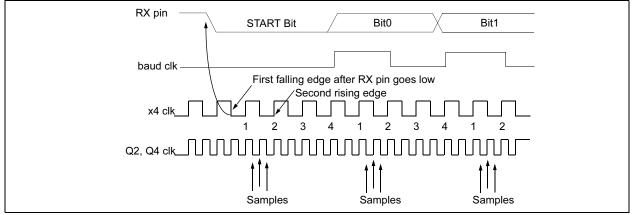

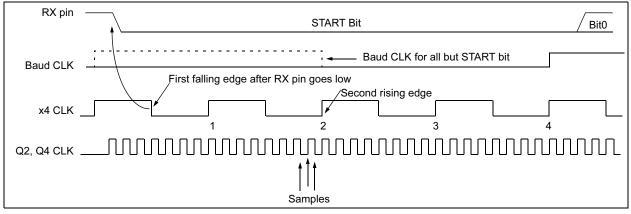

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

#### FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

## FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

#### FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

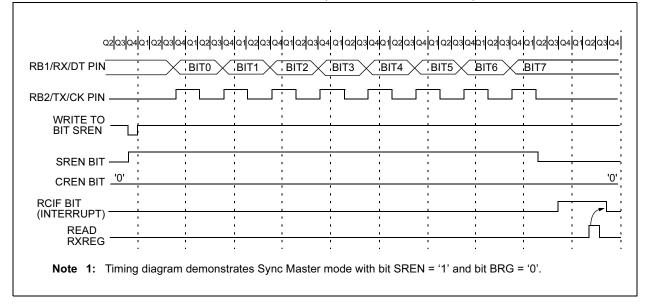

#### 12.4 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RB2/TX/CK and RB1/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART Transmitter Block Diagram is shown in Figure 12-5. The heart of the transmitter is the Transmit (serial) Shift register (TSR). The Shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will RESET only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will RESET the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set, during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however is not RESET although it is disconnected from the pins. In order to RESET the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from Hi-impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

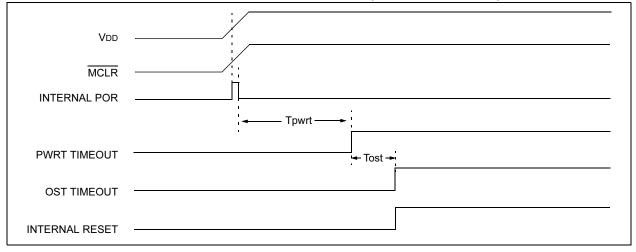

FIGURE 14-9: TIMEOUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 14-10: TIMEOUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

© 2003 Microchip Technology Inc.

#### TABLE 15-2: PIC16F62X INSTRUCTION SET

| Mnemonic,<br>Operands                  |         | Description                  |                  | 14-Bit Opcode |      |         |          | Status   | Notes |

|----------------------------------------|---------|------------------------------|------------------|---------------|------|---------|----------|----------|-------|

|                                        |         |                              |                  | MSb           |      |         | LSb      | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                              |                  |               |      |         |          |          |       |

| ADDWF                                  | f, d    | Add W and f                  | 1                | 00            | 0111 | dfff    | ffff     | C,DC,Z   | 1,2   |

| ANDWF                                  | f, d    | AND W with f                 | 1                | 00            | 0101 | dfff    | ffff     | Z        | 1,2   |

| CLRF                                   | f       | Clear f                      | 1                | 00            | 0001 | lfff    | ffff     | Z        | 2     |

| CLRW                                   | _       | Clear W                      | 1                | 00            | 0001 | 0000    | 0011     | Z        |       |

| COMF                                   | f, d    | Complement f                 | 1                | 00            | 1001 | dfff    | ffff     | Z        | 1,2   |

| DECF                                   | f, d    | Decrement f                  | 1                | 00            | 0011 | dfff    | ffff     | Z        | 1,2   |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 00            | 1011 | dfff    | ffff     |          | 1,2,3 |

| INCF                                   | f, d    | Increment f                  | 1                | 00            | 1010 | dfff    | ffff     | Z        | 1,2   |

| INCFSZ                                 | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 00            | 1111 | dfff    | ffff     |          | 1,2,3 |

| IORWF                                  | f, d    | Inclusive OR W with f        | 1                | 00            | 0100 | dfff    | ffff     | Z        | 1,2   |

| MOVF                                   | f, d    | Move f                       | 1                | 00            | 1000 | dfff    | ffff     | Z        | 1,2   |

| MOVWF                                  | f       | Move W to f                  | 1                | 00            | 0000 | lfff    | ffff     |          |       |

| NOP                                    | _       | No Operation                 | 1                | 00            | 0000 | 0xx0    | 0000     |          |       |

| RLF                                    | f, d    | Rotate Left f through Carry  | 1                | 00            | 1101 | dfff    | ffff     | С        | 1,2   |

| RRF                                    | f, d    | Rotate Right f through Carry | 1                | 00            | 1100 | dfff    | ffff     | С        | 1,2   |

| SUBWF                                  | f, d    | Subtract W from f            | 1                | 00            | 0010 | dfff    | ffff     | C,DC,Z   | 1,2   |

| SWAPF                                  | f, d    | Swap nibbles in f            | 1                | 00            | 1110 | dfff    | ffff     | -, -,    | 1,2   |

| XORWF                                  | f, d    | Exclusive OR W with f        | 1                | 00            | 0110 | dfff    | ffff     | Z        | 1,2   |

| BIT-ORIENT                             | ED FILE | EREGISTER OPERATIONS         |                  |               |      |         |          |          |       |

| BCF                                    | f, b    | Bit Clear f                  | 1                | 01            | 00bb | bfff    | ffff     |          | 1,2   |

| BSF                                    | f, b    | Bit Set f                    | 1                | 01            | 01bb | bfff    | ffff     |          | 1,2   |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear    | 1 <sup>(2)</sup> | 01            | 10bb | bfff    | ffff     |          | 3     |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 01            | 11bb | bfff    | ffff     |          | 3     |

| LITERAL AN                             | ND CON  | TROL OPERATIONS              |                  |               |      |         |          |          |       |

| ADDLW                                  | k       | Add literal and W            | 1                | 11            | 111x | kkkk    | kkkk     | C,DC,Z   |       |

| ANDLW                                  | k       | AND literal with W           | 1                | 11            | 1001 | kkkk    | kkkk     | Z        |       |

| CALL                                   | k       | Call subroutine              | 2                | 10            | 0kkk | kkkk    | kkkk     |          |       |

| CLRWDT                                 | _       | Clear Watchdog Timer         | 1                | 00            | 0000 | 0110    | 0100     | TO,PD    |       |

| GOTO                                   | k       | Go to address                | 2                | 10            | 1kkk | kkkk    | kkkk     |          |       |

| IORLW                                  | k       | Inclusive OR literal with W  | 1                | 11            | 1000 | kkkk    | kkkk     | Z        |       |

| MOVLW                                  | k       | Move literal to W            | 1                | 11            | 00xx | kkkk    | kkkk     |          |       |

| RETFIE                                 | _       | Return from interrupt        | 2                | 00            | 0000 | 0000    | 1001     |          |       |

| RETLW                                  | k       | Return with literal in W     | 2                | 11            | 01xx | kkkk    | kkkk     |          |       |

| RETURN                                 | _       | Return from Subroutine       | 2                | 00            | 0000 | 0000    | 1000     |          |       |

| SLEEP                                  | _       | Go into Standby mode         | 1                | 00            | 0000 | 0110    | 0011     | TO,PD    |       |

| SUBLW                                  | k       | Subtract W from literal      | 1                | 11            | 110x | kkkk    | kkkk     | C,DC,Z   |       |

| XORLW                                  | k       | Exclusive OR literal with W  | 1                | 11            | 1010 | kkkk    | kkkk     | Z        |       |

|                                        |         |                              |                  |               | 7010 | 1010101 | 12121212 | -        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| RETLW            | Return with Literal in W                                                                                                                                                               | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                           | Operation:       | $d \in [0,1]$<br>See description below                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                   | Status Affected: | С                                                                                                                                                                                                              |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                              |

| Description:     | The W register is loaded with<br>the eight bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0 the result<br>is placed in the W register. If 'd' is<br>1 the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      | Words:           | 1                                                                                                                                                                                                              |

| Example          | CALL TABLE;W contains table                                                                                                                                                            |                  | 1                                                                                                                                                                                                              |

|                  | <ul> <li>;offset value</li> <li>;W now has table</li> </ul>                                                                                                                            | Cycles:          |                                                                                                                                                                                                                |

|                  | value                                                                                                                                                                                  | Example          | RLF REG1, 0<br>Before Instruction                                                                                                                                                                              |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8             |                  | REG1 = 1110 0110 $C = 0$ After Instruction $REG1 = 1110 0110$ $W = 1100 1100$ $C = 1$                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

| Syntax:          | [label] RETURN                                                                                                                                                                         |                  |                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction.                             |                  |                                                                                                                                                                                                                |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Example          | RETURN                                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                            |                  |                                                                                                                                                                                                                |

| ABLE         | 17-4. |                                         |        |      |        |       |                               |  |  |

|--------------|-------|-----------------------------------------|--------|------|--------|-------|-------------------------------|--|--|

| Param<br>No. | Sym   | Characteristic                          | Min    | Тур† | Мах    | Units | Conditions                    |  |  |

|              | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC     |      | 4      | MHz   | XT and ER Osc mode,           |  |  |

|              |       |                                         |        |      |        |       | VDD = 5.0V                    |  |  |

|              |       |                                         | DC     | —    | 20     | MHz   | HS Osc mode                   |  |  |

|              |       |                                         | DC     | —    | 200    | kHz   | LP Osc mode                   |  |  |

|              |       | Oscillator Frequency <sup>(1)</sup>     |        |      | 4      | MHz   | ER Osc mode, VDD = 5.0V       |  |  |

|              |       | Costilutor r requeriey                  | 0.1    |      | 4      | MHz   |                               |  |  |

|              |       |                                         | 1      |      | 20     | MHz   |                               |  |  |

|              |       |                                         | '      | _    | 200    | kHz   | LP Osc mode                   |  |  |

|              |       |                                         | 3.65   | 4    | 4.28   | MHz   | INTRC mode (fast), VDD = 5.0V |  |  |

|              |       |                                         |        | 37   |        | kHz   | INTRC mode (slow)             |  |  |

| 4            | INTRC | Internal Calibrated RC                  | 3.65   | 4.00 | 4.28   | MHz   | VDD = 5.0V                    |  |  |

| 5            | ER    | External Biased ER Frequency            | 10 kHz |      | 8 MHz  |       | VDD = 5.0V                    |  |  |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250    | _    |        | ns    | XT and ER Osc mode            |  |  |

|              |       |                                         | 50     | —    | —      | ns    | HS Osc mode                   |  |  |

|              |       |                                         | 5      | —    | —      | μs    | LP Osc mode                   |  |  |

|              |       |                                         |        |      |        |       |                               |  |  |

|              |       | Oscillator Period <sup>(1)</sup>        | 250    | _    |        | ns    | ER Osc mode                   |  |  |

|              |       |                                         | 250    | _    | 10,000 | ns    | XT Osc mode                   |  |  |

|              |       |                                         | 50     | —    | 1,000  | ns    | HS Osc mode                   |  |  |

|              |       |                                         | 5      |      |        | μS    | LP Osc mode                   |  |  |

|              |       |                                         |        | 250  |        | ns    | INTRC mode (fast)             |  |  |

|              |       |                                         |        | 27   |        | μs    | INTRC mode (slow)             |  |  |

| 2            | Тсу   | Instruction Cycle Time                  | 1.0    | Тсү  | DC     | ns    | Tcy = 4/Fosc                  |  |  |

| 3            | TosL, | External CLKIN (OSC1) High              | 100 *  | —    | —      | ns    | XT oscillator, Tosc L/H duty  |  |  |

|              | TosH  | External CLKIN Low                      |        |      |        |       | cycle*                        |  |  |

#### TABLE 17-4: EXTERNAL CLOCK TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (Tcy) equals four times the input oscillator time-based period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max" cycle time limit is "DC" (no clock) for all devices.

| Param<br>No. | Sym                         |                 | Characteristic |         | Min                   | Тур† | Max | Units | Conditions                        |

|--------------|-----------------------------|-----------------|----------------|---------|-----------------------|------|-----|-------|-----------------------------------|

| 50*          | TccL                        | CCP             | No Prescaler   |         | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |                             | input low time  |                | 16F62X  | 10                    | —    | _   | ns    |                                   |

|              |                             |                 | With Prescaler | 16LF62X | 20                    | —    | _   | ns    |                                   |

| 51*          | TccH CCP                    |                 | No Prescaler   |         | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |                             | input high time |                | 16F62X  | 10                    |      |     | ns    |                                   |

|              |                             |                 | With Prescaler | 16LF62X | 20                    |      |     | ns    |                                   |

| 52*          | TccP                        | CCP input perio | d              | ·       | <u>3Tcy + 40</u><br>N | _    |     | ns    | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR                        | CCP output rise | time           | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |                             |                 |                | 16LF62X |                       | 25   | 45  | ns    |                                   |

| 54*          | * TccF CCP output fall time |                 | ime            | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |                             |                 |                | 16LF62X |                       | 25   | 45  | ns    |                                   |

TABLE 17-8: CAPTURE/COMPARE/PWM REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

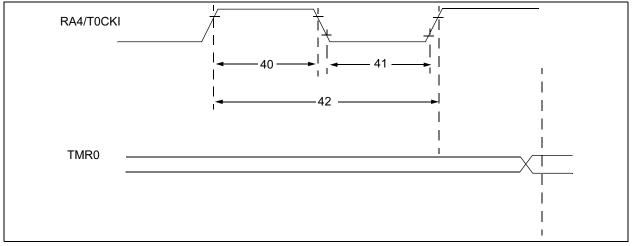

#### FIGURE 17-12: TIMER0 CLOCK TIMING

#### TABLE 17-9: TIMER0 CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Мах | Units | Conditions                            |

|--------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | —    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | _    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _    | _   | ns    | N = prescale value (1, 2,<br>4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

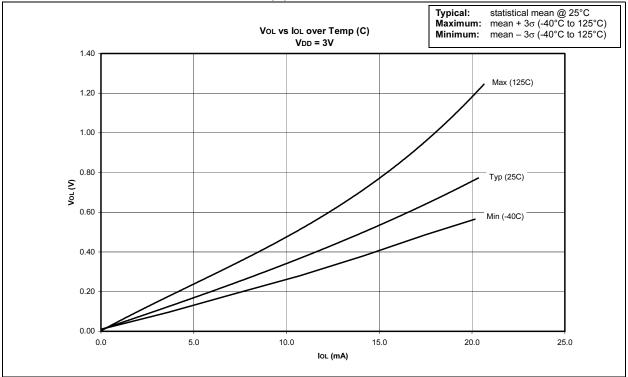

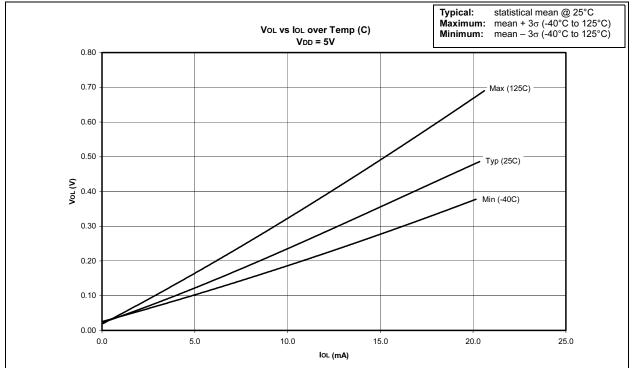

FIGURE 18-20: VOL VS IOL OVER TEMP (C) VDD = 5V