Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

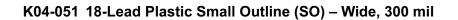

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627-20i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7      | Bit 6           | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0       | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|-----------------|-----------------|----------------|---------------|----------------|--------------|-------------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                 |                 |                |               |                |              |             |                                         |                    |

| 00h     | INDF    | Addressir  | ng this locatio | n uses conte    | nts of FSR to  | address data  | a memory (n    | ot a physica | l register) | xxxx xxxx                               | 25                 |

| 01h     | TMR0    | Timer0 M   | odule's Regis   | ter             |                |               |                |              | • /         | xxxx xxxx                               | 43                 |

| 02h     | PCL     | Program    | Counter's (PC   | ) Least Sign    | ificant Byte   |               |                |              |             | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP        | RP1             | RP0             | TO             | PD            | Z              | DC           | С           | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d | ata memory a    | ddress point    | er             |               |                |              | -           | xxxx xxxx                               | 25                 |

| 05h     | PORTA   | RA7        | RA6             | RA5             | RA4            | RA3           | RA2            | RA1          | RA0         | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7        | RB6             | RB5             | RB4            | RB3           | RB2            | RB1          | RB0         | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen   | nented          |                 |                |               |                |              |             | _                                       |                    |

| 08h     | _       | Unimplen   | nented          |                 |                |               |                |              |             | _                                       |                    |

| 09h     | _       | Unimplen   | nented          |                 |                |               |                |              |             | _                                       |                    |

| 0Ah     | PCLATH  | _          | _               | _               | Write buffer   | for upper 5 b | oits of progra | im counter   |             | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE        | PEIE            | T0IE            | INTE           | RBIE          | T0IF           | INTF         | RBIF        | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF       | CMIF            | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF       | TMR1IF      | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen   | nented          |                 |                |               |                |              |             | —                                       | _                  |

| 0Eh     | TMR1L   | Holding r  | egister for the | Least Signif    | icant Byte of  | the 16-bit TN | 1R1            |              |             | XXXX XXXX                               | 46                 |

| 0Fh     | TMR1H   | Holding r  | egister for the | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |              |             | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _          | _               | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS       | TMR10N      | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo    | odule's registe | r               |                |               |                |              |             | 0000 0000                               | 50                 |

| 12h     | T2CON   | _          | TOUTPS3         | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1      | T2CKPS0     | -000 0000                               | 50                 |

| 13h     | _       | Unimplen   | nented          |                 |                |               |                |              |             | _                                       | _                  |

| 14h     | —       | Unimplen   | nented          |                 |                |               |                |              |             | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0  | Compare/PWN     | /I register (LS | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0  | Compare/PWN     | /I register (M  | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _          | —               | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1       | CCP1M0      | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN       | RX9             | SREN            | CREN           | ADEN          | FERR           | OERR         | RX9D        | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T    | ransmit data    | register        |                |               |                |              |             | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART F    | Receive data r  | egister         |                |               |                |              |             | 0000 0000                               | 77                 |

| 1Bh     | _       | Unimplen   | nented          |                 |                |               |                |              |             | —                                       | _                  |

| 1Ch     | _       | Unimplen   | nented          |                 |                |               |                |              |             | —                                       | _                  |

| 1Dh     | —       | Unimplen   | nented          |                 |                |               |                |              |             | —                                       | —                  |

| 1Eh     | —       | Unimplen   | nented          |                 | 1              | 1             |                |              | 1           | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT      | C10UT           | C2INV           | C1INV          | CIS           | CM2            | CM1          | CM0         | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### 3.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |  |  |  |

|       | (PSA = 1). See Section 6.3.1              |  |  |  |  |  |  |  |  |

#### **REGISTER 3-2:** OPTION REGISTER (ADDRESS: 81h, 181h)

101

110 111

Legend:

R = Readable bit

-n = Value at POR

1:64

1:128

1:256

|         |                  |                                                                                                                             | UBBILL                    | <i></i> ,,         | ,,                         |       |       |       |  |  |  |  |  |  |  |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|----------------------------|-------|-------|-------|--|--|--|--|--|--|--|

|         | R/W-1            | R/W-1                                                                                                                       | R/W-1                     | R/W-1              | R/W-1                      | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |  |  |  |

|         | RBPU             | INTEDG                                                                                                                      | TOCS                      | TOSE               | PSA                        | PS2   | PS1   | PS0   |  |  |  |  |  |  |  |

|         | bit 7            | bit 7 bit                                                                                                                   |                           |                    |                            |       |       |       |  |  |  |  |  |  |  |

| bit 7   | <b>RBPU</b> : PO | RBPU: PORTB Pull-up Enable bit                                                                                              |                           |                    |                            |       |       |       |  |  |  |  |  |  |  |

|         | 1 = PORTE        | <ul> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |                           |                    |                            |       |       |       |  |  |  |  |  |  |  |

| bit 6   | INTEDG: In       | INTEDG: Interrupt Edge Select bit                                                                                           |                           |                    |                            |       |       |       |  |  |  |  |  |  |  |

|         |                  | <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul>       |                           |                    |                            |       |       |       |  |  |  |  |  |  |  |

| bit 5   | TOCS: TM         | R0 Clock Sc                                                                                                                 | ource Selec               | t bit              |                            |       |       |       |  |  |  |  |  |  |  |

|         |                  | ion on RA4/<br>I instruction                                                                                                |                           | (CLKOUT)           |                            |       |       |       |  |  |  |  |  |  |  |

| bit 4   | TOSE: TMF        | R0 Source E                                                                                                                 | Edge Select               | bit                |                            |       |       |       |  |  |  |  |  |  |  |

|         |                  | -                                                                                                                           |                           |                    | 4/T0CKI pin<br>4/T0CKI pin |       |       |       |  |  |  |  |  |  |  |

| bit 3   | PSA: Pres        | caler Assigr                                                                                                                | ment bit                  |                    |                            |       |       |       |  |  |  |  |  |  |  |

|         |                  | ller is assigr<br>ller is assigr                                                                                            |                           | /DT<br>imer0 modu  | le                         |       |       |       |  |  |  |  |  |  |  |

| bit 2-0 | PS2:PS0:         | Prescaler R                                                                                                                 | ate Select k              | oits               |                            |       |       |       |  |  |  |  |  |  |  |

|         | E                | Bit Value T                                                                                                                 | MR0 Rate                  | WDT Rate           |                            |       |       |       |  |  |  |  |  |  |  |

|         | -                | 000<br>001                                                                                                                  | 1:2<br>1:4                | 1:1<br>1:2         |                            |       |       |       |  |  |  |  |  |  |  |

|         |                  | 010<br>011<br>100                                                                                                           | 1 : 8<br>1 : 16<br>1 : 32 | 1:4<br>1:8<br>1:16 |                            |       |       |       |  |  |  |  |  |  |  |

1:32 1:64

1:128

W = Writable bit

'1' = Bit is set

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### 3.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 3.2.2.4 and Section 3.2.2.5 for a description of the comparator enable and flag bits.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 3-3: | 3: INTCON REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh) |                               |               |            |                          |              |               |       |  |  |  |  |  |

|---------------|----------------------------------------------------|-------------------------------|---------------|------------|--------------------------|--------------|---------------|-------|--|--|--|--|--|

|               | R/W-0                                              | R/W-0                         | R/W-0         | R/W-0      | R/W-0                    | R/W-0        | R/W-0         | R/W-x |  |  |  |  |  |

|               | GIE                                                | PEIE                          | T0IE          | INTE       | RBIE                     | T0IF         | INTF          | RBIF  |  |  |  |  |  |

|               | bit 7 bi                                           |                               |               |            |                          |              |               |       |  |  |  |  |  |

| bit 7         | GIE: Globa                                         | al Interrupt E                | nable bit     |            |                          |              |               |       |  |  |  |  |  |

|               |                                                    | s all unmas<br>es all interru | •             | ots        |                          |              |               |       |  |  |  |  |  |

| bit 6         | PEIE: Peri                                         | oheral Interr                 | upt Enable    | bit        |                          |              |               |       |  |  |  |  |  |

|               |                                                    | s all unmas<br>es all periph  |               |            | S                        |              |               |       |  |  |  |  |  |

| bit 5         | TOIE: TMR                                          | 0 Overflow                    | Interrupt En  | able bit   |                          |              |               |       |  |  |  |  |  |

|               |                                                    | s the TMR0<br>es the TMR0     |               |            |                          |              |               |       |  |  |  |  |  |

| bit 4         | INTE: RB0                                          | /INT Externa                  | al Interrupt  | Enable bit |                          |              |               |       |  |  |  |  |  |

|               |                                                    | s the RB0/II<br>es the RB0/I  |               |            |                          |              |               |       |  |  |  |  |  |

| bit 3         | RBIE: RB I                                         | Port Change                   | e Interrupt E | nable bit  |                          |              |               |       |  |  |  |  |  |

|               |                                                    | s the RB po<br>es the RB po   |               |            |                          |              |               |       |  |  |  |  |  |

| bit 2         | TOIF: TMR                                          | 0 Overflow                    | nterrupt Fla  | ag bit     |                          |              |               |       |  |  |  |  |  |

|               |                                                    | register has<br>register did  |               |            | eared in softwa          | are)         |               |       |  |  |  |  |  |

| bit 1         | INTF: RB0                                          | /INT Externa                  | al Interrupt  | Flag bit   |                          |              |               |       |  |  |  |  |  |

|               |                                                    | 30/INT exter<br>30/INT exter  |               | •          | must be cleare           | d in softwaı | e)            |       |  |  |  |  |  |

| bit 0         | RBIF: RB I                                         | Port Change                   | Interrupt F   | lag bit    |                          |              |               |       |  |  |  |  |  |

|               |                                                    | at least one<br>of the RB7:R  |               |            | nanged state (n<br>state | nust be clea | ared in softw | vare) |  |  |  |  |  |

|               | Levendu                                            |                               |               |            |                          |              |               | 1     |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 3.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Detect.

Note: BOD is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOD is cleared, indicating a brown-out has occurred. The BOD STATUS bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### REGISTER 3-6: PCON REGISTER (ADDRESS: 0Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | —   | —   | —   | OSCF  | _   | POR   | BOD   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTRC/ER oscillator frequency

- 1 = 4 MHz typical<sup>(1)</sup>

- 0 = 37 KHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect STATUS bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

- **Note 1:** When in ER Oscillator mode, setting OSCF = 1 will cause the oscillator frequency to change to the frequency specified by the external resistor.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 9.6 Comparator Interrupts

The Comparator Interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the Comparator Interrupt Flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a                                 | change                                     | in  | the   | CMCON   | register |  |  |  |  |  |  |  |

|-------|--------------------------------------|--------------------------------------------|-----|-------|---------|----------|--|--|--|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a |                                            |     |       |         |          |  |  |  |  |  |  |  |

|       | read                                 | read operation is being executed (start of |     |       |         |          |  |  |  |  |  |  |  |

|       | the C                                | the Q2 cycle), then the CMIF (PIR1<6>)     |     |       |         |          |  |  |  |  |  |  |  |

|       | interr                               | upt flag m                                 | nay | not g | et set. |          |  |  |  |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 9.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes-up from SLEEP, the contents of the CMCON register are not affected.

# 9.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the Comparator module to be in the comparator RESET mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 9.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A source impedance of maximum 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

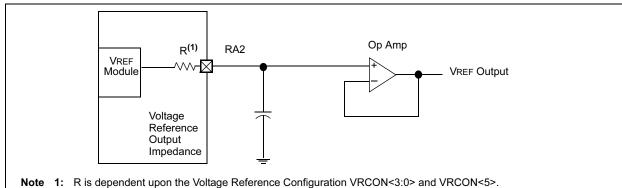

#### 10.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

#### 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

## 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

#### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

## 12.0 UNIVERSAL SYNCHRONOUS/ ASYNCHRONOUS RECEIVER/ TRANSMITTER (USART) MODULE

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/ A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISB<2:1>, have to be set in order to configure pins RB2/TX/CK and RB1/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

## REGISTER 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

|       | R/W-0                                               | R/W-0                                            | R/W-0                         | R/W-0           | U-0          | <b>R</b> /W-0 | R-1            | ,<br>R/W-0 |

|-------|-----------------------------------------------------|--------------------------------------------------|-------------------------------|-----------------|--------------|---------------|----------------|------------|

|       | CSRC                                                | TX9                                              | TXEN                          | SYNC            | —            | BRGH          | TRMT           | TX9D       |

|       | bit 7                                               |                                                  |                               |                 |              |               |                | bit 0      |

| bit 7 | CSRC: Cloc                                          | k Source Sel                                     | ect bit                       |                 |              |               |                |            |

|       | Asynchronou<br>Don't car                            |                                                  |                               |                 |              |               |                |            |

|       |                                                     | er mode (Clo                                     | ck generated<br>k from extern | internally from | m BRG)       |               |                |            |

| bit 6 | 1 = Selects 9                                       | ansmit Enabl<br>9-bit transmis<br>3-bit transmis | sion                          |                 |              |               |                |            |

| bit 5 | <b>TXEN</b> : Trans<br>1 = Transmit<br>0 = Transmit |                                                  | <sub>oit</sub> (1)            |                 |              |               |                |            |

| bit 4 | SYNC: USA<br>1 = Synchro<br>0 = Asynchro            |                                                  | ect bit                       |                 |              |               |                |            |

| bit 3 | Unimpleme                                           | nted: Read a                                     | is '0'                        |                 |              |               |                |            |

| bit 2 | BRGH: High                                          | Baud Rate S                                      | Select bit                    |                 |              |               |                |            |

|       | Asynchronou<br>1 = High s<br>0 = Low s              | speed                                            |                               |                 |              |               |                |            |

|       | <u>Synchronou</u>                                   | •                                                |                               |                 |              |               |                |            |

| bit 1 | <b>TRMT</b> : Trans<br>1 = TSR em<br>0 = TSR full   |                                                  | gister STATU                  | S bit           |              |               |                |            |

| bit 0 | <b>TX9D</b> : 9th bi                                | t of transmit                                    | data. Can be                  | PARITY bit.     |              |               |                |            |

|       | Note 1: S                                           | REN/CREN                                         | overrides TX                  | EN in SYNC      | node.        |               |                |            |

|       | Legend:                                             |                                                  |                               |                 |              |               |                |            |

|       | R = Reada                                           | ble bit                                          | VV = V                        | Vritable bit    | U = Unimp    | lemented b    | oit, read as ' | )'         |

|       | -n = Value                                          | at POR                                           | '1' = E                       | Bit is set      | '0' = Bit is | cleared       | x = Bit is ur  | nknown     |

| BAUD     | Fosc = 20 M | lHz    | SPBRG              | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          |        | _                  | NA     |        | _                  | NA     |        | _                  |

| 1.2      | NA          | _      | —                  | NA     | _      |                    | NA     | —      |                    |

| 2.4      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| 9.6      | NA          | _      | _                  | NA     | _      | _                  | 9.766  | +1.73% | 255                |

| 19.2     | 19.53       | +1.73% | 255                | 19.23  | +0.16% | 207                | 19.23  | +0.16% | 129                |

| 76.8     | 76.92       | +0.16% | 64                 | 76.92  | +0.16% | 51                 | 75.76  | -1.36% | 32                 |

| 96       | 96.15       | +0.16% | 51                 | 95.24  | -0.79% | 41                 | 96.15  | +0.16% | 25                 |

| 300      | 294.1       | -1.96  | 16                 | 307.69 | +2.56% | 12                 | 312.5  | +4.17% | 7                  |

| 500      | 500         | 0      | 9                  | 500    | 0      | 7                  | 500    | 0      | 4                  |

| HIGH     | 5000        | _      | 0                  | 4000   | _      | 0                  | 2500   | _      | 0                  |

| LOW      | 19.53       | _      | 255                | 15.625 | _      | 255                | 9.766  | _      | 255                |

#### TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|-------------|---------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 1.2      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 2.4      | NA          |         |                    | NA         | _      |                    | NA     |        | _                  |

| 9.6      | 9.622       | +0.23%  | 185                | 9.6        | 0      | 131                | 9.615  | +0.16% | 103                |

| 19.2     | 19.24       | +0.23%  | 92                 | 19.2       | 0      | 65                 | 19.231 | +0.16% | 51                 |

| 76.8     | 77.82       | +1.32   | 22                 | 79.2       | +3.13% | 15                 | 75.923 | +0.16% | 12                 |

| 96       | 94.20       | -1.88   | 18                 | 97.48      | +1.54% | 12                 | 1000   | +4.17% | 9                  |

| 300      | 298.3       | -0.57   | 5                  | 316.8      | 5.60%  | 3                  | NA     |        | —                  |

| 500      | NA          | _       | _                  | NA         |        | _                  | NA     | _      | _                  |

| HIGH     | 1789.8      |         | 0                  | 1267       | _      | 0                  | 100    | _      | 0                  |

| LOW      | 6.991       |         | 255                | 4.950      | _      | 255                | 3.906  | _      | 255                |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |        | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|--------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) |

| 0.3         | NA           |          | _                  | NA     |        |                    | 0.303      | +1.14% | 26                 |

| 1.2         | NA           | —        | —                  | 1.202  | +0.16% | 207                | 1.170      | -2.48% | 6                  |

| 2.4         | NA           | _        | _                  | 2.404  | +0.16% | 103                | NA         | _      | _                  |

| 9.6         | 9.622        | +0.23%   | 92                 | 9.615  | +0.16% | 25                 | NA         | _      | _                  |

| 19.2        | 19.04        | -0.83%   | 46                 | 19.24  | +0.16% | 12                 | NA         | _      | —                  |

| 76.8        | 74.57        | -2.90%   | 11                 | 83.34  | +8.51% | 2                  | NA         | —      | _                  |

| 96          | 99.43        | +3.57%   | 8                  | NA     |        | _                  | NA         | _      | —                  |

| 300         | 298.3        | 0.57%    | 2                  | NA     | _      | _                  | NA         | _      | _                  |

| 500         | NA           | _        | —                  | NA     |        |                    |            | —      | —                  |

| HIGH        | 894.9        | _        | 0                  | 250    |        | 0                  | 8.192      | _      | 0                  |

| LOW         | 3.496        | _        | 255                | 0.9766 |        | 255                | 0.032      | _      | 255                |

#### 14.2.6 INTERNAL 4 MHz OSCILLATOR

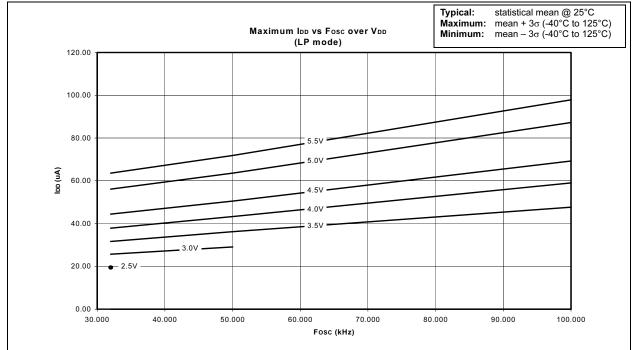

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and 25°C, see "Electrical Specifications" section for information on variation over voltage and temperature.

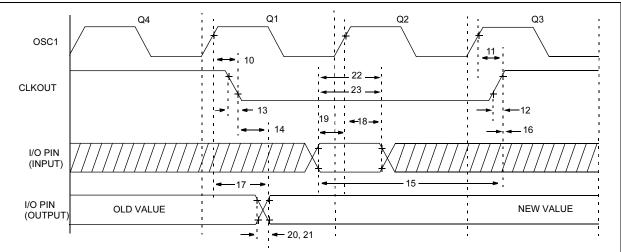

#### 14.2.7 CLKOUT

The PIC16F62X can be configured to provide a clock out signal by programming the configuration word. The oscillator frequency, divided by 4 can be used for test purposes or to synchronize other logic.

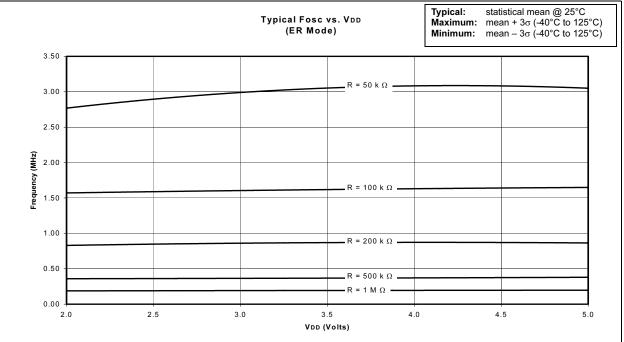

#### 14.3 Special Feature: Dual Speed Oscillator Modes

A software programmable Dual Speed Oscillator mode is provided when the PIC16F62X is configured in either ER or INTRC Oscillator modes. This feature allows users to dynamically toggle the oscillator speed between 4 MHz and 37 kHz. In ER mode, the 4 MHz setting will vary depending on the value of the external resistor. Also in ER mode, the 37 kHz operation is fixed and does not vary with resistor value. Applications that require low current power savings, but cannot tolerate putting the part into SLEEP, may use this mode.

The OSCF bit in the PCON register is used to control Dual Speed mode. See Section 3.2.2.6, Register 3-4.

#### 14.4 RESET

The PIC16F62X differentiates between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) WDT Reset (normal operation)

- e) WDT Wake-up (SLEEP)

- f) Brown-out Detect (BOD)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, MCLR Reset, WDT Reset and MCLR Reset during SLEEP. They are not affected by a WDT Wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 14-5. These bits are used in software to determine the nature of the RESET. See Table 14-8 for a full description of RESET states of all registers.

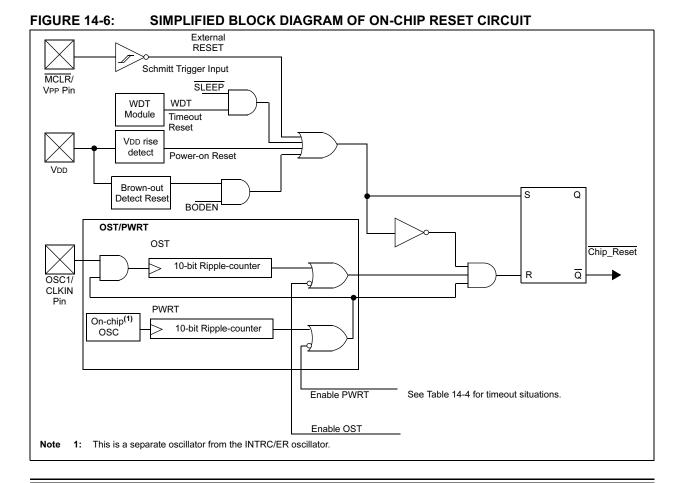

A simplified block diagram of the on-chip RESET circuit is shown in Figure 14-6.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 17-6 for pulse width specification.

#### TABLE 14-7: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | 1-uu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 1-uu             |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-uu             |

| Brown-out Detect Reset             | 000h                  | 000x xuuu          | 1-u0             |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note** 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on<br>Reset | <ul> <li>MCLR Reset during normal<br/>operation</li> <li>MCLR Reset during SLEEP</li> <li>WDT Reset</li> <li>Brown-out Detect Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP through<br/>interrupt</li> <li>Wake-up from SLEEP through<br/>WDT timeout</li> </ul> |

|----------|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| W        |         | xxxx xxxx         | սսսս սսսս                                                                                                                                                     | սսսս սսսս                                                                                                        |

| INDF     | 00h     | _                 | -                                                                                                                                                             | -                                                                                                                |

| TMR0     | 01h     | xxxx xxxx         | uuuu uuuu                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PCL      | 02h     | 0000 0000         | 0000 0000                                                                                                                                                     | PC + 1 <sup>(3)</sup>                                                                                            |

| STATUS   | 03h     | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                                                                                                                      | uuuq quuu <sup>(4)</sup>                                                                                         |

| FSR      | 04h     | xxxx xxxx         | սսսս սսսս                                                                                                                                                     | uuuu uuuu                                                                                                        |

| PORTA    | 05h     | xxxx 0000         | xxxx u000                                                                                                                                                     | xxxx 0000                                                                                                        |

| PORTB    | 06h     | xxxx xxxx         | uuuu uuuu                                                                                                                                                     | <u>uuuu</u> uuuu                                                                                                 |

| T1CON    | 10h     | 00 0000           | uu uuuu                                                                                                                                                       | uu uuuu                                                                                                          |

| T2CON    | 12h     | -000 0000         | -000 0000                                                                                                                                                     | -uuu uuuu                                                                                                        |

| CCP1CON  | 17h     | 00 0000           | 00 0000                                                                                                                                                       | uu uuuu                                                                                                          |

| RCSTA    | 18h     | 0000 -00x         | 0000 -00x                                                                                                                                                     | uuuu -uuu                                                                                                        |

| CMCON    | 1Fh     | 0000 0000         | 0000 0000                                                                                                                                                     | uu uuuu                                                                                                          |

| PCLATH   | 0Ah     | 0 0000            | 0 0000                                                                                                                                                        | u uuuu                                                                                                           |

| INTCON   | 0Bh     | 0000 000x         | 0000 000u                                                                                                                                                     | uuuu uqqq <sup>(2)</sup>                                                                                         |

| PIR1     | 0Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | -q (2,5)                                                                                                         |

| OPTION   | 81h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| TRISA    | 85h     | 11-1 1111         | 11 1111                                                                                                                                                       | uu-u uuuu                                                                                                        |

| TRISB    | 86h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PIE1     | 8Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | uuuu -uuu                                                                                                        |

| PCON     | 8Eh     | 1-0x              | 1-uq <sup>(1,6)</sup>                                                                                                                                         | uu                                                                                                               |

| TXSTA    | 98h     | 0000 -010         | 0000 -010                                                                                                                                                     | uuuu -uuu                                                                                                        |

| EECON1   | 9Ch     | x000              | q000                                                                                                                                                          | uuuu                                                                                                             |

| VRCON    | 9Fh     | 000- 0000         | 000- 0000                                                                                                                                                     | սսս- սսսս                                                                                                        |

TABLE 14-8:

INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**4**: See Table 14-7 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then Bit 6 = 1. All other interrupts generating a wake-up will cause Bit 6 = u.

6: If RESET was due to brown-out, then Bit 0 = 0. All other RESETS will cause Bit 0 = u.

# PIC16F62X

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test f, Skip if Clear                                                            |

|------------------|---------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             | Syntax:          | [ <i>label</i> ]BTFSC f,b                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                  |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                              |

| Status Affected: | None                                                                | Status Affected: | None                                                                                 |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                                    |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0' then the                                           |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0' then the next                      |

| Cycles:          | 1                                                                   |                  | instruction fetched during the                                                       |

| Example          | BCF REG1, 7                                                         |                  | current instruction execution is                                                     |

|                  | Before Instruction<br>REG1 = 0xC7<br>After Instruction              |                  | discarded, and a NOP is executed<br>instead, making this a two-cycle<br>instruction. |

|                  | REG1 = 0x47                                                         | Words:           | 1                                                                                    |

|                  |                                                                     | Cycles:          | 1 <sup>(2)</sup>                                                                     |

| BSF              | Bit Set f                                                           | Example          | HERE BTFSC REG1<br>FALSE GOTO PROCESS_CODE                                           |

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |                  | TRUE •                                                                               |

| Operands:        | $0 \le f \le 127$                                                   |                  | •                                                                                    |

|                  | $0 \le b \le 7$                                                     |                  | Before Instruction                                                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | PC = address HERE<br>After Instruction                                               |

| Status Affected: | None                                                                |                  | if REG<1> = 0,                                                                       |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | PC = address TRUE                                                                    |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | if REG<1>=1,                                                                         |

| Words:           | 1                                                                   |                  | PC = address FALSE                                                                   |

| Cycles:          | 1                                                                   |                  |                                                                                      |

Example

BSF

REG1, 7

REG1 = 0x0A

REG1 = 0x8A

Before Instruction

After Instruction

# PIC16F62X

| CLRW             | Clear W                                                               |                                       |           |       |   | COMF   |

|------------------|-----------------------------------------------------------------------|---------------------------------------|-----------|-------|---|--------|

| Syntax:          | [ label ]                                                             | CLRW                                  |           |       | I | Syntax |

| Operands:        | None                                                                  |                                       |           |       |   | Opera  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (V) \\ 1 \rightarrow Z \end{array}$ | W)                                    |           |       |   | Operat |

| Status Affected: | Z                                                                     |                                       |           |       |   | Status |

| Encoding:        | 00                                                                    | 0001                                  | 0000      | 0011  |   | Encod  |

| Description:     | W regist<br>(Z) is set                                                |                                       | ared. Zer | o bit | I | Descri |

| Words:           | 1                                                                     |                                       |           |       |   |        |

| Cycles:          | 1                                                                     |                                       |           |       |   |        |

| Example          | CLRW                                                                  |                                       |           |       |   | Words  |

|                  | Before In                                                             |                                       |           |       |   | Cycles |

|                  | After Ins<br>V                                                        | V = 0x<br>truction<br>V = 0x<br>Z = 1 |           |       |   | Examp  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                       |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                      |  |  |  |  |

| Status Affected: | Z                                                                                                                                                        |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                        |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the<br>result is stored in W. If 'd' is 1 the<br>result is stored back in register<br>'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |

| Example          | COMF REG1, 0                                                                                                                                             |  |  |  |  |

|                  | Before Instruction<br>REG1 = 0x13<br>After Instruction<br>REG1 = 0x13<br>W = 0xEC                                                                        |  |  |  |  |

| CLRWDT                    | Clear Watchdog Timer                                                                                                                    | DECF                                    | Decrement f                                                                                                                                 |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                   | [label] CLRWDT                                                                                                                          | Syntax:                                 | [ <i>label</i> ] DECF f,d                                                                                                                   |  |  |

| Operands:                 | None                                                                                                                                    | Operands:                               | $0 \leq f \leq 127$                                                                                                                         |  |  |

| Operation:                | $00h \rightarrow WDT$                                                                                                                   |                                         | d ∈ [0,1]                                                                                                                                   |  |  |

|                           | $0 \rightarrow \frac{\text{WDT}}{\text{TO}}$ prescaler,                                                                                 | Operation: (f) - 1 $\rightarrow$ (dest) |                                                                                                                                             |  |  |

|                           | $1 \rightarrow TO$<br>$1 \rightarrow PD$                                                                                                | Status Affected:                        | Z                                                                                                                                           |  |  |

| Status Affected:          | TO, PD                                                                                                                                  | Encoding:                               | 00 0011 dfff ffff                                                                                                                           |  |  |

| Encoding:<br>Description: | 00000001100100CLRWDT instruction resets the<br>Watchdog Timer. It also resets                                                           | Description:                            | Decrement register 'f'. If 'd' is 0<br>the result is stored in the W<br>register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |

|                           | the prescaler of the WDT.<br>STATUS bits TO and PD are set.                                                                             | Words:                                  | 1                                                                                                                                           |  |  |

| Words:                    | 1                                                                                                                                       | Cycles:                                 | 1                                                                                                                                           |  |  |

| Cycles:                   | 1                                                                                                                                       | Example                                 | DECF CNT, 1                                                                                                                                 |  |  |

| Example                   | CLRWDT<br>Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = 1<br>PD = 1 |                                         | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                       |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                        |   |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |   |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |   |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |   |  |  |  |  |

| Status Affected: | Z                                                                                                                  |   |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkk                                                                                                   | k |  |  |  |  |

| Description:     | The contents of the W register<br>OR'ed with the eight bit literal '<br>The result is placed in the W<br>register. |   |  |  |  |  |

| Words:           | 1                                                                                                                  |   |  |  |  |  |

| Cycles:          | 1                                                                                                                  |   |  |  |  |  |

| Example          | IORLW 0x35                                                                                                         |   |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 0                                           |   |  |  |  |  |

| MOVLW            | Move L              | iteral to           | w                                  |      |  |  |  |

|------------------|---------------------|---------------------|------------------------------------|------|--|--|--|

| Syntax:          | [ label ]           | MOVL                | Wk                                 |      |  |  |  |

| Operands:        | $0 \le k \le 255$   |                     |                                    |      |  |  |  |

| Operation:       | $k \rightarrow (W)$ |                     |                                    |      |  |  |  |

| Status Affected: | None                |                     |                                    |      |  |  |  |

| Encoding:        | 11                  | 00xx                | kkkk                               | kkkk |  |  |  |

| Description:     | into W r            |                     | ral 'k' is lo<br>The don't<br>0's. |      |  |  |  |

| Words:           | 1                   |                     |                                    |      |  |  |  |

| Cycles:          | 1                   |                     |                                    |      |  |  |  |

| Example          | MOVLW               | 0x5A                |                                    |      |  |  |  |

|                  |                     | struction<br>= 0x5/ | 4                                  |      |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                     |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                     |

| Status Affected: | Z                                                                                                                                                                     |