Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 × 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

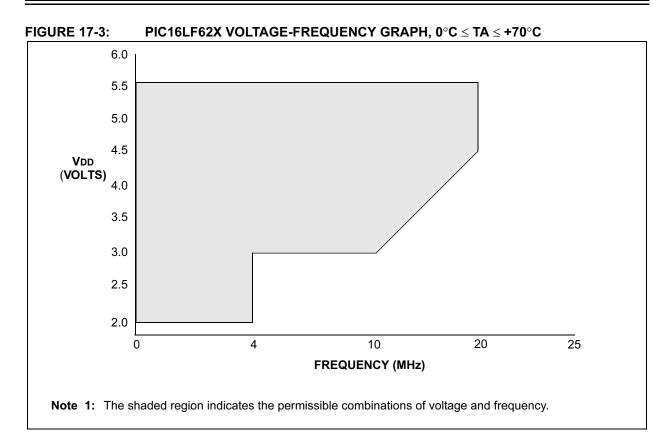

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name   | Bit 7               | Bit 6           | Bit 5       | Bit 4         | Bit 3        | Bit 2         | Bit 1         | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|---------------------|-----------------|-------------|---------------|--------------|---------------|---------------|---------|-----------------------------------------|--------------------|

| Bank 1  |        |                     |                 |             |               |              |               |               |         |                                         |                    |

| 80h     | INDF   | Addressin register) | g this locatior | n uses cont | ents of FSF   | to address   | s data memo   | ory (not a ph | nysical | XXXX XXXX                               | 25                 |

| 81h     | OPTION | RBPU                | INTEDG          | TOCS        | T0SE          | PSA          | PS2           | PS1           | PS0     | 1111 1111                               | 20                 |

| 82h     | PCL    | Program (           | Counter's (PC   | ) Least Sig | nificant Byte | e            |               |               |         | 0000 0000                               | 25                 |

| 83h     | STATUS | IRP                 | RP1             | RP0         | TO            | PD           | Z             | DC            | С       | 0001 1xxx                               | 19                 |

| 84h     | FSR    | Indirect da         | ata memory a    | ddress poir | nter          |              |               |               |         | xxxx xxxx                               | 25                 |

| 85h     | TRISA  | TRISA7              | TRISA6          | TRISA5      | TRISA4        | TRISA3       | TRISA2        | TRISA1        | TRISA0  | 1111 1111                               | 29                 |

| 86h     | TRISB  | TRISB7              | TRISB6          | TRISB5      | TRISB4        | TRISB3       | TRISB2        | TRISB1        | TRISB0  | 1111 1111                               | 34                 |

| 87h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 88h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       |                    |

| 89h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 8Ah     | PCLATH | _                   | _               | _           | Write buffe   | er for upper | 5 bits of pro | ogram count   | ter     | 0 0000                                  | 25                 |

| 8Bh     | INTCON | GIE                 | PEIE            | T0IE        | INTE          | RBIE         | TOIF          | INTF          | RBIF    | 0000 000x                               | 21                 |

| 8Ch     | PIE1   | EEIE                | CMIE            | RCIE        | TXIE          | _            | CCP1IE        | TMR2IE        | TMR1IE  | 0000 -000                               | 22                 |

| 8Dh     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 8Eh     | PCON   | _                   | _               | _           | _             | OSCF         | _             | POR           | BOD     | 1-0x                                    | 24                 |

| 8Fh     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 90h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       |                    |

| 91h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 92h     | PR2    | Timer2 Pe           | eriod Register  |             |               |              |               |               |         | 1111 1111                               | 50                 |

| 93h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 94h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 95h     | _      | Unimplem            | ented           |             |               |              |               |               |         | —                                       | _                  |

| 96h     |        | Unimplem            | ented           |             |               |              |               |               |         | —                                       | —                  |

| 97h     |        | Unimplem            | ented           |             |               |              |               |               |         | —                                       | —                  |

| 98h     | TXSTA  | CSRC                | TX9             | TXEN        | SYNC          |              | BRGH          | TRMT          | TX9D    | 0000 -010                               | 69                 |

| 99h     | SPBRG  | Baud Rate           | e Generator F   | Register    |               |              |               |               |         | 0000 0000                               | 69                 |

| 9Ah     | EEDATA | EEPROM              | data register   |             |               |              |               |               |         | xxxx xxxx                               | 87                 |

| 9Bh     | EEADR  | _                   | EEPROM a        | ddress regi | ster          |              |               | -             |         | xxxx xxxx                               | 87                 |

| 9Ch     | EECON1 | _                   | —               | _           | _             | WRERR        | WREN          | WR            | RD      | x000                                    | 87                 |

| 9Dh     | EECON2 | EEPROM              | control regist  | er 2 (not a | physical reg  | gister)      |               |               |         |                                         | 87                 |

| 9Eh     | —      | Unimplem            | 1               |             |               |              |               |               |         | _                                       | _                  |

| 9Fh     | VRCON  | VREN                | VROE            | VRR         | —             | VR3          | VR2           | VR1           | VR0     | 000- 0000                               | 59                 |

| <b>TABLE 3-2:</b> | SPECIAL FUNCTION REGISTERS SUMMARY BANK 1 |

|-------------------|-------------------------------------------|

|                   |                                           |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### 3.2.2.1 STATUS Register

The STATUS register, shown in Register 3-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory (SRAM).

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect any STATUS bit. For other instructions, not affecting any STATUS bits, see the "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

|         | R/W-0                                                                                                                                                                                                                                                                                                             | R/W-0                                      | R/W-0        | R-1                        | R-1                                             | R/W-x | R/W-x                          | R/W-x        |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|----------------------------|-------------------------------------------------|-------|--------------------------------|--------------|--|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                                                                               | RP1                                        | RP0          | TO                         | PD                                              | Z     | DC                             | С            |  |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                             |                                            |              |                            |                                                 |       |                                | bit 0        |  |  |  |  |  |

| bit 7   | <b>IRP</b> : Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                  |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

| bit 6-5 | <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h - 7Fh)<br>01 = Bank 1 (80h - FFh)<br>10 = Bank 2 (100h - 17Fh)<br><u>11</u> = Bank 3 (180h - 1FFh)                                                                                                                    |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

| bit 4   | TO: Timeout bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT timeout occurred                                                                                                                                                                                                     |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

| bit 3   |                                                                                                                                                                                                                                                                                                                   | -down bit<br>ower-up or t<br>cution of the | •            |                            | on                                              |       |                                |              |  |  |  |  |  |

| bit 2   |                                                                                                                                                                                                                                                                                                                   | sult of an ari<br>sult of an ari           |              | • •                        | on is zero<br>on is not zero                    |       |                                |              |  |  |  |  |  |

| bit 1   | is reversed<br>1 = A carry                                                                                                                                                                                                                                                                                        | l)<br>/-out from th                        | e 4th low or | rder bit of th             | BLW, SUBWF ins<br>e result occurre<br>he result |       | for borrow t                   | the polarity |  |  |  |  |  |

| bit 0   | <ul> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

|         | <ul> <li>Note 1: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul>                                             |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                           |                                            |              |                            |                                                 |       |                                |              |  |  |  |  |  |

|         | R = Reada<br>-n = Value                                                                                                                                                                                                                                                                                           |                                            |              | Vritable bit<br>Bit is set | U = Unimple<br>'0' = Bit is c                   |       | it, read as '<br>x = Bit is ui |              |  |  |  |  |  |

### 3.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 3.2.2.4 and Section 3.2.2.5 for a description of the comparator enable and flag bits.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 3-3: INTCON REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh) |                                   |                               |               |            |                          |              |               |       |  |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------|-------------------------------|---------------|------------|--------------------------|--------------|---------------|-------|--|--|--|--|--|

|                                                               | R/W-0                             | R/W-0                         | R/W-0         | R/W-0      | R/W-0                    | R/W-0        | R/W-0         | R/W-x |  |  |  |  |  |

|                                                               | GIE PEIE TOIE INTE RBIE TOIF INTF |                               |               |            |                          |              |               |       |  |  |  |  |  |

|                                                               | bit 7                             |                               |               |            |                          |              |               |       |  |  |  |  |  |

| bit 7                                                         | GIE: Global Interrupt Enable bit  |                               |               |            |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | s all unmas<br>es all interru | •             | ots        |                          |              |               |       |  |  |  |  |  |

| bit 6                                                         | PEIE: Peri                        | oheral Interr                 | upt Enable    | bit        |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | s all unmas<br>es all periph  |               |            | S                        |              |               |       |  |  |  |  |  |

| bit 5                                                         | TOIE: TMR                         | 0 Overflow                    | Interrupt En  | able bit   |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | s the TMR0<br>es the TMR0     |               |            |                          |              |               |       |  |  |  |  |  |

| bit 4                                                         | INTE: RB0                         | /INT Externa                  | al Interrupt  | Enable bit |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | s the RB0/II<br>es the RB0/I  |               |            |                          |              |               |       |  |  |  |  |  |

| bit 3                                                         | RBIE: RB I                        | Port Change                   | e Interrupt E | nable bit  |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | s the RB po<br>es the RB po   |               |            |                          |              |               |       |  |  |  |  |  |

| bit 2                                                         | TOIF: TMR                         | 0 Overflow                    | nterrupt Fla  | ag bit     |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | register has<br>register did  |               |            | eared in softwa          | are)         |               |       |  |  |  |  |  |

| bit 1                                                         | INTF: RB0                         | /INT Externa                  | al Interrupt  | Flag bit   |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | 30/INT exter<br>30/INT exter  |               | •          | must be cleare           | d in softwaı | e)            |       |  |  |  |  |  |

| bit 0                                                         | RBIF: RB I                        | Port Change                   | Interrupt F   | lag bit    |                          |              |               |       |  |  |  |  |  |

|                                                               |                                   | at least one<br>of the RB7:R  |               |            | nanged state (n<br>state | nust be clea | ared in softw | vare) |  |  |  |  |  |

|                                                               | Levendu                           |                               |               |            |                          |              |               | 1     |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 3.2.2.4 PIE1 Register

This register contains interrupt enable bits.

| 51ER 3-4: | PIET REGISTER (ADDRESS: 8Ch)             |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

|-----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------|----------------|-----------|---------------|--------|--|--|--|--|--|

|           | R/W-0                                    | R/W-0                                                                                                                 | R/W-0         | R/W-0                           | U-0            | R/W-0     | R/W-0         | R/W-0  |  |  |  |  |  |

|           | EEIE                                     | CMIE                                                                                                                  | RCIE          | TXIE                            |                | CCP1IE    | TMR2IE        | TMR1IE |  |  |  |  |  |

|           | bit 7                                    |                                                                                                                       |               |                                 |                |           |               | bit 0  |  |  |  |  |  |

|           |                                          |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 7     |                                          | EEIE: EE Write Complete Interrupt Enable Bit                                                                          |               |                                 |                |           |               |        |  |  |  |  |  |

|           |                                          | <ul> <li>1 = Enables the EE write complete interrupt</li> <li>0 = Disables the EE write complete interrupt</li> </ul> |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 6     | CMIE: Com                                | parator Inte                                                                                                          | errupt Enab   | le bit                          |                |           |               |        |  |  |  |  |  |

|           |                                          | <ul> <li>1 = Enables the comparator interrupt</li> <li>0 = Disables the comparator interrupt</li> </ul>               |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 5     | RCIE: USA                                | RT Receive                                                                                                            | e Interrupt E | Enable bit                      |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables<br>0 = Disable               |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 4     | TXIE: USAF                               | RT Transmi                                                                                                            | t Interrupt E | Enable bit                      |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables<br>0 = Disable               |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 3     | Unimpleme                                | ented: Rea                                                                                                            | d as '0'      |                                 |                |           |               |        |  |  |  |  |  |

| bit 2     | CCP1IE: CO                               | CP1 Interru                                                                                                           | pt Enable b   | oit                             |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables<br>0 = Disable               |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 1     | TMR2IE: T                                | MR2 to PR2                                                                                                            | 2 Match Inte  | errupt Enable                   | e bit          |           |               |        |  |  |  |  |  |

|           |                                          |                                                                                                                       |               | itch interrupt<br>atch interrup |                |           |               |        |  |  |  |  |  |

| bit 0     | TMR1IE: T                                | MR1 Overfle                                                                                                           | ow Interrup   | t Enable bit                    |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables                              | s the TMR1                                                                                                            | overflow in   | nterrupt                        |                |           |               |        |  |  |  |  |  |

|           | 0 = Disables the TMR1 overflow interrupt |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

|           | Legend:                                  |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

|           | R = Readat                               | ole bit                                                                                                               | VV = V        | Vritable bit                    | U = Unimple    | emented b | it, read as ' | D'     |  |  |  |  |  |

|           | -n = Value a                             | at POR                                                                                                                | '1' = E       | Bit is set                      | '0' = Bit is c | leared    | x = Bit is ur | nknown |  |  |  |  |  |

## REGISTER 3-4: PIE1 REGISTER (ADDRESS: 8Ch)

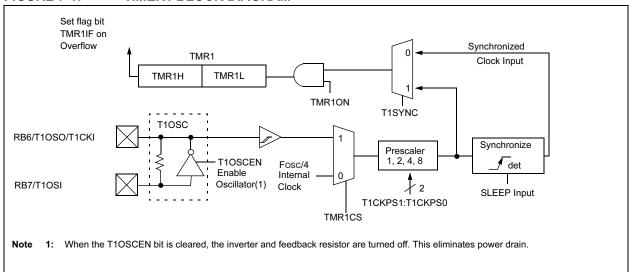

# 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

## 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

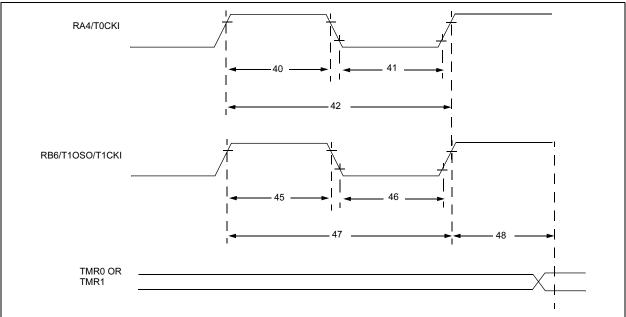

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

## FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

# 7.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq    | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

**Note 1:** These values are for design guidance only. Consult AN826 (DS00826A) for further information on Crystal/Capacitor Selection.

# 7.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |      |      |    |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|------|------|----|--|--|--|--|--|--|--|--|

|       | module will not set interrupt flag bit   |      |      |    |  |  |  |  |  |  |  |  |

|       | TMR1IF                                   | (PIR | 1<0> | ). |  |  |  |  |  |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

# 7.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other RESET except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

# 7.7 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7      | Bit 6                                                                      | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|------------|----------------------------------------------------------------------------|---------------|----------------|---------------|-------------|--------|--------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE        | PEIE                                                                       | TOIE          | INTE           | RBIE          | T0IF        | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF       | CMIF                                                                       | RCIF          | TXIF           | I             | CCP1IF      | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE       | CMIE                                                                       | RCIE          | TXIE           | I             | CCP1IE      | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 0Eh                   | TMR1L  | Holding re | egister for                                                                | the Least Sig | gnificant Byte | of the 16-bit | TMR1 regist | er     |        | xxxx xxxx       | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding re | Holding register for the Most Significant Byte of the 16-bit TMR1 register |               |                |               |             |        |        |                 | uuuu uuuu                       |

| 10h                   | T1CON  | _          | _                                                                          | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS | TMR10N | 00 0000         | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

| <b>REGISTER 8-1:</b> |                                                      |                            |             |             |           |        |         |         |  |  |  |  |  |  |

|----------------------|------------------------------------------------------|----------------------------|-------------|-------------|-----------|--------|---------|---------|--|--|--|--|--|--|

|                      | U-0                                                  | R/W-0                      | R/W-0       | R/W-0       | R/W-0     | R/W-0  | R/W-0   | R/W-0   |  |  |  |  |  |  |

|                      | _                                                    | TOUTPS3                    | TOUTPS2     | TOUTPS1     | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |  |  |  |  |

|                      | bit 7                                                |                            |             |             |           |        |         | bit 0   |  |  |  |  |  |  |

|                      |                                                      |                            |             |             |           |        |         |         |  |  |  |  |  |  |

| bit 7                | Unimplemented: Read as '0'                           |                            |             |             |           |        |         |         |  |  |  |  |  |  |

| bit 6-3              | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |                            |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | 0000 = 1:1                                           | 0000 = 1:1 Postscale Value |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | 0001 = 1:2                                           | 0001 = 1:2 Postscale Value |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | •                                                    |                            |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | •                                                    |                            |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | 1111 = 1:1                                           | 6 Postscale                |             |             |           |        |         |         |  |  |  |  |  |  |

|                      |                                                      |                            |             |             |           |        |         |         |  |  |  |  |  |  |

| bit 2                | TMR2ON:                                              | Timer2 On bi               | it          |             |           |        |         |         |  |  |  |  |  |  |

|                      | 1 = Timer2                                           | is on                      |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | 0 = Timer2                                           | is off                     |             |             |           |        |         |         |  |  |  |  |  |  |

| bit 1-0              | T2CKPS1:                                             | T2CKPS0: T                 | imer2 Clock | Prescale Se | lect bits |        |         |         |  |  |  |  |  |  |

|                      | 00 = 1:1 P                                           | rescaler Valu              | е           |             |           |        |         |         |  |  |  |  |  |  |

|                      |                                                      | rescaler Valu              | -           |             |           |        |         |         |  |  |  |  |  |  |

|                      | 1x = 1:16                                            | Prescaler Val              | ue          |             |           |        |         |         |  |  |  |  |  |  |

|                      | <b></b>                                              |                            |             |             |           |        |         |         |  |  |  |  |  |  |

|                      | Legend:                                              |                            |             |             |           |        |         |         |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

## TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|------------------------|----------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE                    | PEIE           | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF                   | CMIF           | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE                   | CMIE           | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r       |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Period Register |                |         |         |         |        |         |         |                 | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

## 10.2 Voltage Reference Accuracy/Error

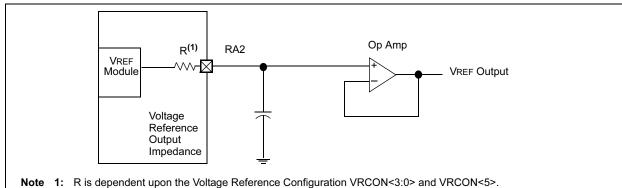

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

## 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

# 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

## **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

## FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

NOTES:

| BAUD     | Fosc = 20 M | Hz     |                    | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _      | _                  | NA     | _      |                    | NA     | _      | _                  |

| 1.2      | 1.221       | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404       | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2       | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5       | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5       | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221       | —      | 255                | 0.977  |        | 255                | 0.6104 |        | 255                |

| TABLE 12-4: | BAUD RATES FOR ASYNCHRONOUS MODE ( | BRGH=0) |

|-------------|------------------------------------|---------|

|-------------|------------------------------------|---------|

| BAUD     | Fosc = 7.15909 MHz |        | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|--------------------|--------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD              | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA                 | _      | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203              | +0.23% | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380              | -0.83% | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322              | -2.90% | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64              | -2.90% | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA                 | _      | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 500      | NA                 |        | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9              | _      | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437              | —      | 255                | 0.3094     |        | 255                | 3.906  |        | 255                |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |         | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3         | 0.301        | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2         | 1.190        | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4         | 2.432        | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6         | 9.322        | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2        | 18.64        | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8        | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96          | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH        | 55.93        | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW         | 0.2185       | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

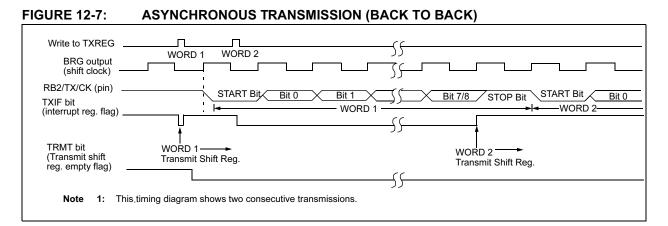

## TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                                 | Bit 7     | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|---------|--------------------------------------|-----------|----------|--------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                                 | EEIF      | CMIF     | RCIF   | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                                | SPEN      | RX9      | SREN   | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG                                | USART Tra | nsmit Re | gister |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                                 | EEIE      | CMIE     | RCIE   | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                                | CSRC      | TX9      | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | N SPBRG Baud Rate Generator Register |           |          |        |       |       |        |        |        |                 | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

## 12.3 USART Function

The USART function is similar to that on the PIC16C74B, which includes the BRGH = 1 fix.

#### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed so when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer. The ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if, and only, if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (='1'), all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = '1'). When ADEN is disabled (='0'), all data bytes are received and the 9th bit can be used as the PARITY bit.

The USART Receive Block Diagram is shown in Figure 12-8.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Steps to follow when setting up an Asynchronous or Synchronous Reception with Address Detect Enabled:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable asynchronous or synchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. Set bit RX9 to enable 9-bit reception.

- 5. Set ADEN to enable address detect.

- 6. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 9. If any error occurred, clear the error by clearing enable bit CREN if it was already set.

- If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name                               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR |      |      | e on<br>other<br>ETS |

|---------|------------------------------------|-------|-------|-------|-------|-------|--------|--------|--------|-----------------|------|------|----------------------|

| 0Ch     | PIR1                               | EEIF  | CMIF  | RCIF  | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF | 0000            | -000 | 0000 | -000                 |

| 18h     | RCSTA                              | SPEN  | RX9   | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000            | -00x | 0000 | -00x                 |

| 1Ah     | RCREG                              | RX7   | RX6   | RX5   | RX4   | RX3   | RX2    | RX1    | RX0    | 0000            | 0000 | 0000 | 0000                 |

| 8Ch     | PIE1                               | EEIE  | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000            | -000 | 0000 | -000                 |

| 98h     | TXSTA                              | CSRC  | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000            | -010 | 0000 | -010                 |

| 99h     | SPBRG Baud Rate Generator Register |       |       |       |       |       |        |        |        |                 | 0000 | 0000 | 0000                 |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

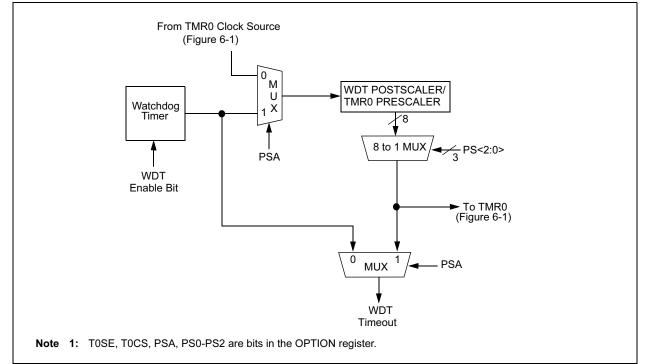

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-10: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name            | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|-----------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config.<br>bits | LVP   | BODEN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |

| 81h     | OPTION          | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: -= Unimplemented location, read as "0", + = Reserved for future use

**Note 1:** Shaded cells are not used by the Watchdog Timer.

#### 14.9 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | by a WDT timeout does not drive MCLR      |  |  |  |  |

|       | pin low.                                  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                    | CALL                      | Call Subroutine                                                                                                                                                                                                                |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                                                        | Syntax:                   | [ <i>label</i> ] CALL k                                                                                                                                                                                                        |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                                        | Operands:                 | $0 \leq k \leq 2047$                                                                                                                                                                                                           |  |  |

|                  | 0 ≤ b < 7                                                                                                                                                                                                                                  | Operation:                | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                                    |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                    |                           |                                                                                                                                                                                                                                |  |  |

| Status Affected: | None                                                                                                                                                                                                                                       | Status Affected:          | None                                                                                                                                                                                                                           |  |  |

| Encoding:        | 01 11bb bfff                                                                                                                                                                                                                               | TITI Croading             | 10 0kkk kkkk kkkk                                                                                                                                                                                                              |  |  |

| Description:     | If bit 'b' in register 'f' is '1'<br>next instruction is skipped<br>If bit 'b' is '1', then the nex<br>instruction fetched during<br>current instruction execut<br>discarded and a NOP is ex<br>instead, making this a two<br>instruction. | the<br>ion, is<br>xecuted | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven bit<br>immediate address is loaded<br>into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle |  |  |

| Words:           | 1                                                                                                                                                                                                                                          |                           | instruction.                                                                                                                                                                                                                   |  |  |

| Cycles:          | 1 <sup>(2)</sup>                                                                                                                                                                                                                           | Words:                    | 1                                                                                                                                                                                                                              |  |  |

| Example          | HERE BTFSS REG1                                                                                                                                                                                                                            | Cycles:                   | 2                                                                                                                                                                                                                              |  |  |

|                  | FALSE GOTO PROCE<br>TRUE •                                                                                                                                                                                                                 | SS_CODE Example           | HERE CALL THERE                                                                                                                                                                                                                |  |  |

|                  | •                                                                                                                                                                                                                                          |                           | Before Instruction<br>PC = Address HERE                                                                                                                                                                                        |  |  |

|                  | •<br>Before Instruction<br>PC = address<br>After Instruction<br>if FLAG<1> = 0,                                                                                                                                                            |                           | After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                                                |  |  |

|                  | PC = address<br>if FLAG<1> = 1,                                                                                                                                                                                                            | FALSE CLRF                | Clear f                                                                                                                                                                                                                        |  |  |

|                  | PC = address                                                                                                                                                                                                                               | TRUE Syntax:              | [label] CLRF f                                                                                                                                                                                                                 |  |  |

|                  |                                                                                                                                                                                                                                            | Operands:                 | $0 \le f \le 127$                                                                                                                                                                                                              |  |  |

|                  |                                                                                                                                                                                                                                            | Operation:                | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                                                                          |  |  |

|                  |                                                                                                                                                                                                                                            | Status Affected:          | 7                                                                                                                                                                                                                              |  |  |

| Status Affected: | Z                                                              |                                             |        |      |

|------------------|----------------------------------------------------------------|---------------------------------------------|--------|------|

| Encoding:        | 00                                                             | 0001                                        | lfff   | ffff |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |                                             |        |      |

| Words:           | 1                                                              |                                             |        |      |

| Cycles:          | 1                                                              |                                             |        |      |

| Example          | CLRF                                                           | REG1                                        |        |      |

|                  | R<br>After In                                                  | Instructic<br>REG1 =<br>struction<br>REG1 = | = 0x5A |      |

# 16.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

## 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham