Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| 201010                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f627t-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

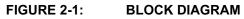

## 2.0 ARCHITECTURAL OVERVIEW

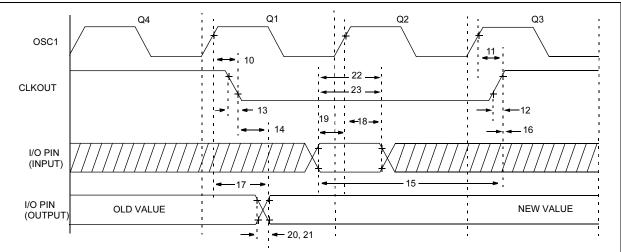

The high performance of the PIC16F62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The Table below lists program memory (FLASH, Data and EEPROM).

TABLE 2-1: DEVICE DESCRIPTION

|            | Memory           |             |                |  |  |  |  |

|------------|------------------|-------------|----------------|--|--|--|--|

| Device     | FLASH<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC16F627  | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16F628  | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF627 | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF628 | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

The PIC16F62X can directly or indirectly address its register files or data memory. All Special Function registers, including the program counter, are mapped in the data memory. The PIC16F62X have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any Addressing mode. This symmetrical nature, and lack of 'special optimal situations' make programming with the PIC16F62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bit wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 2-1, and a description of the device pins in Table 2-1.

Two types of data memory are provided on the PIC16F62X devices. Non-volatile EEPROM data memory is provided for long term storage of data such as calibration values, lookup table data, and any other data which may require periodic updating in the field. This data is not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. It is lost when power is removed.

# PIC16F62X

### 3.2.2.4 PIE1 Register

This register contains interrupt enable bits.

| 51ER 3-4: | PIET REGI                                | SIER (AL     | DRESS:        | ocn)                            |                |           |               |        |

|-----------|------------------------------------------|--------------|---------------|---------------------------------|----------------|-----------|---------------|--------|

|           | R/W-0                                    | R/W-0        | R/W-0         | R/W-0                           | U-0            | R/W-0     | R/W-0         | R/W-0  |

|           | EEIE                                     | CMIE         | RCIE          | TXIE                            |                | CCP1IE    | TMR2IE        | TMR1IE |

|           | bit 7                                    |              |               |                                 |                |           |               | bit 0  |

|           |                                          |              |               |                                 |                |           |               |        |

| bit 7     |                                          | •            | •             | ot Enable Bit                   |                |           |               |        |

|           | 1 = Enables<br>0 = Disable               |              | •             | •                               |                |           |               |        |

| bit 6     | CMIE: Com                                | parator Inte | errupt Enab   | le bit                          |                |           |               |        |

|           | 1 = Enables<br>0 = Disable               |              |               |                                 |                |           |               |        |

| bit 5     | RCIE: USA                                | RT Receive   | e Interrupt E | Enable bit                      |                |           |               |        |

|           | 1 = Enables<br>0 = Disable               |              |               |                                 |                |           |               |        |

| bit 4     | TXIE: USAF                               | RT Transmi   | t Interrupt E | Enable bit                      |                |           |               |        |

|           | 1 = Enables<br>0 = Disable               |              |               |                                 |                |           |               |        |

| bit 3     | Unimpleme                                | ented: Rea   | d as '0'      |                                 |                |           |               |        |

| bit 2     | CCP1IE: CO                               | CP1 Interru  | pt Enable b   | oit                             |                |           |               |        |

|           | 1 = Enables<br>0 = Disable               |              |               |                                 |                |           |               |        |

| bit 1     | TMR2IE: T                                | MR2 to PR2   | 2 Match Inte  | errupt Enable                   | e bit          |           |               |        |

|           |                                          |              |               | itch interrupt<br>atch interrup |                |           |               |        |

| bit 0     | TMR1IE: T                                | MR1 Overfle  | ow Interrup   | t Enable bit                    |                |           |               |        |

|           | 1 = Enables                              | s the TMR1   | overflow in   | nterrupt                        |                |           |               |        |

|           | 0 = Disables the TMR1 overflow interrupt |              |               |                                 |                |           |               |        |

|           | Legend:                                  |              |               |                                 |                |           |               |        |

|           | R = Readat                               | ole bit      | VV = V        | Vritable bit                    | U = Unimple    | emented b | it, read as ' | D'     |

|           | -n = Value a                             | at POR       | '1' = E       | Bit is set                      | '0' = Bit is c | leared    | x = Bit is ur | nknown |

#### REGISTER 3-4: PIE1 REGISTER (ADDRESS: 8Ch)

#### 3.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Detect.

Note: BOD is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOD is cleared, indicating a brown-out has occurred. The BOD STATUS bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### REGISTER 3-6: PCON REGISTER (ADDRESS: 0Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | _   | —   | —   | OSCF  | _   | POR   | BOD   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTRC/ER oscillator frequency

- 1 = 4 MHz typical<sup>(1)</sup>

- 0 = 37 KHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect STATUS bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

- **Note 1:** When in ER Oscillator mode, setting OSCF = 1 will cause the oscillator frequency to change to the frequency specified by the external resistor.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

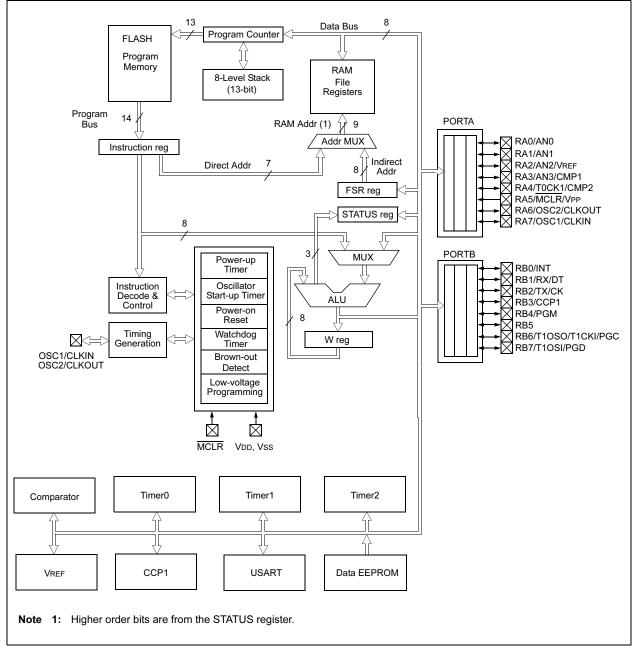

### FIGURE 5-7: BLOCK DIAGRAM OF RA7/OSC1/CLKIN PIN

| Name                                    | Function | Input Type     | Output<br>Type                                                                | Description                                                                                                                                                                       |

|-----------------------------------------|----------|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                                 | RB0      | TTL            | CMOS                                                                          | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | INT      | ST             | _                                                                             | External interrupt.                                                                                                                                                               |

| RB1/RX/DT                               | RB1      | TTL            | CMOS                                                                          | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | RX       | ST             | _                                                                             | USART Receive Pin                                                                                                                                                                 |

|                                         | DT       | ST             | CMOS                                                                          | Synchronous data I/O                                                                                                                                                              |

| RB2/TX/CK                               | RB2      | TTL            | CMOS                                                                          | Bi-directional I/O port                                                                                                                                                           |

|                                         | ТХ       | _              | CMOS                                                                          | USART Transmit Pin                                                                                                                                                                |

|                                         | СК       | ST             | CMOS                                                                          | Synchronous Clock I/O. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                         |          |                | Bi-directional I/O port. Can be software programmed fo internal weak pull-up. |                                                                                                                                                                                   |

|                                         | CCP1     | ST             | CMOS                                                                          | Capture/Compare/PWM/I/O                                                                                                                                                           |

| RB4/PGM                                 | RB4      | TTL            | CMOS                                                                          | Bi-directional I/O port. Can be software programmed fo internal weak pull-up.                                                                                                     |

|                                         | PGM      | ST             | _                                                                             | Low voltage programming input pin. Interrupt-on-pin<br>change. When low voltage programming is enabled, the<br>interrupt-on-pin change and weak pull-up resistor are<br>disabled. |

| RB5                                     | RB5      | TTL            | CMOS                                                                          | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

| RB6/T1OSO/T1CKI/<br>PGC                 | RB6      | TTL            | CMOS                                                                          | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T10SO    | _              | XTAL                                                                          | Timer1 Oscillator Output                                                                                                                                                          |

|                                         | T1CKI    | ST             | —                                                                             | Timer1 Clock Input                                                                                                                                                                |

|                                         | PGC      | ST             | _                                                                             | ICSP Programming Clock                                                                                                                                                            |

| RB7/T1OSI/PGD                           | RB7      | TTL            | CMOS                                                                          | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T1OSI    | XTAL           | _                                                                             | Timer1 Oscillator Input                                                                                                                                                           |

|                                         | PGD      | ST             | CMOS                                                                          | ICSP Data I/O                                                                                                                                                                     |

| Legend: O = Out<br>— = Not<br>TTL = TTL | used     | CM(<br>I<br>OD | OS = CMOS<br>= Input<br>= Open                                                | S Output P = Power<br>ST = Schmitt Trigger Input<br>Drain Output AN = Analog                                                                                                      |

PORTE FUNCTIONS

SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup> TABLE 5-4:

| Address   | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h, 106h | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h, 186h | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h, 181h | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTB.

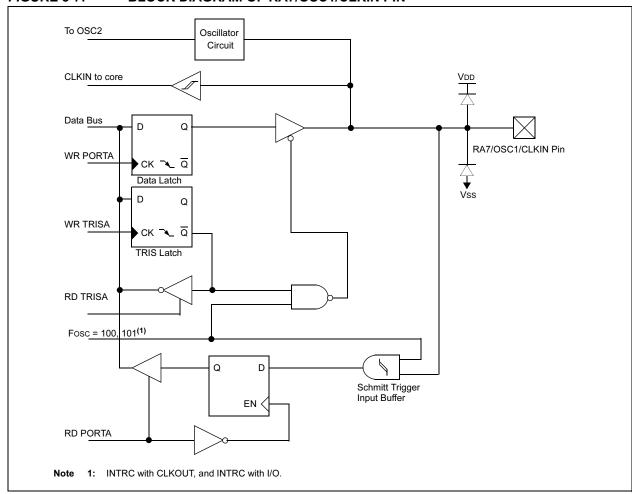

#### 9.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 9-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 17-1.

Note: Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

### 9.6 Comparator Interrupts

The Comparator Interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the Comparator Interrupt Flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a                                       | change     | in  | the   | CMCON      | register |  |  |  |  |

|-------|--------------------------------------------|------------|-----|-------|------------|----------|--|--|--|--|

|       | (C10                                       | UT or C2   | OU  | T) sh | ould occur | r when a |  |  |  |  |

|       | read operation is being executed (start of |            |     |       |            |          |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |            |     |       |            |          |  |  |  |  |

|       | interr                                     | upt flag m | nay | not g | et set.    |          |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

#### 9.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes-up from SLEEP, the contents of the CMCON register are not affected.

## 9.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the Comparator module to be in the comparator RESET mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

### 9.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A source impedance of maximum 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

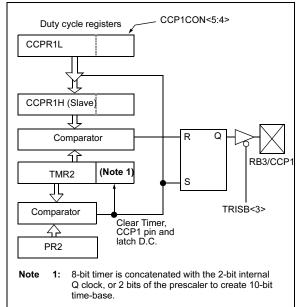

### 11.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTB I/O data |

|       | latch.                                    |

Figure 11-2 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 11.3.3.

#### FIGURE 11-2: SIMPLIFIED PWM BLOCK DIAGRAM

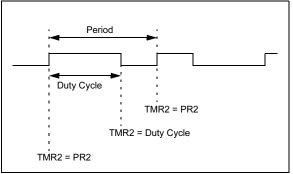

A PWM output (Figure 11-3) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 11-3: PWM OUTPUT

#### 11.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • Tosc • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 8.0) is not used in the determination of the PWM frequency. The postscaler could be used to have an interrupt occur at a different frequency than the PWM output.

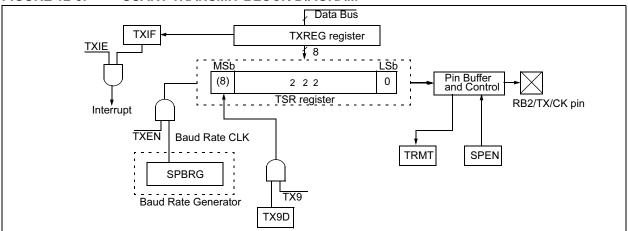

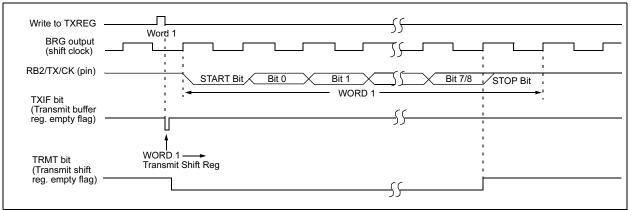

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

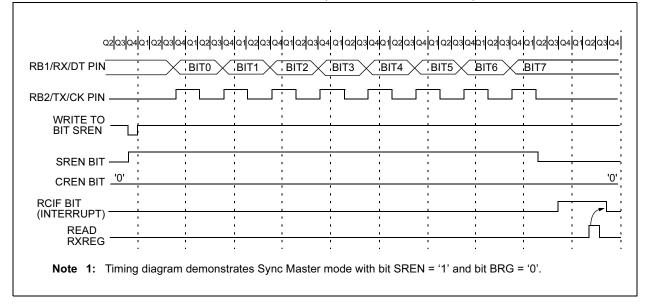

#### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

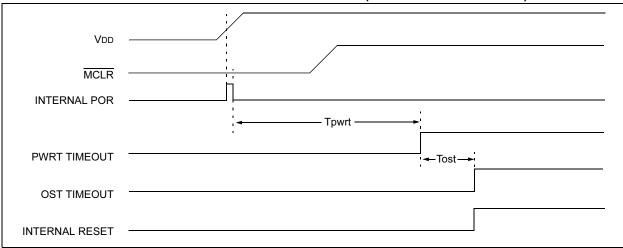

FIGURE 14-9: TIMEOUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

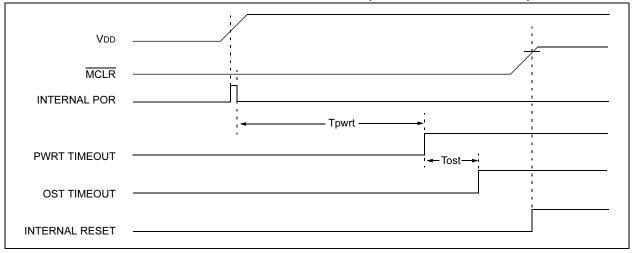

FIGURE 14-10: TIMEOUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

© 2003 Microchip Technology Inc.

## 15.0 INSTRUCTION SET SUMMARY

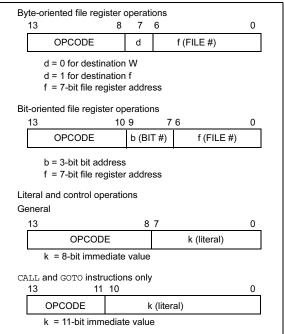

Each PIC16F62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F62X instruction set summary in Table 15-2 lists byte-oriented, bitoriented, and literal and control operations. Table 15-1 shows the opcode field descriptions.

For byte-oriented instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For bit-oriented instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For literal and control operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLA<br>TH    | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| то            | Timeout bit                                                                                                                                                                    |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| < >           | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 15-1 shows the three general formats that the instructions can have.

- Note 1: Any unused opcode is reserved. Use of any reserved opcode may cause unexpected operation.

- 2: To maintain upward compatibility with future PICmicro<sup>®</sup> products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| RETLW            | Return with Literal in W                                                                                                                                                               | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                           | Operation:       | $d \in [0,1]$<br>See description below                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                   | Status Affected: | С                                                                                                                                                                                                              |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                              |

| Description:     | The W register is loaded with<br>the eight bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0 the result<br>is placed in the W register. If 'd' is<br>1 the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      | Words:           | 1                                                                                                                                                                                                              |

| Example          | CALL TABLE;W contains table                                                                                                                                                            | Cycles:          | 1                                                                                                                                                                                                              |

|                  | <ul> <li>;offset value</li> <li>;W now has table</li> </ul>                                                                                                                            | -                |                                                                                                                                                                                                                |

|                  | value                                                                                                                                                                                  | Example          | RLF REG1, 0<br>Before Instruction                                                                                                                                                                              |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8             |                  | REG1 = 1110 0110 $C = 0$ After Instruction $REG1 = 1110 0110$ $W = 1100 1100$ $C = 1$                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

| Syntax:          | [label] RETURN                                                                                                                                                                         |                  |                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction.                             |                  |                                                                                                                                                                                                                |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Example          | RETURN                                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                            |                  |                                                                                                                                                                                                                |

#### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

#### 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

#### 17.1 DC Characteristics: PIC16F62X-04 (Commercial, Industrial, Extended) PIC16F62X-20 (Commercial, Industrial, Extended) PIC16LF62X-04 (Commercial, Industrial)

| PIC16F62                                                           |      |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |             |          |                                                                               |  |

|--------------------------------------------------------------------|------|-----------------------------------------------|------------------------------------------------------|------|-------------|----------|-------------------------------------------------------------------------------|--|

| PIC16F62X-04<br>PIC16F62X-20<br>(Commercial, Industrial, Extended) |      |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |             |          |                                                                               |  |

| Param<br>No.                                                       | Sym  | Characteristic/Device                         | Min                                                  | Тур† | Max         | Units    | Conditions                                                                    |  |

|                                                                    | Vdd  | Supply Voltage                                |                                                      |      |             |          |                                                                               |  |

| D001                                                               |      | PIC16LF62X                                    | 2.0                                                  | _    | 5.5         | V        |                                                                               |  |

| D001                                                               |      | PIC16F62X                                     | 3.0                                                  | _    | 5.5         | V        |                                                                               |  |

| D002                                                               | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | _                                                    | 1.5  | _           | V        | Device in SLEEP mode*                                                         |  |

| D003                                                               | VPOR | VDD Start Voltage<br>to ensure Power-on Reset | _                                                    | Vss  | _           | V        | See section on Power-on Reset for details                                     |  |

| D004                                                               | SVDD | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05                                                 | —    | —           | V/ms     | See section on Power-on Reset for details*                                    |  |

| D005                                                               | VBOD | Brown-out Detect Voltage                      | 3.65<br>3.65                                         | 4.0  | 4.35<br>4.4 | V<br>V   | BODEN configuration bit is set<br>BODEN configuration bit is set,<br>Extended |  |

|                                                                    | IDD  | Supply Current <sup>(2), (5)</sup>            |                                                      |      |             |          | •                                                                             |  |

| D010                                                               |      | PIC16LF62X                                    | _                                                    | 0.30 | 0.6         | mA       | Fosc = 4.0 MHz, VDD = 2.0 <sup>(5)</sup>                                      |  |

| D010                                                               |      |                                               | —                                                    | 1.10 | 2.0         | mA       | Fosc = 4.0 MHz, VDD = 5.5*                                                    |  |

| D013                                                               |      |                                               | —                                                    | 4.0  | 7.0         | mA       | Fosc = 20.0 MHz, VDD = 5.5                                                    |  |

|                                                                    |      |                                               | _                                                    | 3.80 | 6.0<br>2.0  | mA<br>mA | Fosc = 20.0 MHz, VDD = 4.5*<br>Fosc = 10.0 MHz, VDD = 3.0 <sup>(6)</sup>      |  |

|                                                                    |      |                                               | _                                                    | 20   | 30          | μA       | Fosc = 32  kHz,  VDD = 3.0  M                                                 |  |

| D010                                                               |      | PIC16F62X                                     | _                                                    | 0.60 | 0.7         | mA       | Fosc = 4.0 MHz, VDD = 3.0                                                     |  |

|                                                                    |      |                                               | _                                                    | 1.10 | 2.0         | mA       | Fosc = 4.0 MHz, VDD = 5.5*                                                    |  |

| D013                                                               |      |                                               | —                                                    | 4.0  | 7.0         | mA       | Fosc = 20.0 MHz, VDD = 5.5                                                    |  |

|                                                                    |      |                                               | —                                                    | 3.80 | 6.0         | mA       | Fosc = 20.0 MHz, VDD = $4.5^*$                                                |  |

| D014                                                               |      |                                               | _                                                    | 20   | 2.0<br>30   | mA<br>μA | Fosc = 10.0 MHz, VDD = 3.0* <sup>(6)</sup><br>Fosc = 32 kHz, VDD = 3.0*       |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active Operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

5: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

6: Commercial temperature only.

#### 17.2 DC Characteristics: PIC16F62X (Commercial, Industrial, Extended) PIC16LF62X (Commercial, Industrial)

| DC CHARACTERISTICS |       |                                           | Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial and $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended         Operating voltage VDD range as described in DC spec Table 17-1 and Table 17-2 |      |               |              |                                                                     |  |  |  |

|--------------------|-------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--------------|---------------------------------------------------------------------|--|--|--|

| Param.<br>No.      | Sym   | Characteristic/Device                     | Min                                                                                                                                                                                                                                                                                                                                                | Тур† | Мах           | Unit         | Conditions                                                          |  |  |  |

|                    | VIL   | Input Low Voltage                         |                                                                                                                                                                                                                                                                                                                                                    |      |               |              |                                                                     |  |  |  |

|                    |       | I/O ports                                 |                                                                                                                                                                                                                                                                                                                                                    |      |               |              |                                                                     |  |  |  |

| D030               |       | with TTL buffer                           | Vss                                                                                                                                                                                                                                                                                                                                                | _    | 0.8           | V            | VDD = 4.5V to 5.5V                                                  |  |  |  |

|                    |       |                                           |                                                                                                                                                                                                                                                                                                                                                    |      | 0.15 VDD      | V            | otherwise                                                           |  |  |  |

| D031               |       | with Schmitt Trigger input                | Vss                                                                                                                                                                                                                                                                                                                                                |      | 0.2 VDD       | V            |                                                                     |  |  |  |

| D032               |       | MCLR, RA4/T0CKI,OSC1<br>(in ER mode)      | Vss                                                                                                                                                                                                                                                                                                                                                | —    | 0.2 VDD       | V            | (Note1)                                                             |  |  |  |

| D033               |       | OSC1 (in XT and HS)                       | Vss                                                                                                                                                                                                                                                                                                                                                | _    | 0.3 VDD       | V            |                                                                     |  |  |  |

| 2000               |       | OSC1 (in LP)                              | Vss                                                                                                                                                                                                                                                                                                                                                | _    | 0.6 Vdd - 1.0 | V            |                                                                     |  |  |  |

|                    | VIH   | Input High Voltage                        |                                                                                                                                                                                                                                                                                                                                                    |      |               |              | •                                                                   |  |  |  |

|                    |       | I/O ports                                 |                                                                                                                                                                                                                                                                                                                                                    |      |               |              |                                                                     |  |  |  |

| D040               |       | with TTL buffer                           | 2.0V                                                                                                                                                                                                                                                                                                                                               | —    | Vdd           | V            | VDD = 4.5V to 5.5V                                                  |  |  |  |

|                    |       |                                           | .25 VDD + 0.8V                                                                                                                                                                                                                                                                                                                                     |      | Vdd           | V            | otherwise                                                           |  |  |  |

| D041               |       | with Schmitt Trigger input                | 0.8 VDD                                                                                                                                                                                                                                                                                                                                            | —    | VDD           | V            |                                                                     |  |  |  |

| D042               |       | MCLR RA4/T0CKI                            | 0.8 VDD                                                                                                                                                                                                                                                                                                                                            | _    | VDD           | V            |                                                                     |  |  |  |

| D043<br>D043A      |       | OSC1 (XT, HS and LP)                      | 0.7 VDD<br>0.9 VDD                                                                                                                                                                                                                                                                                                                                 |      | Vdd           | V<br>V       | (Noto1)                                                             |  |  |  |

|                    |       | OSC1 (in ER mode)                         | 50                                                                                                                                                                                                                                                                                                                                                 | 200  | 400           |              | (Note1)<br>VDD = 5.0V, VPIN = VSS                                   |  |  |  |

| D070               | IPURB | PORTB weak pull-up<br>current             | 50                                                                                                                                                                                                                                                                                                                                                 | 200  | 400           | μA           | VDD = 5.0V, VPIN = VSS                                              |  |  |  |

|                    | lı∟   | Input Leakage Current <sup>(2), (3)</sup> | Current <sup>(2), (3)</sup>                                                                                                                                                                                                                                                                                                                        |      |               |              |                                                                     |  |  |  |

|                    |       | I/O ports (Except PORTA)                  |                                                                                                                                                                                                                                                                                                                                                    |      | ±1.0          | μΑ           | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                     |  |  |  |

| D060               |       | PORTA                                     | —                                                                                                                                                                                                                                                                                                                                                  | —    | ±0.5          | μΑ           | $VSS \le VPIN \le VDD$ , pin at hi-impedance                        |  |  |  |

| D061               |       | RA4/T0CKI                                 | —                                                                                                                                                                                                                                                                                                                                                  | _    | ±1.0          | μA           | $Vss \leq V \text{PIN} \leq V \text{DD}$                            |  |  |  |

| D063               |       | OSC1, MCLR                                | —                                                                                                                                                                                                                                                                                                                                                  | —    | ±5.0          | μΑ           | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc                       |  |  |  |

|                    |       |                                           |                                                                                                                                                                                                                                                                                                                                                    |      |               |              | configuration                                                       |  |  |  |

|                    | Vol   | Output Low Voltage                        | 1                                                                                                                                                                                                                                                                                                                                                  |      | 1             |              | 1                                                                   |  |  |  |

| D080               |       | I/O ports                                 | —                                                                                                                                                                                                                                                                                                                                                  | —    | 0.6           | V            | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                 |  |  |  |

|                    |       |                                           | —                                                                                                                                                                                                                                                                                                                                                  | —    | 0.6           | V            | IOL=7.0 mA, VDD=4.5V, +125°C                                        |  |  |  |

| D083               |       | OSC2/CLKOUT (ER only)                     | —                                                                                                                                                                                                                                                                                                                                                  | _    | 0.6<br>0.6    | V<br>V       | IOL=1.6 mA, VDD=4.5V, -40° to +85°C<br>IOL=1.2 mA, VDD=4.5V, +125°C |  |  |  |

|                    | Voн   | Output High Voltage <sup>(3)</sup>        |                                                                                                                                                                                                                                                                                                                                                    |      | 0.0           | v            |                                                                     |  |  |  |

| D090               |       | I/O ports (Except RA4)                    | VDD - 0.7                                                                                                                                                                                                                                                                                                                                          |      |               | V            | Іон=-3.0 mA. VDD=4.5V40° to +85°С                                   |  |  |  |

| 2000               |       |                                           | VDD - 0.7<br>VDD - 0.7                                                                                                                                                                                                                                                                                                                             | _    | _             | v            | IOH=-2.5 mA, VDD=4.5V, +125°C                                       |  |  |  |