Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 3.2.2.4 and Section 3.2.2.5 for a description of the comparator enable and flag bits.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 3-3: |                                             | REGISTER                      | (ADDRES      | S: 0Bh, 8 | Bh, 10Bh, 18             | Bh)          |               |       |  |

|---------------|---------------------------------------------|-------------------------------|--------------|-----------|--------------------------|--------------|---------------|-------|--|

|               | R/W-0                                       | R/W-0                         | R/W-0        | R/W-0     | R/W-0                    | R/W-0        | R/W-0         | R/W-x |  |

|               | GIE                                         | PEIE                          | T0IE         | INTE      | RBIE                     | T0IF         | INTF          | RBIF  |  |

|               | bit 7                                       |                               |              |           |                          |              |               | bit 0 |  |

| bit 7         | GIE: Globa                                  | al Interrupt E                | nable bit    |           |                          |              |               |       |  |

|               |                                             | s all unmas<br>es all interru | •            | ots       |                          |              |               |       |  |

| bit 6         | PEIE: Peri                                  | oheral Interr                 | upt Enable   | bit       |                          |              |               |       |  |

|               |                                             | s all unmas<br>es all periph  |              |           | S                        |              |               |       |  |

| bit 5         | TOIE: TMR                                   | 0 Overflow                    | Interrupt En | able bit  |                          |              |               |       |  |

|               |                                             | s the TMR0<br>es the TMR0     |              |           |                          |              |               |       |  |

| bit 4         | INTE: RB0/INT External Interrupt Enable bit |                               |              |           |                          |              |               |       |  |

|               |                                             | s the RB0/II<br>es the RB0/I  |              |           |                          |              |               |       |  |

| bit 3         | RBIE: RB Port Change Interrupt Enable bit   |                               |              |           |                          |              |               |       |  |

|               |                                             | s the RB po<br>es the RB po   |              |           |                          |              |               |       |  |

| bit 2         | TOIF: TMR                                   | 0 Overflow                    | nterrupt Fla | ag bit    |                          |              |               |       |  |

|               |                                             | register has<br>register did  |              |           | eared in softwa          | are)         |               |       |  |

| bit 1         | INTF: RB0                                   | /INT Externa                  | al Interrupt | Flag bit  |                          |              |               |       |  |

|               |                                             | 30/INT exter<br>30/INT exter  |              | •         | must be cleare           | d in softwaı | e)            |       |  |

| bit 0         | RBIF: RB I                                  | Port Change                   | Interrupt F  | lag bit   |                          |              |               |       |  |

|               |                                             | at least one<br>of the RB7:R  |              |           | nanged state (n<br>state | nust be clea | ared in softw | vare) |  |

|               | Levendu                                     |                               |              |           |                          |              |               | 1     |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000       | xxxu 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

TABLE 5-2:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTA<sup>(1)</sup>

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTA.

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

PORTB is multiplexed with the external interrupt, USART, CCP module and the TMR1 clock input/output. The standard port functions and the alternate port functions are shown in Table 5-3. Alternate port functions override TRIS setting when enabled.

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-onchange comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | when a read operation is being executed       |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

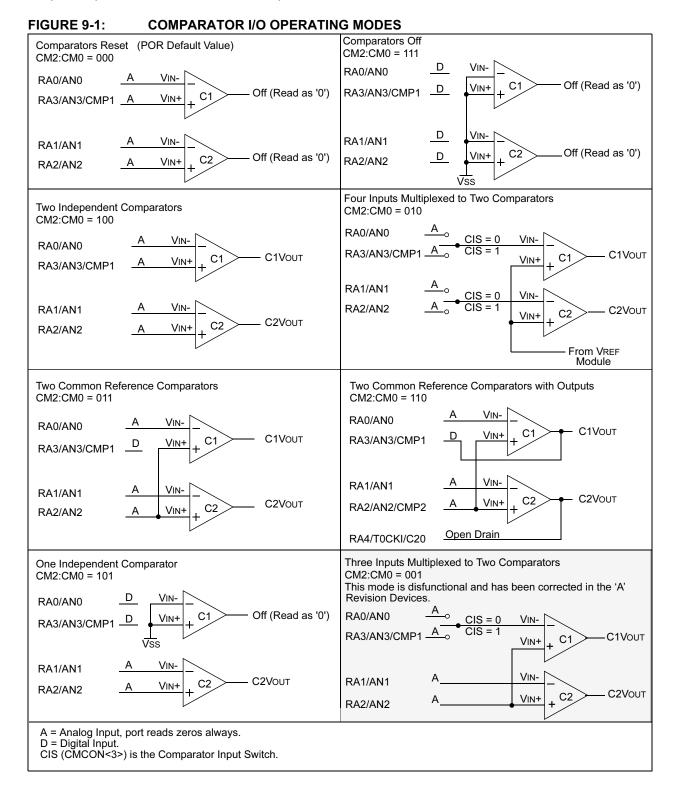

#### 9.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 9-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 17-1.

Note: Comparator interrupts should be disabled during a Comparator mode change otherwise a false interrupt may occur.

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

## 10.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

## 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

## 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

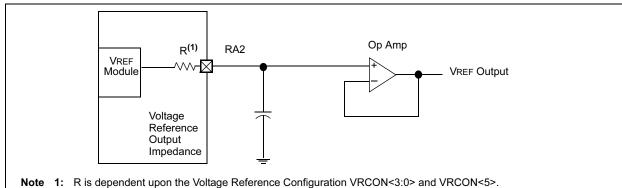

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

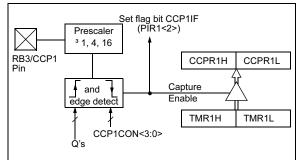

## 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the Interrupt Request Flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 11.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

## TABLE 11-2:CAPTURE MODE OPERATION<br/>BLOCK DIAGRAM

### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 11-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

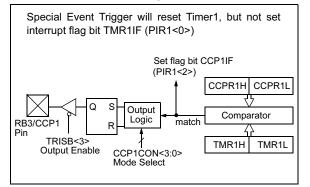

## 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 11-1: COMPARE MODE OPERATION BLOCK DIAGRAM

### 11.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an output by clearing the TRISB<3> bit.

Note: Clearing the CCP1CON register will force the RB3/CCP1 compare output latch to the default low level. This is not the data latch.

NOTES:

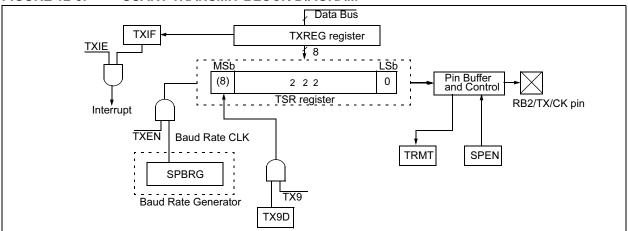

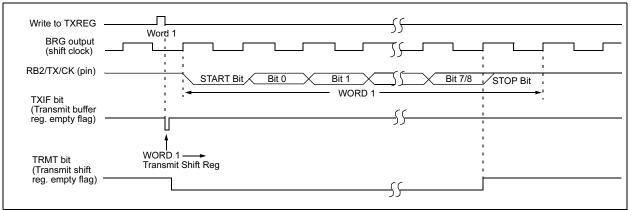

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

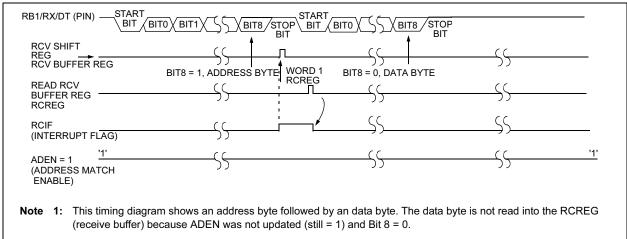

| FIGURE 12-9: | ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT |

|--------------|--------------------------------------------|

|              |                                            |

|                                                               | BIT0 X BIT1 X _ STOP<br>BIT<br>♦ |                               |          |            |

|---------------------------------------------------------------|----------------------------------|-------------------------------|----------|------------|

| RCV SHIFT REG                                                 | (                                |                               | ((       |            |

| RCV BUFFER REG                                                | ) )<br>BIT8 = 0, DATA BYTE       | BIT8 = 1, ADDRESS BYTE WORD 1 |          |            |

| READ RCV                                                      | ((                               | ( C                           | (        | п          |

| BUFFER REG<br>RCREG                                           |                                  |                               |          |            |

| RCIF<br>(INTERRUPT FLAG)                                      |                                  | <u>_</u>                      | <u> </u> | ¥          |

| ADEN = 1 <sup>'<u>1'</u><br/>(ADDRESS MATCH<br/>ENABLE)</sup> | <u>_</u>                         | <u> </u>                      | <u> </u> | <u>'1'</u> |

#### FIGURE 12-10: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

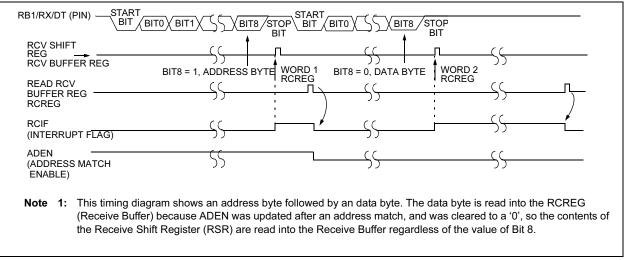

## FIGURE 12-11: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST FOLLOWED BY VALID DATA BYTE

| REGISTER 13-2: | EECON1 REGISTER (ADDRESS: 9Ch)                                                                                                                                                                          |                                             |                |              |                       |              |                |           |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------|--------------|-----------------------|--------------|----------------|-----------|

|                | U-0                                                                                                                                                                                                     | U-0                                         | U-0            | U-0          | R/W-x                 | R/W-0        | R/S-0          | R/S-x     |

|                | —                                                                                                                                                                                                       | _                                           | _              | —            | WRERR                 | WREN         | WR             | RD        |

|                | bit 7                                                                                                                                                                                                   |                                             |                |              |                       |              |                | bit 0     |

| bit 7-4        | Unimpleme                                                                                                                                                                                               | Unimplemented: Read as '0'                  |                |              |                       |              |                |           |

| bit 3          | WRERR: E                                                                                                                                                                                                | EPROM Er                                    | ror Flag bit   |              |                       |              |                |           |

|                | normal                                                                                                                                                                                                  | operation is<br>operation o<br>te operatior | r BOD Res      | et)          | d (any MCLR R         | eset, any \  | WDT Reset      | during    |

| bit 2          | WREN: EE                                                                                                                                                                                                | PROM Write                                  | e Enable bi    | t            |                       |              |                |           |

|                | 1 = Allows<br>0 = Inhibits                                                                                                                                                                              |                                             |                | ROM          |                       |              |                |           |

| bit 1          | WR: Write                                                                                                                                                                                               | Control bit                                 |                |              |                       |              |                |           |

|                | can onl                                                                                                                                                                                                 | y be set (no                                | ot cleared) ii |              | y hardware onc<br>ete | e write is c | complete. T    | he WR bit |

| bit 0          | RD: Read (                                                                                                                                                                                              | Control bit                                 |                |              |                       |              |                |           |

|                | <ul> <li>1 = Initiates an EEPROM read (read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software).</li> <li>0 = Does not initiate an EEPROM read</li> </ul> |                                             |                |              |                       |              |                |           |

|                | Legend:                                                                                                                                                                                                 |                                             |                |              |                       |              |                |           |

|                | R = Readal                                                                                                                                                                                              | ole bit                                     | W = V          | Vritable bit | U = Unimple           | emented bi   | it, read as '( | D'        |

|                | -n = Value a                                                                                                                                                                                            | at POR                                      | '1' = B        | lit is set   | '0' = Bit is c        | leared       | x = Bit is ur  | nknown    |

#### TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7  | Bit 6                     | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|---------|-----------------------|--------|---------------------------|----------|-------|-------|-------|-------|-----------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPROM | EPROM data register       |          |       |       |       |       | XXXX XXXX | uuuu uuuu                     |                                 |

| 9Bh     | EEADR                 | EEPROM | address                   | register |       |       |       |       |           | XXXX XXXX                     | uuuu uuuu                       |

| 9Ch     | EECON1                | _      | _                         |          | _     | WRERR | WREN  | WR    | RD        | x000                          | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM | EEPROM control register 2 |          |       |       |       |       |           |                               |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

**Note 1:** EECON2 is not a physical register

### **REGISTER 14-1: CONFIGURATION WORD**

| CP1                         | CP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CP1                                                                                                                                                 | CP0                                                                                                                                                    | _                                                                                                           | CPD                                       | LVP                                     | BODEN                                | MCLRE                                       | FOSC2                                      | PWRTE                 | WDTE | F0SC1 | F0SC0 |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|--------------------------------------|---------------------------------------------|--------------------------------------------|-----------------------|------|-------|-------|

| bit 13                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     | ·                                                                                                                                                      |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       | bit 0 |

| bit 13-10:                  | Code<br>11 =<br>01 =<br>00 =<br>Code<br>11 =<br>10 =<br>01 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | protection<br>Program<br>0400h-07<br>0200h-07<br>0000h-07<br>protection<br>Program<br>Program<br>0200h-03                                           | le Protection<br>n for 2K prog<br>memory cod<br>7FFh code p<br>7FFh code p<br>7FFh code p<br>n for 1K prog<br>memory cod<br>3FFh code p<br>3FFh code p | gram memore<br>rotected<br>rotected<br>otected<br>gram memore<br>de protection<br>de protection<br>rotected | on off<br>ory<br>on off                   |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 9:                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 8:                      | <b>CPD:</b><br>1 = Da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Unimplemented: Read as '0'<br>CPD: Data Code Protection bit <sup>(3)</sup><br>1 = Data memory code protection off<br>0 = Data memory code protected |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 7:                      | <ul> <li>LVP: Low Voltage Programming Enable</li> <li>RB4/PGM pin has PGM function, low voltage programming enabled</li> <li>RB4/PGM is digital I/O, HV on MCLR must be used for programming</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                     |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 6:                      | BODEN: Brown-out Detect Reset Enable bit <sup>(1)</sup><br>1 = BOD Reset enabled<br>0 = BOD Reset disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                     |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 5:                      | 1 = R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A5/MCLF                                                                                                                                             | MCLR pin fu<br>pin functior<br>pin functior                                                                                                            | is MCLR                                                                                                     |                                           | R internally                            | tied to VDD                          | )                                           |                                            |                       |      |       |       |

| bit 3:                      | 1 = P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>TEN</b> : Pow<br>WRT disa<br>WRT ena                                                                                                             |                                                                                                                                                        | Enable bit                                                                                                  | (1)                                       |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 2:                      | 1 = W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DT enab                                                                                                                                             |                                                                                                                                                        | Enable bit                                                                                                  |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 4, 1-0:                 | <ul> <li>0 = WDT disabled</li> <li>FOSC2:FOSC0: Oscillator Selection bits<sup>(4)</sup></li> <li>111 = ER oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, Resistor on RA7/OSC1/CLKIN</li> <li>100 = ER oscillator: I/O function on RA6/OSC2/CLKOUT pin, Resistor on RA7/OSC1/CLKIN</li> <li>101 = INTRC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN</li> <li>100 = INTRC oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN</li> <li>101 = EC: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN</li> <li>011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN</li> <li>010 = HS oscillator: High speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN</li> <li>001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN</li> <li>000 = LP oscillator: Low power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN</li> </ul> |                                                                                                                                                     |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

|                             | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Er<br>2: Al<br>3: Th                                                                                                                                | nabling Brow<br>nsure the Po<br>I of the CP1:<br>ne entire data<br>hen MCLR i                                                                          | wer-up Tim<br>CP0 pairs<br>a EEPROM                                                                         | er is enab<br>have to be<br>I will be era | led anytime<br>given the s<br>ased when | Brown-ou<br>same value<br>the code p | t Detect Re<br>to enable to<br>rotection is | eset is enab<br>the code pr<br>turned off. | oled.<br>rotection sc |      |       | WRTE. |

| <b>Legend</b><br>R = Readat |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                                                        |                                                                                                             | itable bit                                |                                         |                                      |                                             | ited bit, rea                              |                       |      |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0 | )'                 |

|-------------------|------------------|-----------------------------------|--------------------|

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared                | x = bit is unknown |

-

### 14.5.5 TIMEOUT SEQUENCE

On power-up the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired. Then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in ER mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 14-8, Figure 14-9 and Figure 14-10 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16F62X device operating in parallel.

Table 14-7 shows the RESET conditions for some special registers, while Table 14-8 shows the RESET conditions for all the registers.

#### 14.5.6 POWER CONTROL (PCON) STATUS REGISTER

The Power Control/STATUS register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{BOD}$  (Brown-out).  $\overline{BOD}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOD} = 0$  indicating that a brown-out has occurred. The  $\overline{BOD}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Detect  | Wake-up    |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | Reset             | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| ER, INTRC, EC            | 72 ms             | _         | 72 ms             | —          |  |

## TABLE 14-4: TIMEOUT IN VARIOUS SITUATIONS

| IABLE 14 | TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE |    |    |                                    |  |  |  |  |

|----------|-----------------------------------------------------|----|----|------------------------------------|--|--|--|--|

| POR      | BOD                                                 | то | PD |                                    |  |  |  |  |

| 0        | Х                                                   | 1  | 1  | Power-on Reset                     |  |  |  |  |

| 0        | х                                                   | 0  | х  | Illegal, TO is set on POR          |  |  |  |  |

| 0        | х                                                   | х  | 0  | Illegal, PD is set on POR          |  |  |  |  |

| 1        | 0                                                   | Х  | Х  | Brown-out Detect Reset             |  |  |  |  |

| 1        | 1                                                   | 0  | u  | WDT Reset                          |  |  |  |  |

| 1        | 1                                                   | 0  | 0  | WDT Wake-up                        |  |  |  |  |

| 1        | 1                                                   | u  | u  | MCLR Reset during normal operation |  |  |  |  |

| 1        | 1                                                   | 1  | 0  | MCLR Reset during SLEEP            |  |  |  |  |

#### TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Legend: u = unchanged, x = unknown.

#### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     | _     | -     | OSCF  | Reset | POR   | BOD   | 1-0x                  | u-uq                                           |

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect Reset and Watchdog Timer Reset during normal operation.

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test f, Skip if Clear                                                            |  |  |  |

|------------------|---------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             | Syntax:          | [ <i>label</i> ]BTFSC f,b                                                            |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                  |  |  |  |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                              |  |  |  |

| Status Affected: | None                                                                | Status Affected: | None                                                                                 |  |  |  |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                                    |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0' then the                                           |  |  |  |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0' then the next                      |  |  |  |

| Cycles:          | 1                                                                   |                  | instruction fetched during the                                                       |  |  |  |

| Example          | BCF REG1, 7                                                         |                  | current instruction execution is                                                     |  |  |  |

|                  | Before Instruction<br>REG1 = 0xC7<br>After Instruction              |                  | discarded, and a NOP is executed<br>instead, making this a two-cycle<br>instruction. |  |  |  |

|                  | REG1 = 0x47                                                         | Words:           | 1                                                                                    |  |  |  |

|                  |                                                                     | Cycles:          | 1 <sup>(2)</sup>                                                                     |  |  |  |

| BSF              | Bit Set f                                                           | Example          | HERE BTFSC REG1<br>FALSE GOTO PROCESS_CODE                                           |  |  |  |

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |                  | TRUE •                                                                               |  |  |  |

| Operands:        | $0 \le f \le 127$                                                   |                  | •                                                                                    |  |  |  |

|                  | $0 \le b \le 7$                                                     |                  | Before Instruction                                                                   |  |  |  |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | PC = address HERE                                                                    |  |  |  |

| Status Affected: | None                                                                |                  | After Instruction<br>if REG<1> = 0,                                                  |  |  |  |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | PC = address TRUE                                                                    |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | if REG<1>=1,                                                                         |  |  |  |

| Words:           | 1                                                                   |                  | PC = address FALSE                                                                   |  |  |  |

| Cycles:          | 1                                                                   |                  |                                                                                      |  |  |  |

Example

BSF

REG1, 7

REG1 = 0x0A

REG1 = 0x8A

Before Instruction

After Instruction

| MOVWF            | Move W to f                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                              |

| Operands:        | $0 \leq f \leq 127$                                                                                   |

| Operation:       | $(W) \rightarrow (f)$                                                                                 |

| Status Affected: | None                                                                                                  |

| Encoding:        | 00 0000 1fff ffff                                                                                     |

| Description:     | Move data from W register to register 'f'.                                                            |

| Words:           | 1                                                                                                     |

| Cycles:          | 1                                                                                                     |

| Example          | MOVWF REG1                                                                                            |

|                  | Before Instruction<br>REG1 = $0xFF$<br>W = $0x4F$<br>After Instruction<br>REG1 = $0x4F$<br>W = $0x4F$ |

| OPTION           | Load Op                                                                | otion Re                                                                  | gister                                                                                                |                                                      |  |  |

|------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Syntax:          | [ label ] OPTION                                                       |                                                                           |                                                                                                       |                                                      |  |  |

| Operands:        | None                                                                   |                                                                           |                                                                                                       |                                                      |  |  |

| Operation:       | $(W) \rightarrow C$                                                    | PTION                                                                     |                                                                                                       |                                                      |  |  |

| Status Affected: | None                                                                   |                                                                           |                                                                                                       |                                                      |  |  |

| Encoding:        | 00                                                                     | 0000                                                                      | 0110                                                                                                  | 0010                                                 |  |  |

| Description:     | loaded in<br>This inst<br>code cor<br>products<br>readable<br>user can | n the OP<br>ruction is<br>npatibilit<br>Since (<br>e/writable<br>directly | he W regi<br>TION reg<br>s supporte<br>y with PIC<br>OPTION i<br>register,<br>address i<br>ruction su | ister.<br>ed for<br>C16C5X<br>s a<br>the<br>t. Using |  |  |

| Words:           | 1                                                                      |                                                                           |                                                                                                       |                                                      |  |  |

| Cycles:          | 1                                                                      |                                                                           |                                                                                                       |                                                      |  |  |

| Example          |                                                                        |                                                                           |                                                                                                       |                                                      |  |  |

|                  |                                                                        | future P<br>not use                                                       | vard com<br>lCmicro <sup>@</sup><br>this                                                              |                                                      |  |  |

| NOP              | No Operation |        |      |      |  |  |

|------------------|--------------|--------|------|------|--|--|

| Syntax:          | [ label ]    | NOP    |      |      |  |  |

| Operands:        | None         |        |      |      |  |  |

| Operation:       | No operation |        |      |      |  |  |

| Status Affected: | None         |        |      |      |  |  |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |  |  |

| Description:     | No oper      | ation. | •    |      |  |  |

| Words:           | 1            |        |      |      |  |  |

| Cycles:          | 1            |        |      |      |  |  |

| Example          | NOP          |        |      |      |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS)<br>is loaded in the PC. Interrupts<br>are enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-<br>cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                     |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                     |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                |  |  |  |  |  |

## 16.19 PICDEM 18R PIC18C601/801 Demonstration Board

The PICDEM 18R demonstration board serves to assist development of the PIC18C601/801 family of Microchip microcontrollers. It provides hardware implementation of both 8-bit Multiplexed/De-multiplexed and 16-bit Memory modes. The board includes 2 Mb external FLASH memory and 128 Kb SRAM memory, as well as serial EEPROM, allowing access to the wide range of memory types supported by the PIC18C601/801.

## 16.20 PICDEM LIN PIC16C43X Demonstration Board

The powerful LIN hardware and software kit includes a series of boards and three PICmicro microcontrollers. The small footprint PIC16C432 and PIC16C433 are used as slaves in the LIN communication and feature on-board LIN transceivers. A PIC16F874 FLASH microcontroller serves as the master. All three microcontrollers are programmed with firmware to provide LIN bus communication.

## 16.21 PICDEM USB PIC16C7X5 Demonstration Board

The PICDEM USB Demonstration Board shows off the capabilities of the PIC16C745 and PIC16C765 USB microcontrollers. This board provides the basis for future USB products.

## 16.22 Evaluation and Programming Tools

In addition to the PICDEM series of circuits, Microchip has a line of evaluation kits and demonstration software for these products.

- KEELOQ evaluation and programming tools for Microchip's HCS Secure Data Products

- CAN developers kit for automotive network applications

- Analog design boards and filter design software

- PowerSmart battery charging evaluation/ calibration kits

- IrDA<sup>®</sup> development kit

- microID development and RFLab<sup>™</sup> development software

- SEEVAL<sup>®</sup> designer kit for memory evaluation and endurance calculations

- PICDEM MSC demo boards for Switching mode power supply, high power IR driver, delta sigma ADC, and flow rate sensor

Check the Microchip web page and the latest Product Line Card for the complete list of demonstration and evaluation kits.

| ABLE         | 1/-4. | EXTERNAL CLOCK TIMING                   |        |      | 13        |            |                              |

|--------------|-------|-----------------------------------------|--------|------|-----------|------------|------------------------------|

| Param<br>No. | Sym   | Characteristic                          | Min    | Тур† | Мах       | Units      | Conditions                   |

|              | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC     |      | 4         | MHz        | XT and ER Osc mode,          |

|              |       |                                         |        |      |           |            | VDD = 5.0V                   |

|              |       |                                         | DC     | _    | 20        | MHz        | HS Osc mode                  |

|              |       |                                         | DC     | —    | 200       | kHz        | LP Osc mode                  |

|              |       | Oscillator Frequency <sup>(1)</sup>     |        |      | 4         |            | ER Osc mode, VDD = 5.0V      |

|              |       | Oscillator Frequency ?                  | 0.1    | _    |           | MHz        |                              |

|              |       |                                         |        | _    | 4         |            |                              |

|              |       |                                         | 1      |      | 20<br>200 | MHz<br>kHz | HS Osc mode<br>LP Osc mode   |

|              |       |                                         | 3.65   | 4    | 4.28      | MHz        |                              |

|              |       |                                         | 0.00   | 37   | 1.20      | kHz        | INTRC mode (slow)            |

| 4            | INTRC | Internal Calibrated RC                  | 3.65   | 4.00 | 4.28      | MHz        |                              |

| 5            | ER    | External Biased ER Frequency            | 10 kHz |      | 8 MHz     |            | VDD = 5.0V                   |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250    |      | _         | ns         | XT and ER Osc mode           |

|              |       |                                         | 50     | _    |           | ns         | HS Osc mode                  |

|              |       |                                         | 5      | —    | —         | μs         | LP Osc mode                  |

|              |       |                                         |        |      |           |            |                              |

|              |       | Oscillator Period <sup>(1)</sup>        | 250    |      | —         | ns         | ER Osc mode                  |

|              |       |                                         | 250    | _    | 10,000    | ns         | XT Osc mode                  |

|              |       |                                         | 50     | _    | 1,000     | ns         | HS Osc mode                  |

|              |       |                                         | 5      |      |           | μs         | LP Osc mode                  |

|              |       |                                         |        | 250  |           | ns         | INTRC mode (fast)            |

|              |       |                                         |        | 27   |           | μs         | INTRC mode (slow)            |

| 2            | Тсу   | Instruction Cycle Time                  | 1.0    | Тсү  | DC        | ns         | Tcy = 4/Fosc                 |

| 3            | TosL, | External CLKIN (OSC1) High              | 100 *  | _    | —         | ns         | XT oscillator, Tosc L/H duty |

|              | TosH  | External CLKIN Low                      |        |      |           |            | cycle*                       |

### TABLE 17-4: EXTERNAL CLOCK TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (Tcy) equals four times the input oscillator time-based period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max" cycle time limit is "DC" (no clock) for all devices.

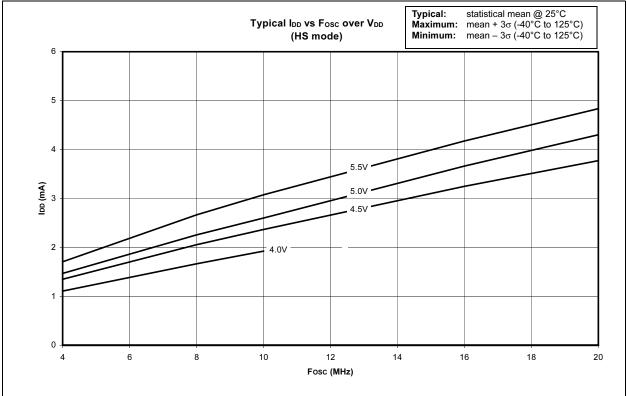

## 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

In some graphs or tables, the data presented is outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.