#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-04e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |

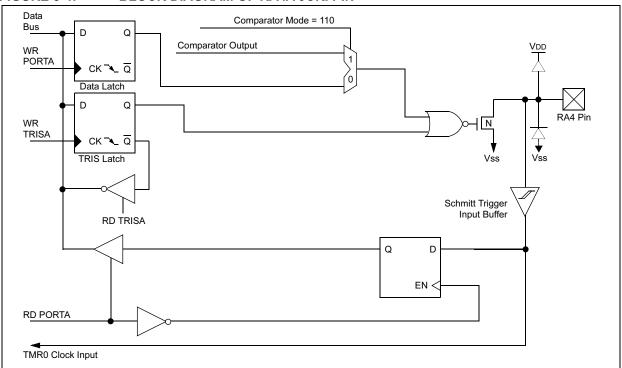

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |

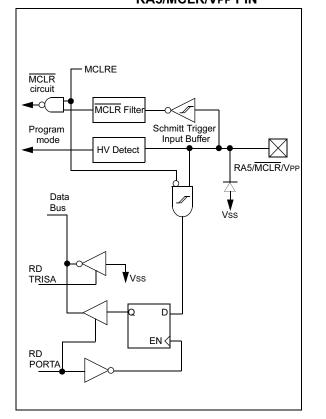

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |

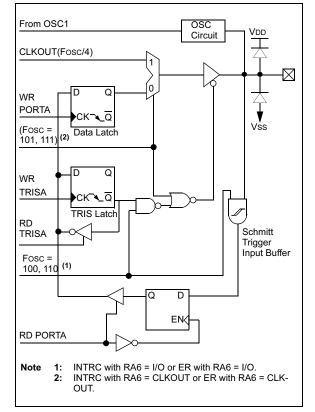

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

## TABLE 2-1:PIC16F62X PINOUT DESCRIPTION (CONTINUED)

| Name                                                  | Function | Input Type                    | Output Type | Description                                                                                                                                                                          |

|-------------------------------------------------------|----------|-------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB4/PGM                                               | RB4      | TTL                           | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                       |

|                                                       | PGM      | ST                            | _           | Low voltage programming input pin. Interrupt-<br>on-pin change. When low voltage program-<br>ming is enabled, the interrupt-on-pin change<br>and weak pull-up resistor are disabled. |

| RB5                                                   | RB5      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

| RB6/T1OSO/T1CKI/PGC                                   | RB6      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

|                                                       | T10SO    | —                             | XTAL        | Timer1 oscillator output.                                                                                                                                                            |

|                                                       | T1CKI    | ST                            | —           | Timer1 clock input.                                                                                                                                                                  |

|                                                       | PGC      | ST                            | _           | ICSP™ Programming Clock.                                                                                                                                                             |

| RB7/T1OSI/PGD                                         | RB7      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |

|                                                       | T1OSI    | XTAL                          | _           | Timer1 oscillator input. Wake-up from SLEEP<br>on pin change. Can be software programmed<br>for internal weak pull-up.                                                               |

|                                                       | PGD      | ST                            | CMOS        | ICSP Data I/O                                                                                                                                                                        |

| Vss                                                   | Vss      | Power                         | _           | Ground reference for logic and I/O pins                                                                                                                                              |

| Vdd                                                   | Vdd      | Power                         | —           | Positive supply for logic and I/O pins                                                                                                                                               |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | CMOS = CI<br>I = In<br>OD = O |             | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                               |

NOTES:

| Address | Name   | Bit 7            | Bit 6            | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|------------------|-------------|--------------|--------------|--------------|--------------|--------------|-----------------------------------------|--------------------|

| Bank 3  |        |                  |                  |             |              |              |              |              |              |                                         |                    |

| 180h    | INDF   | Addressin ister) | ig this location | n uses cont | ents of FSF  | R to address | s data mem   | ory (not a p | hysical reg- | XXXX XXXX                               | 25                 |

| 181h    | OPTION | RBPU             | INTEDG           | TOCS        | TOSE         | PSA          | PS2          | PS1          | PS0          | 1111 1111                               | 20                 |

| 182h    | PCL    | Program (        | Counter's (PC    | ) Least Sig | nificant Byt | e            |              |              |              | 0000 0000                               | 25                 |

| 183h    | STATUS | IRP              | RP1              | RP0         | TO           | PD           | Z            | DC           | С            | 0001 1xxx                               | 19                 |

| 184h    | FSR    | Indirect da      | ata memory a     | ddress poir | nter         | . –          | -            |              | 1-           | xxxx xxxx                               | 25                 |

| 185h    | _      | Unimplem         |                  |             |              |              |              |              |              | _                                       | _                  |

| 186h    | TRISB  | TRISB7           | TRISB6           | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | 1111 1111                               | 34                 |

| 187h    | _      | Unimplem         | nented           | •           |              | •            | •            |              |              | _                                       | —                  |

| 188h    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 189h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 18Ah    | PCLATH | _                | _                | _           | Write buff   | er for upper | 5 bits of pr | ogram cour   | iter         | 0 0000                                  | 25                 |

| 18Bh    | INTCON | GIE              | PEIE             | T0IE        | INTE         | RBIE         | TOIF         | INTF         | RBIF         | 0000 000x                               | 21                 |

| 18Ch    | _      | Unimplem         | nented           |             |              |              | •            |              |              | _                                       | _                  |

| 18Dh    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Eh    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Fh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 190h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 191h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 192h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 193h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 194h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 195h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 196h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 197h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 198h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 199h    | —      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 19Ah    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Bh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Ch    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Dh    | —      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 19Eh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Fh    | —      | Unimplem         | nented           |             |              |              |              |              |              | —                                       | —                  |

### TABLE 3-4: SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### PIR1 Register 3.2.2.5

This register contains interrupt flag bits.

| Note: | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of |

|-------|-------------------------------------------------------------------------------------------|

|       | 0                                                                                         |

|       | its corresponding enable bit or the global                                                |

|       | enable bit, GIE (INTCON<7>). User                                                         |

|       | software should ensure the appropriate                                                    |

|       | interrupt flag bits are clear prior to enabling                                           |

|       | an interrupt.                                                                             |

| REGISTER 3-5: | PIR1 REG | ISTER (AD | DRESS: | 0Ch) |  |

|---------------|----------|-----------|--------|------|--|

|               | R/W-0    | R/W-0     | R-0    | R-0  |  |

|       | R/W-0                                                                                                                                                | R/W-0                                                                                                | R-0                            | R-0                        | U-0                                 | R/W-0       | R/W-0          | R/W-0  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|-------------------------------------|-------------|----------------|--------|--|--|--|

|       | EEIF                                                                                                                                                 | CMIF                                                                                                 | RCIF                           | TXIF                       |                                     | CCP1IF      | TMR2IF         | TMR1IF |  |  |  |

|       | bit 7                                                                                                                                                |                                                                                                      |                                |                            |                                     | I           |                | bit 0  |  |  |  |

| bit 7 | EEIF: EEP                                                                                                                                            | ROM Write                                                                                            | Operation I                    | nterrupt Flag              | a bit                               |             |                |        |  |  |  |

|       | 1 = The wri                                                                                                                                          | ite operatior                                                                                        | n completed                    | l (must be c               | leared in softwa<br>has not been st |             |                |        |  |  |  |

| bit 6 | CMIF: Com                                                                                                                                            | parator Inte                                                                                         | errupt Flag b                  | oit                        |                                     |             |                |        |  |  |  |

|       | •                                                                                                                                                    | <ul> <li>1 = Comparator output has changed</li> <li>0 = Comparator output has not changed</li> </ul> |                                |                            |                                     |             |                |        |  |  |  |

| bit 5 | RCIF: USA                                                                                                                                            | RT Receive                                                                                           | Interrupt F                    | lag bit                    |                                     |             |                |        |  |  |  |

|       |                                                                                                                                                      |                                                                                                      | e buffer is f<br>e buffer is e |                            |                                     |             |                |        |  |  |  |

| bit 4 |                                                                                                                                                      |                                                                                                      |                                |                            |                                     |             |                |        |  |  |  |

| DIL 4 |                                                                                                                                                      |                                                                                                      | t Interrupt F<br>nit buffer is | -                          |                                     |             |                |        |  |  |  |

|       |                                                                                                                                                      |                                                                                                      | nit buffer is                  |                            |                                     |             |                |        |  |  |  |

| bit 3 | Unimplem                                                                                                                                             | ented: Rea                                                                                           | d as '0'                       |                            |                                     |             |                |        |  |  |  |

| bit 2 | CCP1IF: C                                                                                                                                            | CP1 Interru                                                                                          | pt Flag bit                    |                            |                                     |             |                |        |  |  |  |

|       | 0 <b>= No T</b>                                                                                                                                      | IR1 register<br>MR1 regist                                                                           | r capture oc<br>er capture c   |                            | at be cleared in                    | software)   |                |        |  |  |  |

|       |                                                                                                                                                      | IR1 register<br>MR1 registe                                                                          | •                              | natch occuri<br>match occu | red (must be cle<br>rred            | eared in so | ftware)        |        |  |  |  |

|       |                                                                                                                                                      | <u>-</u><br>in this mode                                                                             | 9                              |                            |                                     |             |                |        |  |  |  |

| bit 1 | TMR2IF: T                                                                                                                                            | MR2 to PR2                                                                                           | 2 Match Inte                   | errupt Flag b              | it                                  |             |                |        |  |  |  |

|       | 1 = TMR2 1                                                                                                                                           | o PR2 mate                                                                                           |                                | (must be cl                | eared in softwa                     | re)         |                |        |  |  |  |

| bit 0 | TMR1IF: T                                                                                                                                            | MR1 Overf                                                                                            | low Interrup                   | t Flag bit                 |                                     |             |                |        |  |  |  |

|       | <b>TMR1IF</b> : TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow |                                                                                                      |                                |                            |                                     |             |                |        |  |  |  |

|       | Legend:                                                                                                                                              |                                                                                                      |                                |                            |                                     |             |                |        |  |  |  |

|       | R = Reada                                                                                                                                            | ble bit                                                                                              | VV = V                         | Vritable bit               | U = Unimpl                          | emented b   | it, read as '( | )'     |  |  |  |

|       | -n = Value                                                                                                                                           | at POR                                                                                               | '1' = E                        | Bit is set                 | '0' = Bit is c                      | leared      | x = Bit is ur  | nknown |  |  |  |

NOTES:

## BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

FIGURE 5-6:

BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

## 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2).

In Asynchronous Counter mode, Timer1 can not be used as a time-base for capture or compare operations.

### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

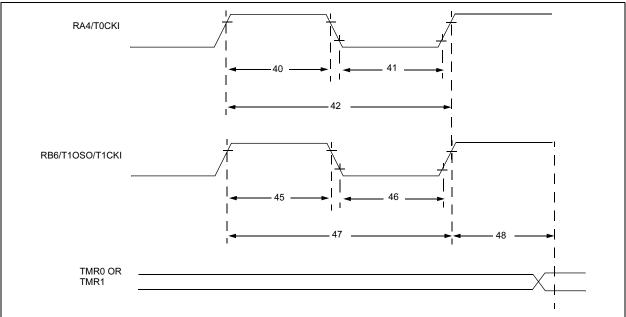

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high-time and low-time requirements. Refer to the appropriate Electrical Specifications section, Timing Parameters 45, 46, and 47.

### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

## EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVF TMR1H, W ;Read high byte

MOVWF TMPH

MOVF

TMR1L, W ;Read low byte

MOVWF TMPL

;

MOVF

TMR1H, W ;Read high byte

SUBWF

TMPH, W

;Sub 1st read

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

GOTO

CONTINUE ;Good 16-bit read

;

TMR1L may have rolled over between the read

;

; of the high and low bytes. Reading the high

; and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

MOVF

TMR1L, W

;Read low byte

MOVWF TMPL

;

; Re-enable the Interrupts (if required)

;Continue with your code

CONTINUE

```

## 9.6 Comparator Interrupts

The Comparator Interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the Comparator Interrupt Flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a   | change     | in  | the    | CMCON      | register  |

|-------|--------|------------|-----|--------|------------|-----------|

|       | (C10   | UT or C2   | OU  | T) sh  | ould occur | r when a  |

|       | read   | operation  | is  | being  | executed   | (start of |

|       | the C  | 2 cycle),  | the | en the | e CMIF (F  | PIR1<6>)  |

|       | interr | upt flag m | nay | not g  | et set.    |           |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 9.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes-up from SLEEP, the contents of the CMCON register are not affected.

# 9.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the Comparator module to be in the comparator RESET mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 9.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A source impedance of maximum 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| BAUD     | Fosc = 20 MHz |        | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|---------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD         | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615         | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230        | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878        | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818        | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636       | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250           | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625           | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250          | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 MHz |        | SPBRG              | 5.068 MHz | 5.068 MHz SPBRG |                    |          | 4 MHz   |                    |  |

|----------|-----------------|--------|--------------------|-----------|-----------------|--------------------|----------|---------|--------------------|--|

| RATE (K) | KBAUD           | ERROR  | value<br>(decimal) | KBAUD     | ERROR           | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |  |

| 9600     | 9.520           | -0.83% | 46                 | 9598.485  | 0.016%          | 32                 | 9615.385 | 0.160%  | 25                 |  |

| 19200    | 19.454          | +1.32% | 22                 | 18632.35  | -2.956%         | 16                 | 19230.77 | 0.160%  | 12                 |  |

| 38400    | 37.286          | -2.90% | 11                 | 39593.75  | 3.109%          | 7                  | 35714.29 | -6.994% | 6                  |  |

| 57600    | 55.930          | -2.90% | 7                  | 52791.67  | -8.348%         | 5                  | 62500    | 8.507%  | 3                  |  |

| 115200   | 111.860         | -2.90% | 3                  | 105583.3  | -8.348%         | 2                  | 125000   | 8.507%  | 1                  |  |

| 250000   | NA              | _      | _                  | 316750    | 26.700%         | 0                  | 250000   | 0.000%  | 0                  |  |

| 625000   | NA              | _      | _                  | NA        | _               | _                  | NA       | _       | _                  |  |

| 1250000  | NA              |        | —                  | NA        | —               | _                  | NA       | —       |                    |  |

| BAUD        | Fosc = 3.579 | 9 MHz    | SPBRG              | 1 MHz   |          | SPBRG              | 32.768 MHz |       | SPBRG              |

|-------------|--------------|----------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600        | 9725.543     | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200       | 18640.63     | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400       | 37281.25     | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600       | 55921.88     | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200      | 111243.8     | -2.913%  | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000      | 223687.5     | -10.525% | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000      | NA           | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000     | NA           | —        | —                  | NA      | —        | —                  | NA         | NA    | NA                 |

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on<br>all other<br>RESETS |

|---------|-------|------------------------------|-------|-------|-------|-------|--------|--------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF  | RCIF  | TXIF  |       | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA | SPEN                         | RX9   | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 -00x       | 0000 -00x                       |

| 1Ah     | RCREG | USART Receive Register       |       |       |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

| 8Ch     | PIE1  | EEIE                         | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA | CSRC                         | TX9   | TXEN  | SYNC  |       | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |       |       |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

## 14.5 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Detect (BOD)

### 14.5.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

## 14.5.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) timeout on power-up only, from POR or Brown-out Detect Reset. The PWRT operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. The PWRT should always be enabled when Brown-out Detect Reset is enabled. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 14.5.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

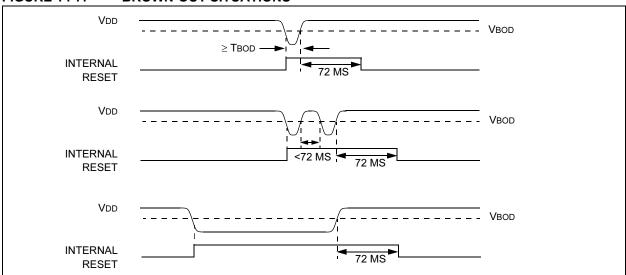

#### 14.5.4 BROWN-OUT DETECT (BOD) RESET

The PIC16F62X members have on-chip BOD circuitry. A configuration bit, BODEN, can disable (if clear/ programmed) or enable (if set) the BOD Reset circuitry. If VDD falls below VBOD for longer than TBOD, the brown-out situation will RESET the chip. A RESET is not guaranteed to occur if VDD falls below VBOD for shorter than TBOD. VBOD and TBOD are defined in Table 17-1 and Table 17-6, respectively.

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above VBOD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below VBOD while the Power-up Timer is running, the chip will go back into a Brown-out Detect Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Detect is enabled. Figure 14-7 shows typical Brown-out situations.

FIGURE 14-7: BROWN-OUT SITUATIONS

## 16.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

## 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

## 16.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

## 16.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

# 16.18 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

## 17.1 DC Characteristics: PIC16F62X-04 (Commercial, Industrial, Extended) PIC16F62X-20 (Commercial, Industrial, Extended) PIC16LF62X-04 (Commercial, Industrial)

| PIC16LF<br>(Comm                                                   | <b>62X-04</b><br>iercial, In | dustrial)                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |             |          |                                                                               |  |  |  |

|--------------------------------------------------------------------|------------------------------|-----------------------------------------------|------------------------------------------------------|------|-------------|----------|-------------------------------------------------------------------------------|--|--|--|

| PIC16F62X-04<br>PIC16F62X-20<br>(Commercial, Industrial, Extended) |                              |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |             |          |                                                                               |  |  |  |

| Param<br>No.                                                       | Sym                          | Characteristic/Device                         | Min                                                  | Тур† | Мах         | Units    | Conditions                                                                    |  |  |  |

|                                                                    | Vdd                          | Supply Voltage                                |                                                      |      |             |          |                                                                               |  |  |  |

| D001                                                               |                              | PIC16LF62X                                    | 2.0                                                  | _    | 5.5         | V        |                                                                               |  |  |  |

| D001                                                               |                              | PIC16F62X                                     | 3.0                                                  | _    | 5.5         | V        |                                                                               |  |  |  |

| D002                                                               | Vdr                          | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —                                                    | 1.5  | —           | V        | Device in SLEEP mode*                                                         |  |  |  |

| D003                                                               | VPOR                         | VDD Start Voltage<br>to ensure Power-on Reset | —                                                    | Vss  | —           | V        | See section on Power-on Reset for details                                     |  |  |  |

| D004                                                               | SVDD                         | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05                                                 | —    | —           | V/ms     | See section on Power-on Reset for details*                                    |  |  |  |

| D005                                                               | VBOD                         | Brown-out Detect Voltage                      | 3.65<br>3.65                                         | 4.0  | 4.35<br>4.4 | V<br>V   | BODEN configuration bit is set<br>BODEN configuration bit is set,<br>Extended |  |  |  |

|                                                                    | IDD                          | Supply Current <sup>(2), (5)</sup>            |                                                      |      |             |          | •                                                                             |  |  |  |

| D010                                                               |                              | PIC16LF62X                                    | _                                                    | 0.30 | 0.6         | mA       | Fosc = 4.0 MHz, VDD = 2.0 <sup>(5)</sup>                                      |  |  |  |

| D010                                                               |                              |                                               | —                                                    | 1.10 | 2.0         | mA       | Fosc = 4.0 MHz, VDD = 5.5*                                                    |  |  |  |

| D013                                                               |                              |                                               | —                                                    | 4.0  | 7.0         | mA       | Fosc = 20.0 MHz, VDD = 5.5                                                    |  |  |  |

|                                                                    |                              |                                               | _                                                    | 3.80 | 6.0<br>2.0  | mA<br>mA | Fosc = 20.0 MHz, VDD = 4.5*<br>Fosc = 10.0 MHz, VDD = 3.0 <sup>(6)</sup>      |  |  |  |

|                                                                    |                              |                                               | _                                                    | 20   | 30          | μΑ       | Fosc = 32  kHz,  VDD = 3.0  M                                                 |  |  |  |

| D010                                                               |                              | PIC16F62X                                     | _                                                    | 0.60 | 0.7         | mA       | Fosc = 4.0 MHz, VDD = 3.0                                                     |  |  |  |

|                                                                    |                              |                                               | _                                                    | 1.10 | 2.0         | mA       | Fosc = 4.0 MHz, VDD = 5.5*                                                    |  |  |  |

| D013                                                               |                              |                                               | —                                                    | 4.0  | 7.0         | mA       | Fosc = 20.0 MHz, VDD = 5.5                                                    |  |  |  |

|                                                                    |                              |                                               | —                                                    | 3.80 | 6.0         | mA       | Fosc = 20.0 MHz, VDD = $4.5^*$                                                |  |  |  |

| D014                                                               |                              |                                               | —                                                    | 20   | 2.0<br>30   | mA       | Fosc = 10.0 MHz, VDD = $3.0^{(6)}$                                            |  |  |  |

| D014                                                               |                              |                                               |                                                      | 20   | 30          | μA       | Fosc = 32 kHz, VDD = 3.0                                                      |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active Operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

**3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

5: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

6: Commercial temperature only.

## TABLE 17-1: COMPARATOR SPECIFICATIONS

|              | Operating Conditions: 3.0V < VDD <5.5V, -40°C < TA < +125°C, unless otherwise stated. |        |     |      |            |          |                   |  |  |  |

|--------------|---------------------------------------------------------------------------------------|--------|-----|------|------------|----------|-------------------|--|--|--|

| Param<br>No. | Characteristics                                                                       | Sym    | Min | Тур  | Мах        | Units    | Comments          |  |  |  |

| D300         | Input offset voltage                                                                  | VIOFF  | _   | ±5.0 | ±10        | mV       |                   |  |  |  |

| D301*        | Input Common mode voltage                                                             | VICM   | 0   | —    | Vdd - 1.5  | V        |                   |  |  |  |

| D302*        | Common Mode Rejection Ratio                                                           | CMRR   | 55  | —    | —          | db       |                   |  |  |  |

| 300*<br>300A | Response Time <sup>(1)</sup>                                                          | TRESP  |     | 150  | 400<br>600 | ns<br>ns | 16F62X<br>16LF62X |  |  |  |

| 301          | Comparator Mode Change to<br>Output Valid*                                            | TMC2OV | _   | -    | 10         | μS       |                   |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

## TABLE 17-2: VOLTAGE REFERENCE SPECIFICATIONS

|             | Operating Conditions: 3.0V < VDD < 5.5V, -40°C < TA < +125°C, unless otherwise stated. |      |        |     |        |       |                      |  |  |  |

|-------------|----------------------------------------------------------------------------------------|------|--------|-----|--------|-------|----------------------|--|--|--|

| Spec<br>No. | Characteristics                                                                        | Sym  | Min    | Тур | Мах    | Units | Comments             |  |  |  |

| D310        | Resolution                                                                             | VRES | VDD/24 | —   | Vdd/32 | LSb   |                      |  |  |  |

| D311        | Absolute Accuracy                                                                      | VRaa | _      | _   | 1/4    | LSb   | Low Range (VRR = 1)  |  |  |  |

|             |                                                                                        |      | —      |     | 1/2    | LSb   | High Range (VRR = 0) |  |  |  |

| D312*       | Unit Resistor Value (R)                                                                | VRur | —      | 2k  | —      | Ω     |                      |  |  |  |

| 310*        | Settling Time <sup>(1)</sup>                                                           | Tset | _      | —   | 10     | μs    |                      |  |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

| Param<br>No. | Sym                                                                                        |                               | Characteristic                      |                | Min                                 | Тур† | Max                                | Units | Conditions                         |

|--------------|--------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------|----------------|-------------------------------------|------|------------------------------------|-------|------------------------------------|

| 40*          | Tt0H                                                                                       | T0CKI High Puls               | e Width                             | No Prescaler   | 0.5Tcy + 20                         | —    |                                    | ns    |                                    |

|              |                                                                                            |                               |                                     | With Prescaler | 10                                  | —    | _                                  | ns    |                                    |

| 41*          | TtOL                                                                                       | T0CKI Low Pulse               | e Width                             | No Prescaler   | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |                                                                                            |                               |                                     | With Prescaler | 10                                  | -    | —                                  | ns    |                                    |

| 42*          | Tt0P                                                                                       | T0CKI Period                  | Greater of:<br><u>Tcy + 40</u><br>N | _              | —                                   | ns   | N = prescale value<br>(2, 4,, 256) |       |                                    |

| 45*          | Tt1H                                                                                       | T1CKI High                    | Synchronous, N                      | lo Prescaler   | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |                                                                                            | Time                          | Synchronous,                        | 16F62X         | 15                                  | -    | —                                  | ns    |                                    |

|              |                                                                                            |                               | with Prescaler                      | 16LF62X        | 25                                  | —    | —                                  | ns    |                                    |

|              |                                                                                            |                               | Asynchronous                        | 16F62X         | 30                                  | _    | -                                  | ns    |                                    |

|              |                                                                                            |                               |                                     | 16LF62X        | 50                                  | —    | _                                  | ns    |                                    |

| 46*          | Tt1L                                                                                       | T1CKI Low Time                | Synchronous, No Prescaler           |                | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |                                                                                            |                               | Synchronous,                        | 16F62X         | 15                                  | —    | —                                  | ns    |                                    |

|              |                                                                                            |                               | with Prescaler                      | 16LF62X        | 25                                  | —    | —                                  | ns    |                                    |

|              |                                                                                            |                               | Asynchronous                        | 16F62X         | 30                                  | -    | Ι                                  | ns    |                                    |

|              |                                                                                            |                               |                                     | 16LF62X        | 50                                  | —    | —                                  | ns    |                                    |

| 47*          | Tt1P                                                                                       | T1CKI input<br>period         | Synchronous                         | 16F62X         | Greater of:<br><u>Tcy + 40</u><br>N | —    | —                                  | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |                                                                                            |                               |                                     | 16LF62X        | Greater of:<br><u>Tcy + 40</u><br>N | _    | —                                  | —     |                                    |

|              |                                                                                            |                               | Asynchronous                        | 16F62X         | 60                                  | _    | -                                  | ns    |                                    |

|              |                                                                                            |                               |                                     | 16LF62X        | 100                                 | -    | —                                  | ns    |                                    |

|              | Ft1 Timer1 oscillator input frequency range<br>(oscillator enabled by setting bit T1OSCEN) |                               |                                     |                | DC                                  | -    | 200                                | kHz   |                                    |

| 48           | TCKEZtmr1                                                                                  | Delay from exter<br>increment | 2Tosc                               | -              | 7Tosc                               | _    |                                    |       |                                    |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

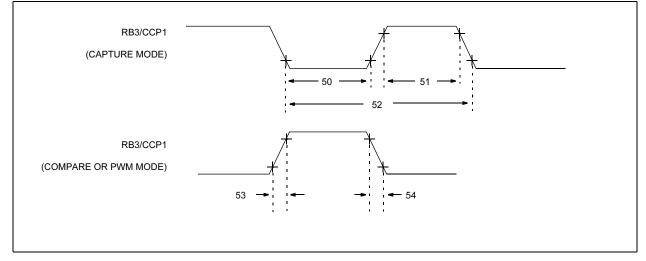

#### FIGURE 17-11: **CAPTURE/COMPARE/PWM TIMINGS**

Note: The graphs and tables provided in this section are for design guidance and are not tested.

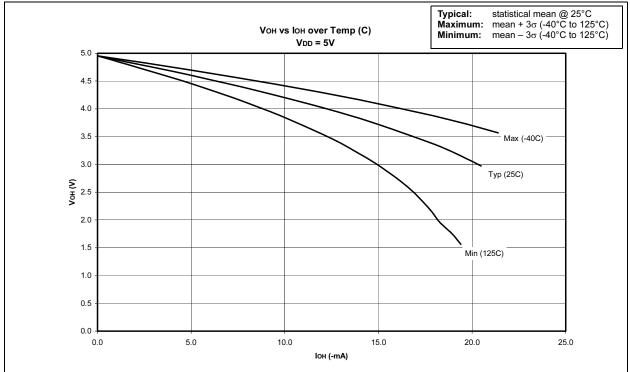

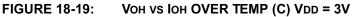

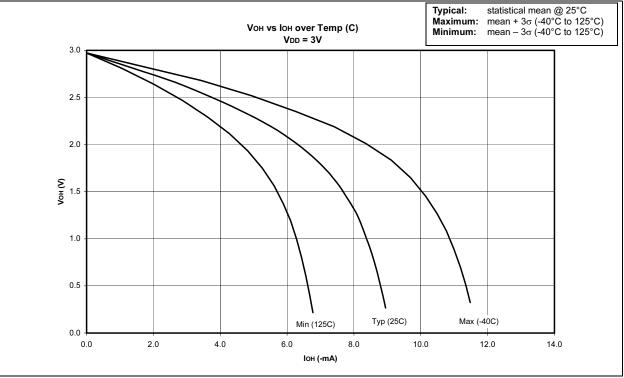

## FIGURE 18-18: VOH VS IOH OVER TEMP (C) VDD = 5V

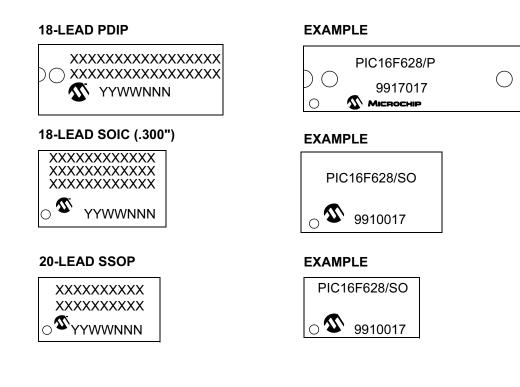

# **19.0 PACKAGING INFORMATION**

## **19.1** Package Marking Information

| Legend: | MMM | Microchip part number information                                                                                                                                                   |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | XXX | Customer specific information(1)                                                                                                                                                    |

|         | YY  | Year code (last 2 digits of calendar year)                                                                                                                                          |

|         | WW  | Week code (week of January 1 is week '01')                                                                                                                                          |

|         | NNN | Alphanumeric traceability code                                                                                                                                                      |

| Note:   |     | vent the full Microchip part number cannot be marked on one line, it will be carried<br>he next line thus limiting the number of available characters for customer specific<br>ion. |