Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | General Description                                                    | 5     |

|------|------------------------------------------------------------------------|-------|

| 2.0  | General Description PIC16F62X Device Varieties                         | 7     |

| 3.0  | Architectural Overview                                                 | 9     |

| 4.0  | Memory Organization                                                    | 15    |

| 5.0  | I/O Ports                                                              | 29    |

| 6.0  | Timer0 Module                                                          | 43    |

| 7.0  | Timer1 Module                                                          | 46    |

| 8.0  | Timer2 Module                                                          | 50    |

| 9.0  | Comparator Module<br>Voltage Reference Module                          | 53    |

| 10.0 | Voltage Reference Module                                               | 59    |

| 11.0 | Capture/Compare/PWM (CCP) Module                                       | 61    |

| 12.0 | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) Module | 67    |

| 13.0 | Data EEPROM Memory                                                     | 87    |

| 14.0 | Special Features of the CPU                                            | 91    |

| 15.0 | Instruction Set Summary                                                | . 107 |

| 16.0 | Development Support                                                    | . 121 |

| 17.0 | Electrical Specifications                                              | . 127 |

| 18.0 | DC and AC Characteristics Graphs and Tables                            | . 143 |

| 19.0 | Packaging Information                                                  | . 157 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

# 2.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16F62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The Table below lists program memory (FLASH, Data and EEPROM).

TABLE 2-1: DEVICE DESCRIPTION

|            | Memory           |             |                |  |  |  |  |

|------------|------------------|-------------|----------------|--|--|--|--|

| Device     | FLASH<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC16F627  | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16F628  | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF627 | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF628 | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

The PIC16F62X can directly or indirectly address its register files or data memory. All Special Function registers, including the program counter, are mapped in the data memory. The PIC16F62X have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any Addressing mode. This symmetrical nature, and lack of 'special optimal situations' make programming with the PIC16F62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bit wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 2-1, and a description of the device pins in Table 2-1.

Two types of data memory are provided on the PIC16F62X devices. Non-volatile EEPROM data memory is provided for long term storage of data such as calibration values, lookup table data, and any other data which may require periodic updating in the field. This data is not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. It is lost when power is removed.

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7                       | Bit 6                        | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0       | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|-----------------------------|------------------------------|-----------------|----------------|---------------|----------------|--------------|-------------|-----------------------------------------|--------------------|

| Bank 0  |         |                             |                              |                 |                |               |                |              |             |                                         |                    |

| 00h     | INDF    | Addressir                   | ng this locatio              | n uses conte    | nts of FSR to  | address data  | a memory (n    | ot a physica | l register) | xxxx xxxx                               | 25                 |

| 01h     | TMR0    | Timer0 M                    | odule's Regis                | ter             |                |               |                |              | • /         | XXXX XXXX                               | 43                 |

| 02h     | PCL     | Program                     | Counter's (PC                | ) Least Sign    | ificant Byte   |               |                |              |             | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP                         | RP1                          | RP0             | TO             | PD            | Z              | DC           | С           | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d                  | ata memory a                 | ddress point    | er             |               |                |              | -           | xxxx xxxx                               | 25                 |

| 05h     | PORTA   | RA7                         | RA6                          | RA5             | RA4            | RA3           | RA2            | RA1          | RA0         | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7                         | RB6                          | RB5             | RB4            | RB3           | RB2            | RB1          | RB0         | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | _                                       |                    |

| 08h     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | _                                       |                    |

| 09h     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | _                                       |                    |

| 0Ah     | PCLATH  | _                           | _                            | _               | Write buffer   | for upper 5 b | oits of progra | im counter   |             | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE                         | PEIE                         | T0IE            | INTE           | RBIE          | T0IF           | INTF         | RBIF        | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF                        | CMIF                         | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF       | TMR1IF      | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen                    | Unimplemented                |                 |                |               |                |              |             | —                                       | _                  |

| 0Eh     | TMR1L   | Holding r                   | egister for the              | Least Signif    | icant Byte of  | the 16-bit TN | 1R1            |              |             | XXXX XXXX                               | 46                 |

| 0Fh     | TMR1H   | Holding r                   | egister for the              | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |              |             | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _                           | _                            | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS       | TMR10N      | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo                     | odule's registe              | r               |                |               |                |              |             | 0000 0000                               | 50                 |

| 12h     | T2CON   | _                           | TOUTPS3                      | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1      | T2CKPS0     | -000 0000                               | 50                 |

| 13h     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | _                                       | _                  |

| 14h     | —       | Unimplen                    | nented                       |                 |                |               |                |              |             | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0                   | Compare/PWN                  | /I register (LS | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0                   | Compare/PWN                  | /I register (M  | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _                           | —                            | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1       | CCP1M0      | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN                        | RX9                          | SREN            | CREN           | ADEN          | FERR           | OERR         | RX9D        | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T                     | USART Transmit data register |                 |                |               |                |              |             | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART Receive data register |                              |                 |                |               |                |              | 0000 0000   | 77                                      |                    |

| 1Bh     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | —                                       | _                  |

| 1Ch     | _       | Unimplen                    | nented                       |                 |                |               |                |              |             | —                                       | _                  |

| 1Dh     | —       | Unimplen                    | nented                       |                 |                |               |                |              |             | —                                       | —                  |

| 1Eh     | —       | Unimplen                    | nented                       | _               | 1              | 1             |                |              | 1           | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT                       | C10UT                        | C2INV           | C1INV          | CIS           | CM2            | CM1          | CM0         | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

## 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on Bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on Bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., Bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if Bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,~{\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings:PORTB<7:4> Inputs

;

;

; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-up and are not ;connected to other circuitry ;

| BCF STATUS, RPO ;                                                                                              |                                                 | PORT latchPORT Pins |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|

| BCF PORTB, /;01pp pppp 11pp pppBSF STATUS, RP0;BCF TRISB, 7;10pp pppp 11pp pppBCF TRISB, 6;10pp pppp 10pp pppp | BCF PORTB, 7<br>BSF STATUS, RP0<br>BCF TRISB, 7 |                     |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

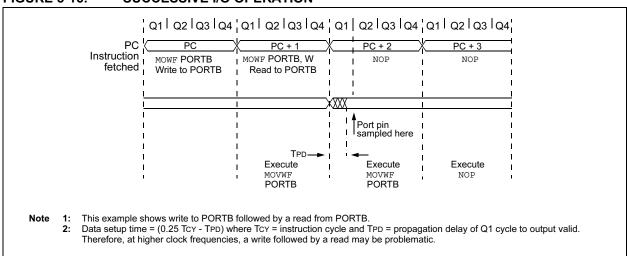

# 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-16: SUCCESSIVE I/O OPERATION

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information available in the PICmicro™ Mid Pange MCLL Eamily Reference

PICmicro™ Mid-Range MCU Family Reference Manual, DS31010A.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

# 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-7.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). Use the instruction sequences, shown in Example 6-1, when changing the prescaler assignment from Timer0 to WDT, to avoid an unintended device RESET.

#### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF    | STATUS, RPO | ;Skip if already in<br>;Bank 0 |

|--------|-------------|--------------------------------|

| CLRWDT |             | ;Clear WDT                     |

|        |             | •                              |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler        |

| BSF    | STATUS, RPO | ;Bank 1                        |

| MOVLW  | '00101111'b | ;These 3 lines                 |

|        |             | ;(5, 6, 7)                     |

| MOVWF  | OPTION_REG  | ;are required only             |

|        |             | ;if desired PS<2:0>            |

|        |             | ;are                           |

| CLRWDT |             | ;000 or 001                    |

| MOVLW  | '00101xxx'b | ;Set Postscaler to             |

| MOVWF  | OPTION_REG  | ;desired WDT rate              |

| BCF    | STATUS, RPO | ;Return to Bank 0              |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                           | ;Clear WDT and<br>;prescaler                              |

|--------------|---------------------------|-----------------------------------------------------------|

| BSF          | STATUS, RPO               |                                                           |

| MOVLW        | b'xxxx0xxx'               | ;Select TMR0, new<br>;prescale value and<br>;clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS, RP0 |                                                           |

| Address               | Name                  | Bit 7    | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------------------|-----------------------|----------|-------------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h                   | TMR0                  | Timer0 m | odule regis | ster   |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE      | PEIE        | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h, 181h             | OPTION <sup>(2)</sup> | RBPU     | INTEDG      | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h                   | TRISA                 | TRISA7   | TRISA6      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**REGISTERS ASSOCIATED WITH TIMER0**

**Note 1:** Shaded bits are not used by TMR0 module.

**TABLE 6-1**:

2: Option is referred by OPTION REG in MPLAB.

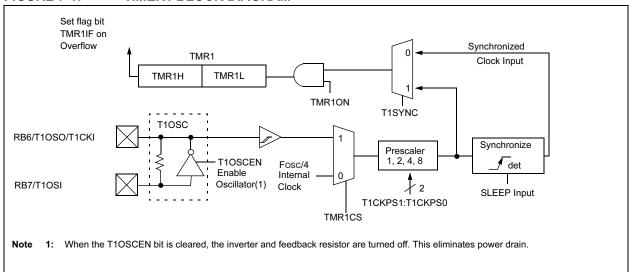

# 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

## 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

## FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

# 9.6 Comparator Interrupts

The Comparator Interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the Comparator Interrupt Flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a                                   | change     | in  | the   | CMCON      | register  |  |  |

|-------|----------------------------------------|------------|-----|-------|------------|-----------|--|--|

|       | (C10                                   | UT or C2   | OU  | T) sh | ould occur | r when a  |  |  |

|       | read                                   | operation  | is  | being | executed   | (start of |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>) |            |     |       |            |           |  |  |

|       | interr                                 | upt flag m | nay | not g | et set.    |           |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 9.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes-up from SLEEP, the contents of the CMCON register are not affected.

# 9.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the Comparator module to be in the comparator RESET mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 9.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A source impedance of maximum 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

Timer Resource

Timer1

Timer1

Timer2

**CCP MODE - TIMER**

RESOURCE

# 11.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 11-1 shows the timer resources of the CCP Module modes.

#### CCP1 Module

bit 5-4

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

# REGISTER 11-1: CCP1CON REGISTER (ADDRESS: 17h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | CCP1X | CCP1Y | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

**TABLE 11-1:**

**CCP Mode**

Capture

Compare

PWM

bit 7-6 Unimplemented: Read as '0'

CCP1X:CCP1Y: PWM Least Significant bits

Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

#### bit 3-0 CCP1M3:CCP1M0: CCPx Mode Select bits

- 0000 = Capture/Compare/PWM off (resets CCP1 module)

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, set output on match (CCP1IF bit is set)

- 1001 = Compare mode, clear output on match (CCP1IF bit is set)

- 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected)

- 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1

- 11xx = PWM mode

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### © 2003 Microchip Technology Inc.

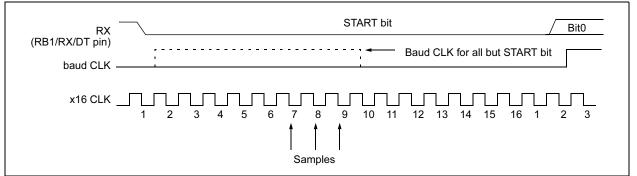

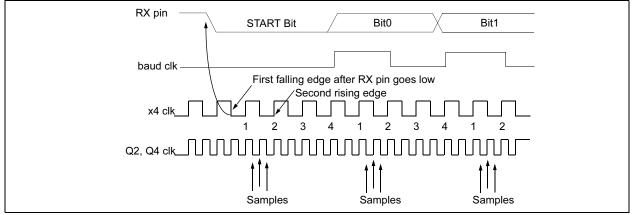

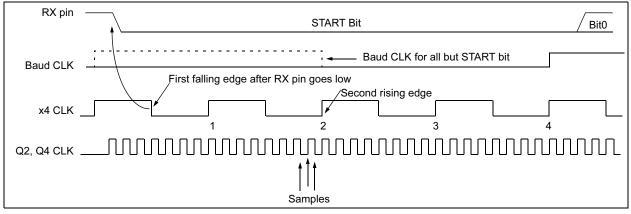

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

## FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

## FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

## FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

NOTES:

# 14.2 Oscillator Configurations

#### 14.2.1 OSCILLATOR TYPES

The PIC16F62X can be operated in eight different oscillator options. The user can program three configuration bits (FOSC2 thru FOSC0) to select one of these eight modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- ER External Resistor (2 modes)

- INTRC Internal Resistor/Capacitor (2 modes)

- EC External Clock In

# 14.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

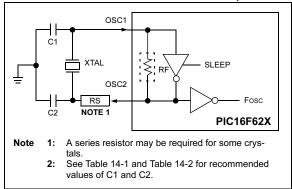

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 14-1). The PIC16F62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 14-4).

#### FIGURE 14-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

# TABLE 14-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| F       |                               |                                         |                                         |  |  |  |  |  |

|---------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Mode    | Freq                          | OSC1(C1)                                | OSC2(C2)                                |  |  |  |  |  |

| XT      | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |  |

| HS      | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |  |  |

| Note 1: |                               |                                         |                                         |  |  |  |  |  |

#### TABLE 14-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

components

its own characteristics, the user should consult the res-

onator manufacturer for appropriate values of external

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                    | OSC1(C1)    | OSC2(C2)     |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--|

| LP      | 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 - 100 pF | 68 - 100 pF  |  |

|         | 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |  |

| ХТ      | 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 - 150 pF | 150 - 200 pF |  |

|         | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 - 30 pF  | 15 - 30 pF   |  |

|         | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 - 30 pF  | 15 - 30 pF   |  |

| HS      | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 - 30 pF  | 15 - 30 pF   |  |

|         | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |

|         | 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |

| Note 1: | Higher capacitance increases the stability of the oscilla-<br>tor but also increases the start-up time. These values<br>are for design guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid overdriving crystals<br>with low drive level specification. Since each crystal<br>has its own characteristics, the user should consult the<br>crystal manufacturer for appropriate values of external<br>components. |             |              |  |

#### 14.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used, or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 14-2 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

## 14.5 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Detect (BOD)

#### 14.5.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 14.5.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) timeout on power-up only, from POR or Brown-out Detect Reset. The PWRT operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. The PWRT should always be enabled when Brown-out Detect Reset is enabled. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 14.5.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

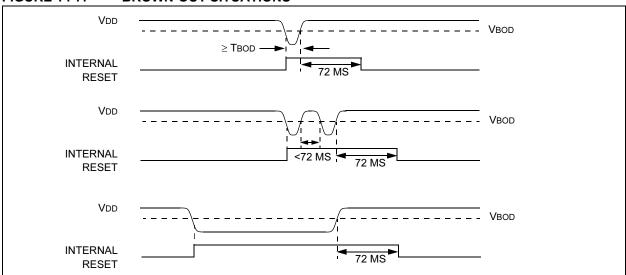

#### 14.5.4 BROWN-OUT DETECT (BOD) RESET

The PIC16F62X members have on-chip BOD circuitry. A configuration bit, BODEN, can disable (if clear/ programmed) or enable (if set) the BOD Reset circuitry. If VDD falls below VBOD for longer than TBOD, the brown-out situation will RESET the chip. A RESET is not guaranteed to occur if VDD falls below VBOD for shorter than TBOD. VBOD and TBOD are defined in Table 17-1 and Table 17-6, respectively.

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above VBOD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below VBOD while the Power-up Timer is running, the chip will go back into a Brown-out Detect Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Detect is enabled. Figure 14-7 shows typical Brown-out situations.

FIGURE 14-7: BROWN-OUT SITUATIONS

## 14.6 Interrupts

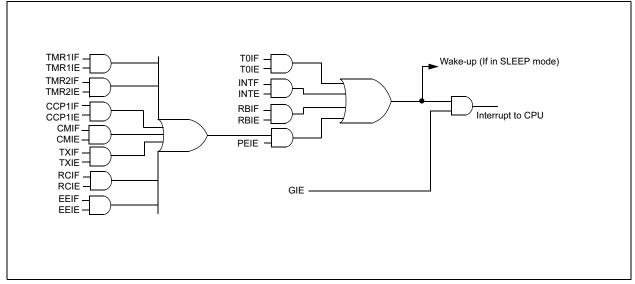

The PIC16F62X has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB7:RB4)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- EEPROM

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- **Note 1:** Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

## FIGURE 14-14: INTERRUPT LOGIC

# 16.0 DEVELOPMENT SUPPORT

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB C30 C Compiler

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- MPLAB dsPIC30 Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM.net<sup>™</sup> Demonstration Board

- PICDEM 2 Plus Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- PICDEM 18R Demonstration Board

- PICDEM LIN Demonstration Board

- PICDEM USB Demonstration Board

- Evaluation Kits

- KEELOQ®

- PICDEM MSC

- microID®

- CAN

- PowerSmart®

- Analog

## 16.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor with color coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High level source code debugging

- Mouse over variable inspection

- Extensive on-line help

- The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files (assembly or C)

- absolute listing file (mixed assembly and C)

- machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost effective simulators, through low cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increasing flexibility and power.

## 16.2 MPASM Assembler

The MPASM assembler is a full-featured, universal macro assembler for all PICmicro MCUs.

The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contains source lines and generated machine code and COFF files for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects

- · User defined macros to streamline assembly code

- · Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 17.1 DC Characteristics: PIC16F62X-04 (Commercial, Industrial, Extended) PIC16F62X-20 (Commercial, Industrial, Extended) PIC16LF62X-04 (Commercial, Industrial)

| PIC16LF62X-04<br>(Commercial, Industrial)                          |                                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                             |                                                                                                                                                                                                                                                     |                              |                           |                      |                                                                                    |

|--------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|----------------------|------------------------------------------------------------------------------------|

| PIC16F62X-04<br>PIC16F62X-20<br>(Commercial, Industrial, Extended) |                                             |                                                                                                                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial and $0^{\circ}C \le Ta \le +70^{\circ}C$ for commercial and $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |                              |                           |                      |                                                                                    |

| Param<br>No.                                                       | Sym                                         | Characteristic/Device                                                                                                                                            | Min                                                                                                                                                                                                                                                 | Тур†                         | Мах                       | Units                | Conditions                                                                         |

|                                                                    | IPD Power Down Current* <sup>(2), (3)</sup> |                                                                                                                                                                  |                                                                                                                                                                                                                                                     |                              |                           |                      |                                                                                    |

| D020                                                               |                                             | PIC16LF62X                                                                                                                                                       | _                                                                                                                                                                                                                                                   | 0.20<br>0.20                 | 2.0<br>2.2                | μΑ<br>μΑ             | VDD = 2.0<br>VDD = 5.5                                                             |

| D020                                                               |                                             | PIC16F62X                                                                                                                                                        |                                                                                                                                                                                                                                                     | 0.20<br>0.20<br>0.20<br>2.70 | 2.2<br>5.0<br>9.0<br>15.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0<br>VDD = 4.5*<br>VDD = 5.5<br>VDD = 5.5 Extended                         |

| D023                                                               | ΔIWDT<br>ΔIBOD<br>ΔICOMP<br>ΔIVREF          | WDT Current <sup>(4)</sup><br>Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup><br>VREF Current <sup>(4)</sup> | <br>                                                                                                                                                                                                                                                | 6.0<br>75<br>30              | 15<br>125<br>50<br>135    | μΑ<br>μΑ<br>μΑ       | $\frac{V_{DD}}{BOD} = 3.0V$<br>BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V |

| Daga                                                               | ∆Iwdt                                       | WDT Current <sup>(4)</sup>                                                                                                                                       | _                                                                                                                                                                                                                                                   | 6.0                          | 20<br>25                  | μΑ<br>μΑ             | VDD = 4.0V, Commercial,<br>Industrial<br>VDD = 4.0V, Extended                      |

| D023                                                               |                                             | Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup>                                                              | _                                                                                                                                                                                                                                                   | 75<br>30                     | 125<br>50                 | μΑ<br>μΑ             | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                              |

|                                                                    | $\Delta$ IVREF                              | VREF Current <sup>(4)</sup>                                                                                                                                      | —                                                                                                                                                                                                                                                   |                              | 135                       | μA                   | VDD = 4.0V                                                                         |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

- 4: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 5: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

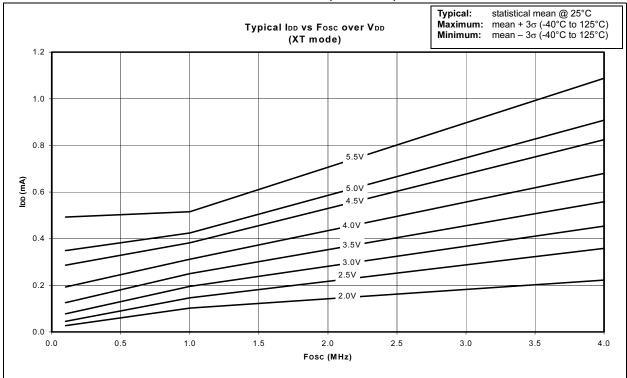

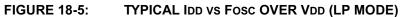

#### FIGURE 18-4: TYPICAL IDD vs Fosc OVER VDD (XT MODE)

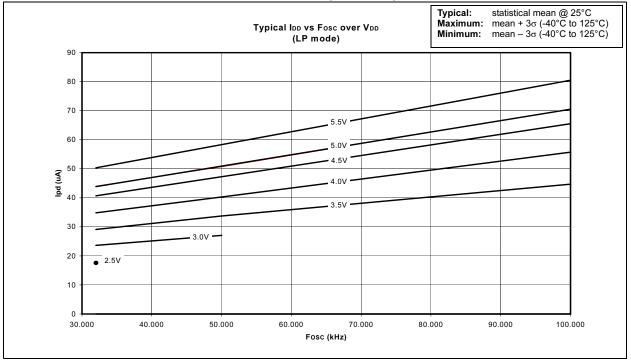

# **19.0 PACKAGING INFORMATION**

# **19.1** Package Marking Information

| Legend: MMMMicrochip part number informationXXXCustomer specific information(1)YYYear code (last 2 digits of calendar year) |     | Microchip part number information                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             |     | Customer specific information(1)                                                                                                                                                   |

|                                                                                                                             |     | Year code (last 2 digits of calendar year)                                                                                                                                         |

|                                                                                                                             | WW  | Week code (week of January 1 is week '01')                                                                                                                                         |

|                                                                                                                             | NNN | Alphanumeric traceability code                                                                                                                                                     |

| Note:                                                                                                                       |     | ent the full Microchip part number cannot be marked on one line, it will be carried<br>ne next line thus limiting the number of available characters for customer specific<br>ion. |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

| MOVLW                    |     |

|--------------------------|-----|

| MOVWF                    | 116 |

| NOP                      |     |

| OPTION                   |     |

| RETFIE                   | 116 |

| RETLW                    |     |

| RETURN                   |     |

| RLF                      |     |

| RRF                      |     |

| SLEEP                    |     |

| SUBLW                    |     |

| SUBWF                    |     |

| SWAPF                    | 119 |

| TRIS                     | 119 |

| XORLW                    | 120 |

| XORWF                    | 120 |

| Instruction Set Summary  | 107 |

| INT Interrupt            | 102 |

| INTCON Register          | 21  |

| Interrupt Sources        |     |

| Capture Complete (CCP)   | 62  |

| Compare Complete (CCP)   | 63  |

| TMR2 to PR2 Match (PWM)  | 64  |

| Interrupts               | 101 |

| Interrupts, Enable Bits  |     |

| CCP1 Enable (CCP1IE Bit) | 62  |

| Interrupts, Flag Bits    |     |

| CCP1 Flag (CCP1IF Bit)   | 62  |

| IORLW Instruction        | 115 |

| IORWF Instruction        |     |

# Μ

| Memory Organization                             |          |

|-------------------------------------------------|----------|

| Data EEPROM Memory                              |          |

| MOVF Instruction                                |          |

| MOVLW Instruction                               | 115      |

| MOVWF Instruction                               | 116      |

| MPLAB C17 and MPLAB C18 C Compilers             | 122      |

| MPLAB ICD In-Circuit Debugger                   | 123      |

| MPLAB ICE High Performance Universal In-Circuit | Emulator |

| with MPLAB IDE                                  | 123      |

| MPLAB Integrated Development Environment Softw  | vare 121 |

| MPLINK Object Linker/MPLIB Object Librarian     | 122      |

|                                                 |          |

# Ν

# 0

| OPTION Instruction              |  |

|---------------------------------|--|

| OPTION Register                 |  |

| Oscillator Configurations       |  |

| Oscillator Start-up Timer (OST) |  |

| Output of TMR2.                 |  |

# Ρ

| 157   |

|-------|

| 157   |

| 25    |

| 24    |

| 24    |

| 124   |

| 124   |

| 124   |

| r 123 |

| 22    |

|       |

| Pin Functions                           |       |

|-----------------------------------------|-------|

| RC6/TX/CK                               | 67–84 |

| RC7/RX/DT                               | 67–84 |

| PIR1                                    | 23    |

| PIR1 Register                           | 23    |

| Port RB Interrupt                       |       |

| PORTA                                   | 29    |

| PORTB                                   | 34    |

| Power Control/Status Register (PCON)    |       |

| Power-Down Mode (SLEEP)                 |       |

| Power-On Reset (POR)                    |       |

| Power-up Timer (PWRT)                   |       |

| PR2 Register                            | 50    |

| Prescaler                               | 44    |

| Prescaler, Capture                      | 62    |

| Prescaler, Timer2                       | 65    |

| PRO MATE II Universal Device Programmer | 123   |

| Program Memory Organization             |       |

| PROTECTION                              |       |

| PWM (CCP Module)                        |       |

| Block Diagram                           |       |

| CCPR1H:CCPR1L Registers                 |       |

| Duty Cycle                              | 65    |

| Example Frequencies/Resolutions         |       |

| Output Diagram                          | 64    |

| Period                                  | 64    |

| Set-Up for PWM Operation                |       |

| TMR2 to PR2 Match                       |       |

|                                         |       |

# Q

| Q-Clock                                   | 65 |

|-------------------------------------------|----|

| Quick-Turnaround-Production (QTP) Devices | 5  |

# R

| RC Oscillator      |     |

|--------------------|-----|

| Registers          |     |

| Maps               |     |

| PIC16C76           |     |

| PIC16C77           |     |

| Reset              |     |

| RETFIE Instruction | 116 |

| RETLW Instruction  | 117 |

| RETURN Instruction | 117 |

| RLF Instruction    | 117 |

| RRF Instruction    | 118 |

# s

| Serial Communication Interface (SCI) Module, See | USART   |

|--------------------------------------------------|---------|

| Serialized Quick-Turnaround-Production (SQTP) De | vices 5 |

| SLEEP Instruction                                | 118     |

| Software Simulator (MPLAB SIM)                   | 122     |

| Special                                          | 95      |

| Special Event Trigger. See Compare               |         |

| Special Features of the CPU                      | 91      |

| Special Function Registers                       | 15      |

| Stack                                            | 25      |

| Status Register                                  | 19      |

| SUBLW Instruction                                | 118     |

| SUBWF Instruction                                | 119     |

| SWAPF Instruction                                | 119     |

# т

| T1CKPS0 bit |    |

|-------------|----|

| T1CKPS1 bit |    |

| T1OSCEN bit | 46 |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                                             | Technical Publications Manager                                                          | Total Pages Sent                                       |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| RE:                                             | Reader Response                                                                         |                                                        |  |

| Fron                                            | ו: Name                                                                                 |                                                        |  |

|                                                 | Company                                                                                 |                                                        |  |

|                                                 | Address                                                                                 |                                                        |  |

|                                                 | City / State / ZIP / Country                                                            |                                                        |  |

|                                                 | Telephone: ()                                                                           | FAX: ()                                                |  |

| Application (optional):                         |                                                                                         |                                                        |  |

| Would you like a reply?YN                       |                                                                                         |                                                        |  |

| Device: PIC16F62X Literature Number: DS40300C   |                                                                                         |                                                        |  |

| Questions:                                      |                                                                                         |                                                        |  |

| 1. What are the best features of this document? |                                                                                         |                                                        |  |

|                                                 |                                                                                         |                                                        |  |

| -                                               |                                                                                         |                                                        |  |

| 2.                                              | 2. How does this document meet your hardware and software development needs?            |                                                        |  |