Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

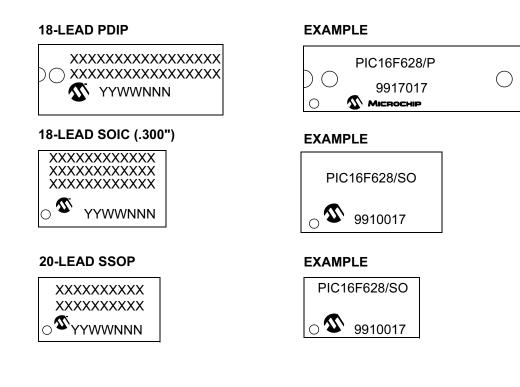

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-04i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | General Description                                                    | 5     |

|------|------------------------------------------------------------------------|-------|

| 2.0  | General Description PIC16F62X Device Varieties                         | 7     |

| 3.0  | Architectural Overview                                                 | 9     |

| 4.0  | Memory Organization                                                    | 15    |

| 5.0  | I/O Ports                                                              | 29    |

| 6.0  | Timer0 Module                                                          | 43    |

| 7.0  | Timer1 Module                                                          | 46    |

| 8.0  | Timer2 Module                                                          | 50    |

| 9.0  | Comparator Module<br>Voltage Reference Module                          | 53    |

| 10.0 | Voltage Reference Module                                               | 59    |

| 11.0 | Capture/Compare/PWM (CCP) Module                                       | 61    |

| 12.0 | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) Module | 67    |

| 13.0 | Data EEPROM Memory                                                     | 87    |

| 14.0 | Special Features of the CPU                                            | 91    |

| 15.0 | Instruction Set Summary                                                | . 107 |

| 16.0 | Development Support                                                    | . 121 |

| 17.0 | Electrical Specifications                                              | . 127 |

| 18.0 | DC and AC Characteristics Graphs and Tables                            | . 143 |

| 19.0 | Packaging Information                                                  | . 157 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

## 4.0 GENERAL DESCRIPTION

The PIC16F62X are 18-Pin FLASH-based members of the versatile PIC16CXX family of low cost, high performance, CMOS, fully static, 8-bit microcontrollers.

All PICmicro<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F62X have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16F62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F62X has eight oscillator configurations. The single pin ER oscillator provides a low cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, INTRC is a self-contained internal oscillator. The HS is for High Speed crystals. The EC mode is for an external clock source. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external interrupts, internal interrupts, and RESETS.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

Table 4-1 shows the features of the PIC16F62X midrange microcontroller families.

A simplified block diagram of the PIC16F62X is shown in Figure 2.1.

The PIC16F62X series fits in applications ranging from battery chargers to low power remote sensors. The FLASH technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F62X very versatile.

## 4.1 Development Support

The PIC16F62X family is supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627                        | PIC16F628                        | PIC16LF627                       | PIC16LF628                       |

|-------------|--------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 4                                | 4                                |

|             | FLASH Program Memory (words)         | 1024                             | 2048                             | 1024                             | 2048                             |

| Memory      | RAM Data Memory (bytes)              | 224                              | 224                              | 224                              | 224                              |

|             | EEPROM Data Memory (bytes)           | 128                              | 128                              | 128                              | 128                              |

|             | Timer Module(s)                      | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 |

|             | Comparator(s)                        | 2                                | 2                                | 2                                | 2                                |

| Peripherals | Capture/Compare/PWM modules          | 1                                | 1                                | 1                                | 1                                |

|             | Serial Communications                | USART                            | USART                            | USART                            | USART                            |

|             | Internal Voltage Reference           | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Interrupt Sources                    | 10                               | 10                               | 10                               | 10                               |

|             | I/O Pins                             | 16                               | 16                               | 16                               | 16                               |

| Features    | Voltage Range (Volts)                | 3.0-5.5                          | 3.0-5.5                          | 2.0-5.5                          | 2.0-5.5                          |

|             | Brown-out Detect                     | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Packages                             | 18-pin DIP, SOIC,<br>20-pin SSOP |

## TABLE 4-1:PIC16F62X FAMILY OF DEVICES

All PICmicro® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F62X Family devices use serial programming with clock pin RB6 and data pin RB7.

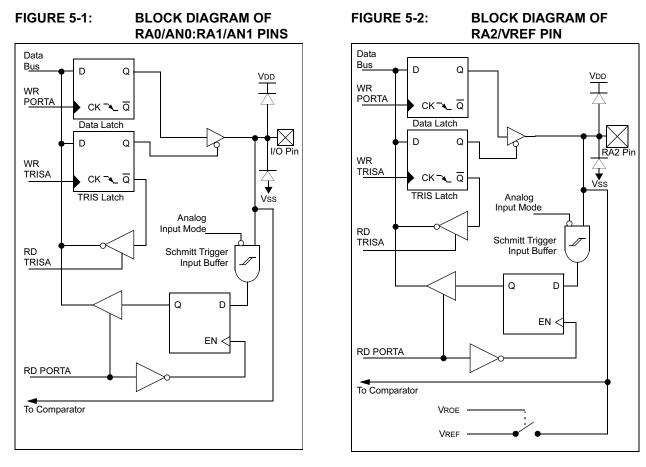

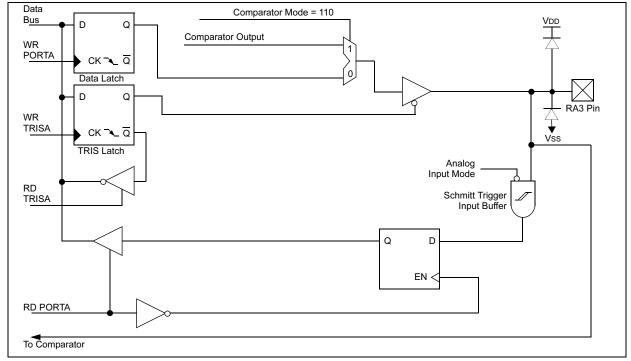

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3 PIN

© 2003 Microchip Technology Inc.

## 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information available in the PICmicro™ Mid Pange MCLL Eamily Reference

PICmicro™ Mid-Range MCU Family Reference Manual, DS31010A.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

## 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

## 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-7.

| <b>REGISTER 8-1:</b> | T2CO       | N: TIMER C    |              | REGISTER     | (ADDRESS:   | 12h)   |         |         |

|----------------------|------------|---------------|--------------|--------------|-------------|--------|---------|---------|

|                      | U-0        | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |

|                      | _          | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |

|                      | bit 7      |               |              |              |             |        |         | bit 0   |

|                      |            |               |              |              |             |        |         |         |

| bit 7                | Unimplem   | ented: Read   | as '0'       |              |             |        |         |         |

| bit 6-3              | TOUTPS3:   | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |

|                      | 0000 = 1:1 | Postscale V   | alue         |              |             |        |         |         |

|                      | 0001 = 1:2 | Postscale V   | alue         |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | 1111 = 1:1 | 6 Postscale   |              |              |             |        |         |         |

|                      |            |               |              |              |             |        |         |         |

| bit 2                | TMR2ON:    | Timer2 On bi  | it           |              |             |        |         |         |

|                      | 1 = Timer2 | is on         |              |              |             |        |         |         |

|                      | 0 = Timer2 | is off        |              |              |             |        |         |         |

| bit 1-0              | T2CKPS1:   | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |

|                      | 00 = 1:1 P | rescaler Valu | е            |              |             |        |         |         |

|                      |            | rescaler Valu | -            |              |             |        |         |         |

|                      | 1x = 1:16  | Prescaler Val | ue           |              |             |        |         |         |

|                      | <b></b>    |               |              |              |             |        |         | 1       |

|                      | Legend:    |               |              |              |             |        |         |         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

## TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE         | PEIE           | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF        | CMIF           | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE        | CMIE           | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod  | lule's registe | r       |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

## 11.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 11.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

## 11.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

| Address                   | Name    | Bit 7                               | Bit 6    | Bit 5       | Bit 4         | Bit 3          | Bit 2       | Bit 1      | Bit 0  | Value on<br>POR |      |      | e on<br>ther<br>ETS |

|---------------------------|---------|-------------------------------------|----------|-------------|---------------|----------------|-------------|------------|--------|-----------------|------|------|---------------------|

| 0Bh/8Bh/<br>10Bh/<br>18Bh | INTCON  | GIE                                 | PEIE     | TOIE        | INTE          | RBIE           | TOIF        | INTF       | RBIF   | 0000            | 000x | 0000 | 000u                |

| 0Ch                       | PIR1    | EEIF                                | CMIF     | RCIF        | TXIF          | _              | CCP1IF      | TMR2IF     | TMR1IF | 0000            | -000 | 0000 | -000                |

| 8Ch                       | PIE1    | EEIE                                | CMIF     | RCIE        | TXIE          | _              | CCP1IE      | TMR2IE     | TMR1IE | 0000            | -000 | 0000 | -000                |

| 87h                       | TRISB   | PORTB                               | Data Dii | rection Reg | ister         |                |             |            |        | 1111            | 1111 | 1111 | 1111                |

| 0Eh                       | TMR1L   | Holding                             | register | for the Lea | st Significar | nt Byte of the | e 16-bit TM | R1 registe | r      | xxxx            | xxxx | uuuu | uuuu                |

| 0Fh                       | TMR1H   | Holding                             | register | for the Mos | t Significan  | t Byte of the  | 16-bit TM   | R1register |        | xxxx            | xxxx | uuuu | uuuu                |

| 10h                       | T1CON   | _                                   |          | T1CKPS1     | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS     | TMR10N | 00              | 0000 | uu   | uuuu                |

| 15h                       | CCPR1L  | Capture/Compare/PWM register1 (LSB) |          |             |               |                |             |            |        | xxxx            | xxxx | uuuu | uuuu                |

| 16h                       | CCPR1H  | Capture/Compare/PWM register1 (MSB) |          |             |               |                |             |            |        | xxxx            | xxxx | uuuu | uuuu                |

| 17h                       | CCP1CON | _                                   | _        | CCP1X       | CCP1Y         | CCP1M3         | CCP1M2      | CCP1M1     | CCP1M0 | 00              | 0000 | 00   | 0000                |

#### TABLE 11-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

| BAUD     | Fosc = 20 M | lHz    | SPBRG              | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          |        | _                  | NA     |        | _                  | NA     |        | _                  |

| 1.2      | NA          | _      | —                  | NA     | _      |                    | NA     | —      |                    |

| 2.4      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| 9.6      | NA          | _      | _                  | NA     | _      | _                  | 9.766  | +1.73% | 255                |

| 19.2     | 19.53       | +1.73% | 255                | 19.23  | +0.16% | 207                | 19.23  | +0.16% | 129                |

| 76.8     | 76.92       | +0.16% | 64                 | 76.92  | +0.16% | 51                 | 75.76  | -1.36% | 32                 |

| 96       | 96.15       | +0.16% | 51                 | 95.24  | -0.79% | 41                 | 96.15  | +0.16% | 25                 |

| 300      | 294.1       | -1.96  | 16                 | 307.69 | +2.56% | 12                 | 312.5  | +4.17% | 7                  |

| 500      | 500         | 0      | 9                  | 500    | 0      | 7                  | 500    | 0      | 4                  |

| HIGH     | 5000        | _      | 0                  | 4000   | _      | 0                  | 2500   | _      | 0                  |

| LOW      | 19.53       | _      | 255                | 15.625 | _      | 255                | 9.766  | _      | 255                |

#### TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |                                         | SPBRG | 4 MHz  |                    | SPBRG |

|----------|-------------|---------|--------------------|------------|-----------------------------------------|-------|--------|--------------------|-------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | value<br>KBAUD ERROR (decimal) KBAUD EF |       | ERROR  | value<br>(decimal) |       |

| 0.3      | NA          | _       | _                  | NA         | _                                       | _     | NA     | _                  | _     |

| 1.2      | NA          | _       | _                  | NA         | _                                       | _     | NA     | _                  | _     |

| 2.4      | NA          |         |                    | NA         | _                                       |       | NA     |                    | _     |

| 9.6      | 9.622       | +0.23%  | 185                | 9.6        | 0                                       | 131   | 9.615  | +0.16%             | 103   |

| 19.2     | 19.24       | +0.23%  | 92                 | 19.2       | 0                                       | 65    | 19.231 | +0.16%             | 51    |

| 76.8     | 77.82       | +1.32   | 22                 | 79.2       | +3.13%                                  | 15    | 75.923 | +0.16%             | 12    |

| 96       | 94.20       | -1.88   | 18                 | 97.48      | +1.54%                                  | 12    | 1000   | +4.17%             | 9     |

| 300      | 298.3       | -0.57   | 5                  | 316.8      | 5.60%                                   | 3     | NA     |                    | —     |

| 500      | NA          | _       | _                  | NA         |                                         | _     | NA     | _                  | _     |

| HIGH     | 1789.8      |         | 0                  | 1267       | _                                       | 0     | 100    | _                  | 0     |

| LOW      | 6.991       |         | 255                | 4.950      | _                                       | 255   | 3.906  | _                  | 255   |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |        | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|--------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) |

| 0.3         | NA           |          | _                  | NA     |        |                    | 0.303      | +1.14% | 26                 |

| 1.2         | NA           |          | —                  | 1.202  | +0.16% | 207                | 1.170      | -2.48% | 6                  |

| 2.4         | NA           | _        | _                  | 2.404  | +0.16% | 103                | NA         | _      | _                  |

| 9.6         | 9.622        | +0.23%   | 92                 | 9.615  | +0.16% | 25                 | NA         | _      | _                  |

| 19.2        | 19.04        | -0.83%   | 46                 | 19.24  | +0.16% | 12                 | NA         | _      | —                  |

| 76.8        | 74.57        | -2.90%   | 11                 | 83.34  | +8.51% | 2                  | NA         | —      | _                  |

| 96          | 99.43        | +3.57%   | 8                  | NA     |        | _                  | NA         | _      | —                  |

| 300         | 298.3        | 0.57%    | 2                  | NA     | _      | _                  | NA         | _      | _                  |

| 500         | NA           | _        | —                  | NA     |        |                    |            | —      | —                  |

| HIGH        | 894.9        | _        | 0                  | 250    |        | 0                  | 8.192      | _      | 0                  |

| LOW         | 3.496        | _        | 255                | 0.9766 |        | 255                | 0.032      | _      | 255                |

## 12.4 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RB2/TX/CK and RB1/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART Transmitter Block Diagram is shown in Figure 12-5. The heart of the transmitter is the Transmit (serial) Shift register (TSR). The Shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will RESET only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will RESET the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set, during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however is not RESET although it is disconnected from the pins. In order to RESET the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from Hi-impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

## PIC16F62X

| REGISTER 13-2: | EECON1 F                   | REGISTER                                    | (ADDRES        | SS: 9Ch)     |                       |              |                |           |

|----------------|----------------------------|---------------------------------------------|----------------|--------------|-----------------------|--------------|----------------|-----------|

|                | U-0                        | U-0                                         | U-0            | U-0          | R/W-x                 | R/W-0        | R/S-0          | R/S-x     |

|                | —                          | _                                           | _              | —            | WRERR                 | WREN         | WR             | RD        |

|                | bit 7                      |                                             |                |              |                       |              |                | bit 0     |

| bit 7-4        | Unimpleme                  | ented: Read                                 | d as '0'       |              |                       |              |                |           |

| bit 3          | WRERR: E                   | EPROM Er                                    | ror Flag bit   |              |                       |              |                |           |

|                | normal                     | operation is<br>operation o<br>te operatior | r BOD Res      | et)          | d (any MCLR R         | eset, any \  | WDT Reset      | during    |

| bit 2          | WREN: EE                   | PROM Write                                  | e Enable bi    | t            |                       |              |                |           |

|                | 1 = Allows<br>0 = Inhibits |                                             |                | ROM          |                       |              |                |           |

| bit 1          | WR: Write                  | Control bit                                 |                |              |                       |              |                |           |

|                | can onl                    | y be set (no                                | ot cleared) ii |              | y hardware onc<br>ete | e write is c | complete. T    | he WR bit |

| bit 0          | RD: Read (                 | Control bit                                 |                |              |                       |              |                |           |

|                | can onl                    |                                             | ot cleared) ii | n software). | e cycle. RD is c      | leared in h  | ardware. Tl    | ne RD bit |

|                | Legend:                    |                                             |                |              |                       |              |                |           |

|                | R = Readal                 | ole bit                                     | W = V          | Vritable bit | U = Unimple           | emented bi   | it, read as '( | D'        |

|                | -n = Value a               | at POR                                      | '1' = B        | lit is set   | '0' = Bit is c        | leared       | x = Bit is ur  | nknown    |

#### TABLE 13-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7  | Bit 6                     | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other<br>RESETS |

|---------|-----------------------|--------|---------------------------|----------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 9Ah     | EEDATA                | EEPROM | data regi                 | ster     |       |       |       |       |       | XXXX XXXX                     | uuuu uuuu                       |

| 9Bh     | EEADR                 | EEPROM | address                   | register |       |       |       |       |       | XXXX XXXX                     | uuuu uuuu                       |

| 9Ch     | EECON1                | _      | _                         |          | _     | WRERR | WREN  | WR    | RD    | x000                          | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM | EEPROM control register 2 |          |       |       |       |       |       |                               |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM.

**Note 1:** EECON2 is not a physical register

## 14.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16F62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Brown-out Reset (BOD)

- 7. Interrupts

- 8. Watchdog Timer (WDT)

- 9. SLEEP

- 10. Code protection

- 11. ID Locations

- 12. In-circuit Serial Programming

The PIC16F62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a Brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The ER oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special configuration memory space (2000h – 3FFFh), which can be accessed only during programming. See Programming Specification.

## 14.12 In-Circuit Serial Programming

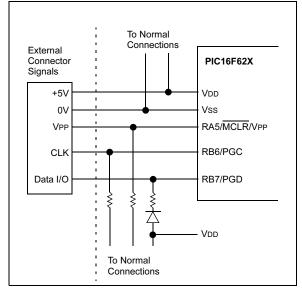

The PIC16F62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 14-18.

#### FIGURE 14-18: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## 14.13 Low Voltage Programming

The LVP bit of the configuration word, enables the low voltage programming. This mode allows the microcontroller to be programmed via ICSP using only a 5V source. This mode removes the requirement of VIHH to be placed on the MCLR pin. The LVP bit is normally erased to '1', which enables the low voltage programming. In this mode, the RB4/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. The device will enter Programming mode when a '1' is placed on the RB4/PGM pin. The HV Programming mode is still available by placing VIHH on the MCLR pin.

- Note 1: While in this mode, the RB4 pin can no longer be used as a general purpose I/O pin.

- 2: VDD must be 5.0V <u>+</u>10% during erase/ program operations while in low voltage Programming mode.

If Low voltage Programming mode is not used, the LVP bit can be programmed to a '0', and RB4/PGM becomes a digital I/O pin. To program the device, VIHH must be placed onto MCLR during programming. The LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit cannot be programmed when programming is entered with RB4/PGM.

It should be noted, that once the LVP bit is programmed to 0, High voltage Programming mode can be used to program the device.

|                  | •                                                                                                                          |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| ADDLW            | Add Literal and W                                                                                                          |  |  |

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |  |  |

| Words:           | 1                                                                                                                          |  |  |

| Cycles:          | 1                                                                                                                          |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |

| ANDLW                                                                                                    | AND Literal with W                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                                                                                  | [ <i>label</i> ] ANDLW k                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Operands:                                                                                                | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Operation:                                                                                               | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Encoding:                                                                                                | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Description:                                                                                             | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                                                                  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Example                                                                                                  | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                          | W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                                                                          | W = 0x03                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| ANDWF                                                                                                    | AND W with f                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| ANDWF<br>Syntax:                                                                                         | AND W with f [ label ] ANDWF f,d                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Syntax:                                                                                                  | [ <i>label</i> ] ANDWF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Syntax:<br>Operands:                                                                                     | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                                                                                                                   |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                             |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} ANDWF  f,d$ $0 \le f \le 127$ $d \in [0,1]$ $(W) .AND. (f) \rightarrow (dest)$ $Z$ $00 \qquad 0101  dfff \qquad ffff$                                                                                                                                                                                                                                              |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register                                                                                                                                                                                                                                    |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 \qquad 0101  dfff \qquad ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register \\ \hline \end{tabular}$                                                |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .AND. (f) $\rightarrow$ (dest) Z $00 \qquad 0101  dfff  ffff$ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                                                             |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. \\ 1 \\ \end{bmatrix}$                                                    |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF & REG1, 1 \\ Before Instruction \\ W &= 0x17 \\ \end{bmatrix}$ |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ \hline AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 1 1 ANDWF REG1, 1 Before Instruction W = 0x17 REG1 = 0xC2$          |  |  |

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |

| Operation:       | $(W) + (f) \rightarrow (dest)$                                                                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |

| Description:     | Add the contents of the W regis-<br>ter with register 'f'. If 'd' is 0 the<br>result is stored in the W register.<br>If 'd' is 1 the result is stored back<br>in register 'f'. |

| Words:           | 1                                                                                                                                                                              |

| Cycles:          | 1                                                                                                                                                                              |

| Example          | ADDWF REG1, 0                                                                                                                                                                  |

|                  | Before Instruction<br>W = 0x17<br>REG1 = 0xC2<br>After Instruction<br>W = 0xD9<br>REG1 = 0xC2<br>Z = 0<br>C = 0<br>DC = 0                                                      |

# PIC16F62X

| MOVWF            | Move W to f                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                              |

| Operands:        | $0 \leq f \leq 127$                                                                                   |

| Operation:       | $(W) \rightarrow (f)$                                                                                 |

| Status Affected: | None                                                                                                  |

| Encoding:        | 00 0000 1fff ffff                                                                                     |

| Description:     | Move data from W register to register 'f'.                                                            |

| Words:           | 1                                                                                                     |

| Cycles:          | 1                                                                                                     |

| Example          | MOVWF REG1                                                                                            |

|                  | Before Instruction<br>REG1 = $0xFF$<br>W = $0x4F$<br>After Instruction<br>REG1 = $0x4F$<br>W = $0x4F$ |

| OPTION           | Load Op                                                                                                                                                                                                                                                                                               | otion Re | gister |      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                                                                        |          |        |      |

| Operands:        | None                                                                                                                                                                                                                                                                                                  |          |        |      |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                                                              |          |        |      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |          |        |      |

| Encoding:        | 00                                                                                                                                                                                                                                                                                                    | 0000     | 0110   | 0010 |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a<br>readable/writable register, the<br>user can directly address it. Using<br>only register instruction such as<br>MOVWF. |          |        |      |

| Words:           | 1                                                                                                                                                                                                                                                                                                     |          |        |      |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                     |          |        |      |

| Example          |                                                                                                                                                                                                                                                                                                       |          |        |      |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                                                                                                                                                |          |        |      |

| NOP              | No Operation |        |      |      |

|------------------|--------------|--------|------|------|

| Syntax:          | [label] NOP  |        |      |      |

| Operands:        | None         |        |      |      |

| Operation:       | No operation |        |      |      |

| Status Affected: | None         |        |      |      |

| Encoding:        | 00           | 0000   | 0xx0 | 0000 |

| Description:     | No oper      | ation. | •    |      |

| Words:           | 1            |        |      |      |

| Cycles:          | 1            |        |      |      |

| Example          | NOP          |        |      |      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                 |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                      |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                         |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                     |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS)<br>is loaded in the PC. Interrupts<br>are enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-<br>cycle instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                                     |  |  |

| Cycles:          | 2                                                                                                                                                                                                                     |  |  |

| Example          | RETFIE                                                                                                                                                                                                                |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                |  |  |

## 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

## 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

## 16.7 MPLAB SIM Software Simulator