Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

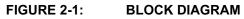

# 1.0 PIC16F62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F62X Product Identification System section (Page 167) at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 1.1 FLASH Devices

FLASH devices can be erased and reprogrammed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically-erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus, or PRO MATE<sup>®</sup> II programmers.

# 1.2 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 1.3 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

# PIC16F62X

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7      | Bit 6                                                              | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0       | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|--------------------------------------------------------------------|-----------------|----------------|---------------|----------------|--------------|-------------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                                                                    |                 |                |               |                |              |             |                                         |                    |

| 00h     | INDF    | Addressir  | ng this locatio                                                    | n uses conte    | nts of FSR to  | address data  | a memory (n    | ot a physica | l register) | xxxx xxxx                               | 25                 |

| 01h     | TMR0    | Timer0 M   | odule's Regis                                                      | ter             |                |               |                |              | • /         | xxxx xxxx                               | 43                 |

| 02h     | PCL     | Program    | Counter's (PC                                                      | ) Least Sign    | ificant Byte   |               |                |              |             | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP        | RP1                                                                | RP0             | TO             | PD            | Z              | DC           | С           | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d | direct data memory address pointer                                 |                 |                |               |                |              |             |                                         | 25                 |

| 05h     | PORTA   | RA7        | RA6                                                                | RA5             | RA4            | RA3           | RA2            | RA1          | RA0         | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7        | RB6                                                                | RB5             | RB4            | RB3           | RB2            | RB1          | RB0         | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       |                    |

| 08h     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       |                    |

| 09h     | _       | Unimplen   | implemented                                                        |                 |                |               |                |              |             | _                                       |                    |

| 0Ah     | PCLATH  | _          | _                                                                  | _               | Write buffer   | for upper 5 b | oits of progra | im counter   |             | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE        | PEIE                                                               | T0IE            | INTE           | RBIE          | T0IF           | INTF         | RBIF        | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF       | CMIF                                                               | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF       | TMR1IF      | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen   | nented                                                             |                 | —              | _             |                |              |             |                                         |                    |

| 0Eh     | TMR1L   | Holding r  | Holding register for the Least Significant Byte of the 16-bit TMR1 |                 |                |               |                |              |             |                                         | 46                 |

| 0Fh     | TMR1H   | Holding r  | egister for the                                                    | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |              |             | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _          | _                                                                  | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS       | TMR10N      | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo    | odule's registe                                                    | r               |                |               |                |              |             | 0000 0000                               | 50                 |

| 12h     | T2CON   | _          | TOUTPS3                                                            | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1      | T2CKPS0     | -000 0000                               | 50                 |

| 13h     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       | _                  |

| 14h     | —       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0  | Compare/PWN                                                        | /I register (LS | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0  | Compare/PWN                                                        | /I register (M  | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _          | —                                                                  | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1       | CCP1M0      | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN       | RX9                                                                | SREN            | CREN           | ADEN          | FERR           | OERR         | RX9D        | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T    | ransmit data                                                       | register        |                |               |                |              |             | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART F    | USART Receive data register                                        |                 |                |               |                |              |             | 0000 0000                               | 77                 |

| 1Bh     | _       | Unimplen   | Unimplemented —                                                    |                 |                |               |                |              |             | _                                       |                    |

| 1Ch     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | —                                       | _                  |

| 1Dh     | —       | Unimplen   | nented                                                             |                 |                |               |                |              |             | —                                       | —                  |

| 1Eh     | —       | Unimplen   | nented                                                             |                 | 1              | 1             |                |              | 1           | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT      | C10UT                                                              | C2INV           | C1INV          | CIS           | CM2            | CM1          | CM0         | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

| Address | Name   | Bit 7            | Bit 6            | Bit 5       | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|------------------|-------------|--------------|--------------|--------------|--------------|--------------|-----------------------------------------|--------------------|

| Bank 3  |        |                  |                  |             |              |              |              |              |              |                                         |                    |

| 180h    | INDF   | Addressin ister) | ig this location | n uses cont | ents of FSF  | R to address | s data mem   | ory (not a p | hysical reg- | XXXX XXXX                               | 25                 |

| 181h    | OPTION | RBPU             | INTEDG           | TOCS        | TOSE         | PSA          | PS2          | PS1          | PS0          | 1111 1111                               | 20                 |

| 182h    | PCL    | Program (        | Counter's (PC    | ) Least Sig | nificant Byt | e            |              |              |              | 0000 0000                               | 25                 |

| 183h    | STATUS | IRP              | RP1              | RP0         | TO           | PD           | Z            | DC           | С            | 0001 1xxx                               | 19                 |

| 184h    | FSR    | Indirect da      | ata memory a     | ddress poir | nter         | . –          | -            |              | 1-           | xxxx xxxx                               | 25                 |

| 185h    | _      | Unimplem         |                  |             |              |              |              |              |              | _                                       | _                  |

| 186h    | TRISB  | TRISB7           | TRISB6           | TRISB5      | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | 1111 1111                               | 34                 |

| 187h    | _      | Unimplem         | nented           | •           |              | •            | •            |              |              | _                                       | —                  |

| 188h    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 189h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 18Ah    | PCLATH | _                | _                | _           | Write buff   | er for upper | 5 bits of pr | ogram cour   | iter         | 0 0000                                  | 25                 |

| 18Bh    | INTCON | GIE              | PEIE             | T0IE        | INTE         | RBIE         | TOIF         | INTF         | RBIF         | 0000 000x                               | 21                 |

| 18Ch    | _      | Unimplem         | Unimplemented    |             |              |              |              |              |              |                                         | _                  |

| 18Dh    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Eh    |        | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 18Fh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 190h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 191h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 192h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 193h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 194h    | —      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 195h    | _      | Unimplem         | nented           |             |              |              |              |              |              |                                         | _                  |

| 196h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 197h    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | —                  |

| 198h    | _      | Unimplem         | Unimplemented    |             |              |              |              |              |              |                                         | —                  |

| 199h    | —      | Unimplem         | Unimplemented    |             |              |              |              |              |              |                                         | —                  |

| 19Ah    | _      | Unimplem         | Unimplemented    |             |              |              |              |              |              | _                                       |                    |

| 19Bh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Ch    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Dh    | —      | Unimplem         | nented           |             |              |              |              |              |              | _                                       | _                  |

| 19Eh    | _      | Unimplem         | nented           |             |              |              |              |              |              | _                                       |                    |

| 19Fh    | —      | Unimplem         | nented           |             |              |              |              |              |              | —                                       | —                  |

#### TABLE 3-4: SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### PIR1 Register 3.2.2.5

This register contains interrupt flag bits.

| Note: | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of |

|-------|-------------------------------------------------------------------------------------------|

|       | 0                                                                                         |

|       | its corresponding enable bit or the global                                                |

|       | enable bit, GIE (INTCON<7>). User                                                         |

|       | software should ensure the appropriate                                                    |

|       | interrupt flag bits are clear prior to enabling                                           |

|       | an interrupt.                                                                             |

| REGISTER 3-5: | PIR1 REG | PIR1 REGISTER (ADDRESS: 0Ch) |     |     |  |  |  |  |

|---------------|----------|------------------------------|-----|-----|--|--|--|--|

|               | R/W-0    | R/W-0                        | R-0 | R-0 |  |  |  |  |

|       | R/W-0           | R/W-0                                                                                                      | R-0                          | R-0                        | U-0                                 | R/W-0       | R/W-0          | R/W-0  |  |  |  |  |  |

|-------|-----------------|------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------|-------------------------------------|-------------|----------------|--------|--|--|--|--|--|

|       | EEIF            | CMIF                                                                                                       | RCIF                         | TXIF                       |                                     | CCP1IF      | TMR2IF         | TMR1IF |  |  |  |  |  |

|       | bit 7           |                                                                                                            |                              |                            |                                     | I           |                | bit 0  |  |  |  |  |  |

| bit 7 | EEIF: EEP       | ROM Write                                                                                                  | Operation I                  | nterrupt Flag              | a bit                               |             |                |        |  |  |  |  |  |

|       | 1 = The wri     | ite operatior                                                                                              | n completed                  | l (must be c               | leared in softwa<br>has not been st |             |                |        |  |  |  |  |  |

| bit 6 | CMIF: Com       | parator Inte                                                                                               | errupt Flag b                | oit                        |                                     |             |                |        |  |  |  |  |  |

|       | •               | <ol> <li>Comparator output has changed</li> <li>Comparator output has not changed</li> </ol>               |                              |                            |                                     |             |                |        |  |  |  |  |  |

| bit 5 | RCIF: USA       | RT Receive                                                                                                 | Interrupt F                  | lag bit                    |                                     |             |                |        |  |  |  |  |  |

|       |                 | 1 = The USART receive buffer is full                                                                       |                              |                            |                                     |             |                |        |  |  |  |  |  |

| bit 4 |                 | <ul> <li>o = The USART receive buffer is empty</li> <li>TXIF: USART Transmit Interrupt Flag bit</li> </ul> |                              |                            |                                     |             |                |        |  |  |  |  |  |

| DIL 4 |                 |                                                                                                            | nit buffer is                | -                          |                                     |             |                |        |  |  |  |  |  |

|       |                 |                                                                                                            | nit buffer is                |                            |                                     |             |                |        |  |  |  |  |  |

| bit 3 | Unimplem        | ented: Rea                                                                                                 | d as '0'                     |                            |                                     |             |                |        |  |  |  |  |  |

| bit 2 | CCP1IF: C       | CP1 Interru                                                                                                | pt Flag bit                  |                            |                                     |             |                |        |  |  |  |  |  |

|       | 0 <b>= No T</b> | IR1 register<br>MR1 regist                                                                                 | r capture oc<br>er capture c |                            | at be cleared in                    | software)   |                |        |  |  |  |  |  |

|       |                 | IR1 register<br>MR1 registe                                                                                | •                            | natch occuri<br>match occu | red (must be cle<br>rred            | eared in so | ftware)        |        |  |  |  |  |  |

|       |                 | <u>-</u><br>in this mode                                                                                   | 9                            |                            |                                     |             |                |        |  |  |  |  |  |

| bit 1 | TMR2IF: T       | MR2 to PR2                                                                                                 | 2 Match Inte                 | errupt Flag b              | it                                  |             |                |        |  |  |  |  |  |

|       | 1 = TMR2 1      | o PR2 mate                                                                                                 |                              | (must be cl                | eared in softwa                     | re)         |                |        |  |  |  |  |  |

| bit 0 | TMR1IF: T       | MR1 Overf                                                                                                  | low Interrup                 | t Flag bit                 |                                     |             |                |        |  |  |  |  |  |

|       |                 |                                                                                                            | rflowed (mu<br>not overflov  |                            | ed in software)                     |             |                |        |  |  |  |  |  |

|       | Legend:         |                                                                                                            |                              |                            |                                     |             |                |        |  |  |  |  |  |

|       | R = Reada       | ble bit                                                                                                    | VV = V                       | Vritable bit               | U = Unimpl                          | emented b   | it, read as '( | )'     |  |  |  |  |  |

|       | -n = Value      | at POR                                                                                                     | '1' = E                      | Bit is set                 | '0' = Bit is c                      | leared      | x = Bit is ur  | nknown |  |  |  |  |  |

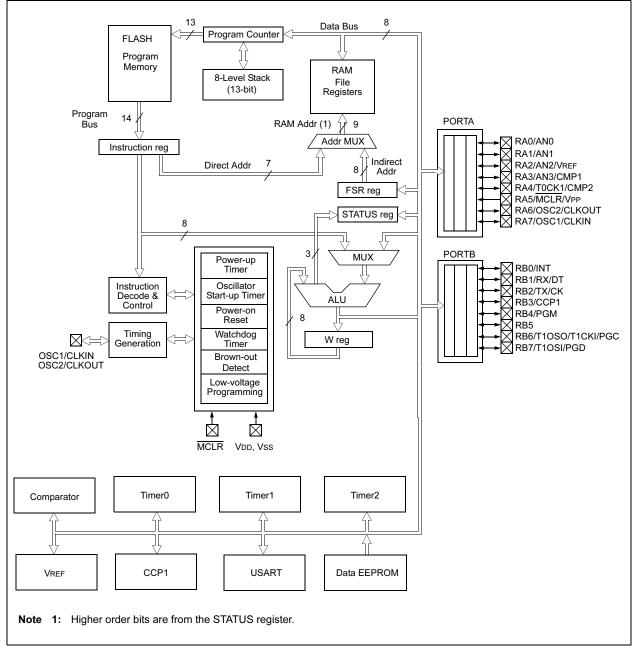

# 3.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 3-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

# 3.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 3.3.2 STACK

The PIC16F62X family has an 8-level deep x 13-bit wide hardware stack (Figure 3-1 and Figure 3-2). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 3.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a nooperation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 3-4.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 3-1.

#### EXAMPLE 3-1: Indirect Addressing

| NEXT | movlw<br>movwf<br>clrf<br>incf | 0x20<br>FSR<br>INDF<br>FSR<br>FSP 4 | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer .all done2</pre> |

|------|--------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|

|      | btfss                          | FSR,4                               | ;all done?                                                                          |

|      | goto                           | NEXT                                | ;no clear next                                                                      |

|      |                                |                                     | ;yes continue                                                                       |

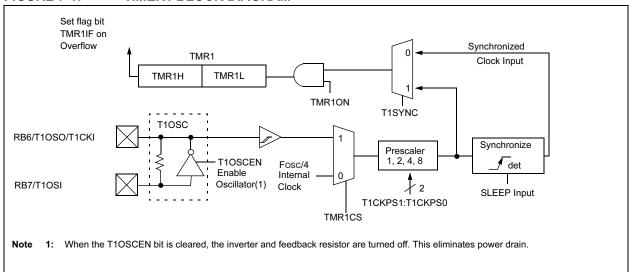

# 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

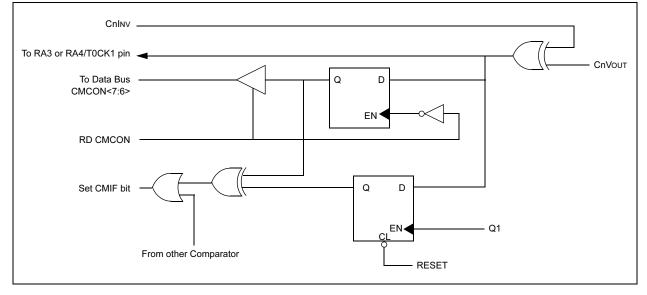

# 9.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4/T0CK1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4/T0CK1 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 9-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

# 10.2 Voltage Reference Accuracy/Error

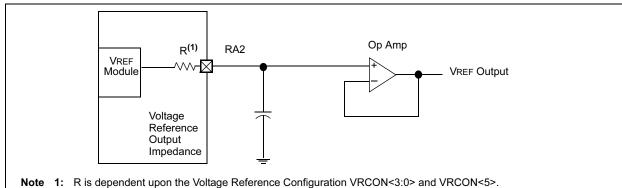

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

# 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

# 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

#### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

NOTES:

#### 12.2.2 ADEN USART ASYNCHRONOUS RECEIVER

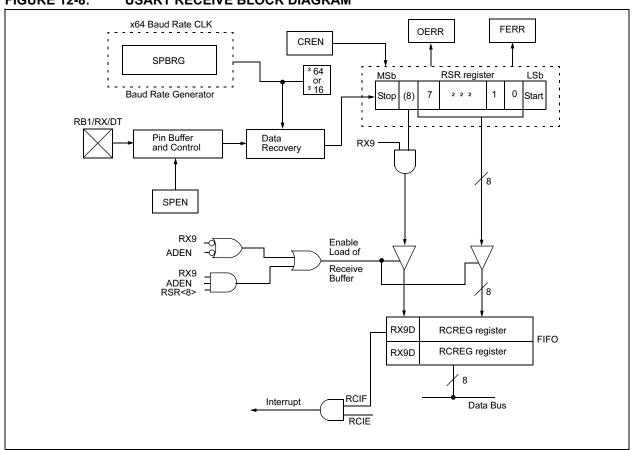

The receiver block diagram is shown in Figure 12-8. The data is received on the RB1/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register ( i.e., it is a two-deep FIFO).

It is possible for two bytes of data to be received and transferred to the RCREG FIFO, and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

FIGURE 12-8: USART RECEIVE BLOCK DIAGRAM

| Address | Name                               | Bit 7   | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|------------------------------------|---------|-----------|----------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF    | CMIF      | RCIF     | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN    | RX9       | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG                              | USART T | ransmit I | Register |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE    | CMIE      | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC    | TX9       | TXEN     | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |         |           |          |       |       |        |        |        | 0000 0000       | 0000 0000                       |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

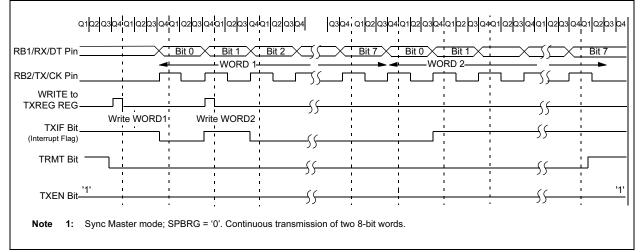

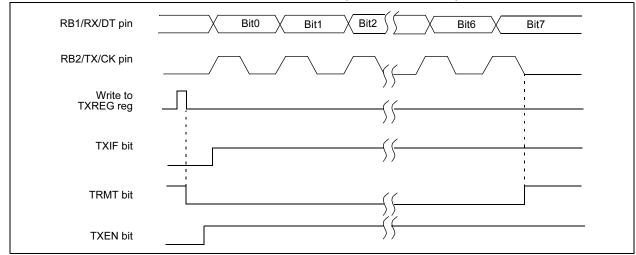

#### FIGURE 12-13: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

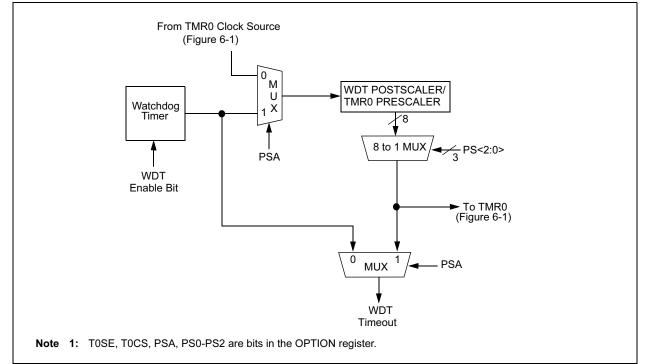

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-10: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name            | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|-----------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config.<br>bits | LVP   | BODEN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |

| 81h     | OPTION          | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: -= Unimplemented location, read as "0", + = Reserved for future use

**Note 1:** Shaded cells are not used by the Watchdog Timer.

#### 14.9 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | by a WDT timeout does not drive MCLR      |  |  |  |  |  |  |  |

|       | pin low.                                  |  |  |  |  |  |  |  |

# 16.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

### 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

# 16.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 16.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

# 16.18 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion. Note: The graphs and tables provided in this section are for design guidance and are not tested.

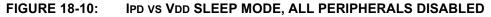

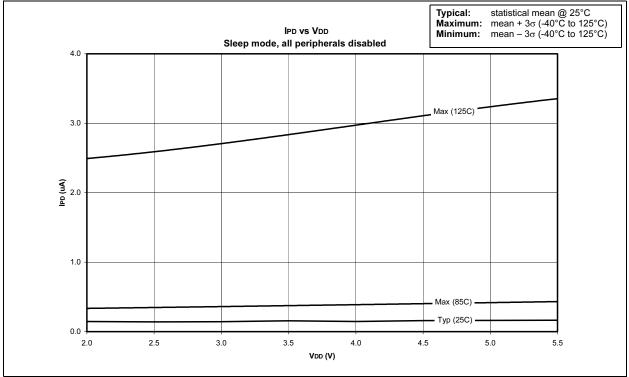

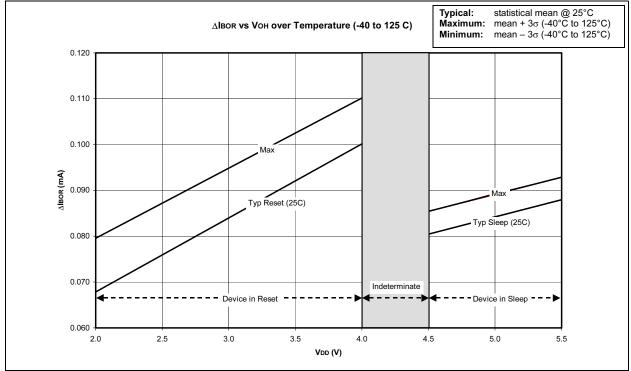

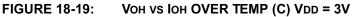

Note: The graphs and tables provided in this section are for design guidance and are not tested.

#### FIGURE 18-18: VOH VS IOH OVER TEMP (C) VDD = 5V

# PIC16F62X

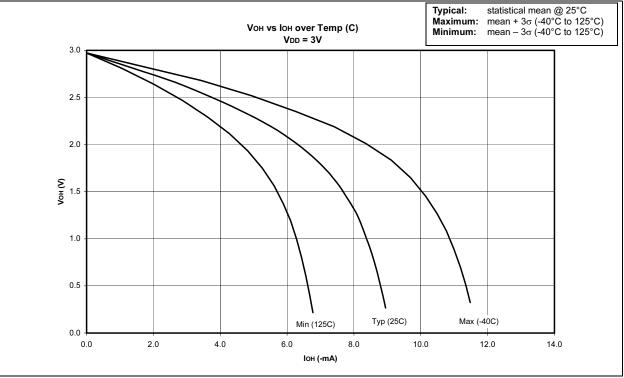

# K04-072 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm

|                          | Units  |      | INCHES* |      | MILLIMETERS |        |        |

|--------------------------|--------|------|---------|------|-------------|--------|--------|

| Dimension                | Limits | MIN  | NOM     | MAX  | MIN         | NOM    | MAX    |

| Number of Pins           | n      |      | 20      |      |             | 20     |        |

| Pitch                    | р      |      | .026    |      |             | 0.65   |        |

| Overall Height           | Α      | .068 | .073    | .078 | 1.73        | 1.85   | 1.98   |

| Molded Package Thickness | A2     | .064 | .068    | .072 | 1.63        | 1.73   | 1.83   |

| Standoff §               | A1     | .002 | .006    | .010 | 0.05        | 0.15   | 0.25   |

| Overall Width            | Е      | .299 | .309    | .322 | 7.59        | 7.85   | 8.18   |

| Molded Package Width     | E1     | .201 | .207    | .212 | 5.11        | 5.25   | 5.38   |

| Overall Length           | D      | .278 | .284    | .289 | 7.06        | 7.20   | 7.34   |

| Foot Length              | L      | .022 | .030    | .037 | 0.56        | 0.75   | 0.94   |

| Lead Thickness           | С      | .004 | .007    | .010 | 0.10        | 0.18   | 0.25   |

| Foot Angle               | ф      | 0    | 4       | 8    | 0.00        | 101.60 | 203.20 |

| Lead Width               | В      | .010 | .013    | .015 | 0.25        | 0.32   | 0.38   |

| Mold Draft Angle Top     | α      | 0    | 5       | 10   | 0           | 5      | 10     |

| Mold Draft Angle Bottom  | β      | 0    | 5       | 10   | 0           | 5      | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

NOTES: