Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 1.0 PIC16F62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F62X Product Identification System section (Page 167) at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 1.1 FLASH Devices

FLASH devices can be erased and reprogrammed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically-erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus, or PRO MATE<sup>®</sup> II programmers.

# 1.2 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 1.3 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

NOTES:

# 2.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16F62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F62X uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The Table below lists program memory (FLASH, Data and EEPROM).

TABLE 2-1: DEVICE DESCRIPTION

|            | Memory           |             |                |  |  |  |  |

|------------|------------------|-------------|----------------|--|--|--|--|

| Device     | FLASH<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |

| PIC16F627  | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16F628  | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF627 | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

| PIC16LF628 | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |  |  |

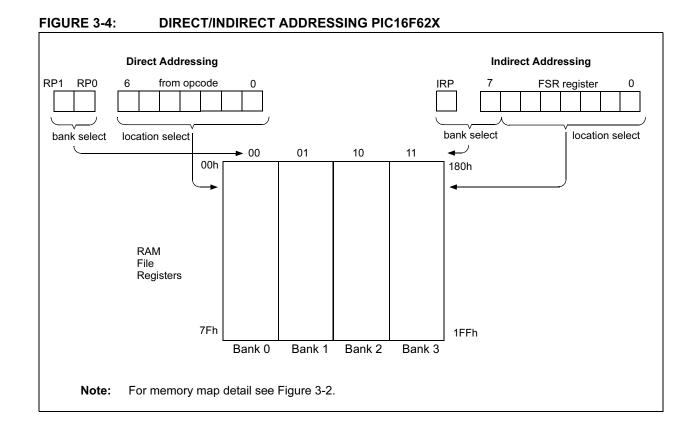

The PIC16F62X can directly or indirectly address its register files or data memory. All Special Function registers, including the program counter, are mapped in the data memory. The PIC16F62X have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any Addressing mode. This symmetrical nature, and lack of 'special optimal situations' make programming with the PIC16F62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bit wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 2-1, and a description of the device pins in Table 2-1.

Two types of data memory are provided on the PIC16F62X devices. Non-volatile EEPROM data memory is provided for long term storage of data such as calibration values, lookup table data, and any other data which may require periodic updating in the field. This data is not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. It is lost when power is removed.

#### 3.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1). See Section 6.3.1              |

#### **REGISTER 3-2:** OPTION REGISTER (ADDRESS: 81h, 181h)

101

110 111

Legend:

R = Readable bit

-n = Value at POR

1:64

1:128

1:256

|         |                  |                                                                                                                       | UBBILL                    | <i></i> ,,         | ,,                         |       |       |       |  |  |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|----------------------------|-------|-------|-------|--|--|

|         | R/W-1            | R/W-1                                                                                                                 | R/W-1                     | R/W-1              | R/W-1                      | R/W-1 | R/W-1 | R/W-1 |  |  |

|         | RBPU             | INTEDG                                                                                                                | TOCS                      | TOSE               | PSA                        | PS2   | PS1   | PS0   |  |  |

|         | bit 7            |                                                                                                                       |                           |                    |                            |       |       | bit 0 |  |  |

| bit 7   | <b>RBPU</b> : PO | RTB Pull-up                                                                                                           | o Enable bit              | :                  |                            |       |       |       |  |  |

|         | 1 = PORTE        | 3 pull-ups ai                                                                                                         | re disabled               |                    | port latch value           | es    |       |       |  |  |

| bit 6   | INTEDG: In       | nterrupt Edg                                                                                                          | je Select bi              | t                  |                            |       |       |       |  |  |

|         |                  | <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul> |                           |                    |                            |       |       |       |  |  |

| bit 5   | TOCS: TM         | R0 Clock Sc                                                                                                           | ource Selec               | t bit              |                            |       |       |       |  |  |

|         |                  | ion on RA4/<br>I instruction                                                                                          |                           | (CLKOUT)           |                            |       |       |       |  |  |

| bit 4   | TOSE: TMF        | R0 Source E                                                                                                           | Edge Select               | bit                |                            |       |       |       |  |  |

|         |                  | -                                                                                                                     |                           |                    | 4/T0CKI pin<br>4/T0CKI pin |       |       |       |  |  |

| bit 3   | PSA: Pres        | caler Assigr                                                                                                          | ment bit                  |                    |                            |       |       |       |  |  |

|         |                  | ller is assigr<br>ller is assigr                                                                                      |                           | /DT<br>imer0 modu  | le                         |       |       |       |  |  |

| bit 2-0 | PS2:PS0:         | Prescaler R                                                                                                           | ate Select k              | oits               |                            |       |       |       |  |  |

|         | E                | Bit Value T                                                                                                           | MR0 Rate                  | WDT Rate           |                            |       |       |       |  |  |

|         | -                | 000<br>001                                                                                                            | 1:2<br>1:4                | 1:1<br>1:2         |                            |       |       |       |  |  |

|         |                  | 010<br>011<br>100                                                                                                     | 1 : 8<br>1 : 16<br>1 : 32 | 1:4<br>1:8<br>1:16 |                            |       |       |       |  |  |

1:32 1:64

1:128

W = Writable bit

'1' = Bit is set

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### 3.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 3.2.2.4 and Section 3.2.2.5 for a description of the comparator enable and flag bits.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 3-3: |            | REGISTER                      | (ADDRES       | S: 0Bh, 8  | Bh, 10Bh, 18             | Bh)          |               |       |

|---------------|------------|-------------------------------|---------------|------------|--------------------------|--------------|---------------|-------|

|               | R/W-0      | R/W-0                         | R/W-0         | R/W-0      | R/W-0                    | R/W-0        | R/W-0         | R/W-x |

|               | GIE        | PEIE                          | T0IE          | INTE       | RBIE                     | T0IF         | INTF          | RBIF  |

|               | bit 7      |                               |               |            |                          |              |               | bit 0 |

| bit 7         | GIE: Globa | al Interrupt E                | nable bit     |            |                          |              |               |       |

|               |            | s all unmas<br>es all interru | •             | ots        |                          |              |               |       |

| bit 6         | PEIE: Peri | oheral Interr                 | upt Enable    | bit        |                          |              |               |       |

|               |            | s all unmas<br>es all periph  |               |            | S                        |              |               |       |

| bit 5         | TOIE: TMR  | 0 Overflow                    | Interrupt En  | able bit   |                          |              |               |       |

|               |            | s the TMR0<br>es the TMR0     |               |            |                          |              |               |       |

| bit 4         | INTE: RB0  | /INT Externa                  | al Interrupt  | Enable bit |                          |              |               |       |

|               |            | s the RB0/II<br>es the RB0/I  |               |            |                          |              |               |       |

| bit 3         | RBIE: RB I | Port Change                   | e Interrupt E | nable bit  |                          |              |               |       |

|               |            | s the RB po<br>es the RB po   |               |            |                          |              |               |       |

| bit 2         | TOIF: TMR  | 0 Overflow                    | nterrupt Fla  | ag bit     |                          |              |               |       |

|               |            | register has<br>register did  |               |            | eared in softwa          | are)         |               |       |

| bit 1         | INTF: RB0  | /INT Externa                  | al Interrupt  | Flag bit   |                          |              |               |       |

|               |            | 30/INT exter<br>30/INT exter  |               | •          | must be cleare           | d in softwaı | e)            |       |

| bit 0         | RBIF: RB I | Port Change                   | Interrupt F   | lag bit    |                          |              |               |       |

|               |            | at least one<br>of the RB7:R  |               |            | nanged state (n<br>state | nust be clea | ared in softw | vare) |

|               | Levendu    |                               |               |            |                          |              |               | 1     |

| Legend:           |                                                        |                      |                    |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |

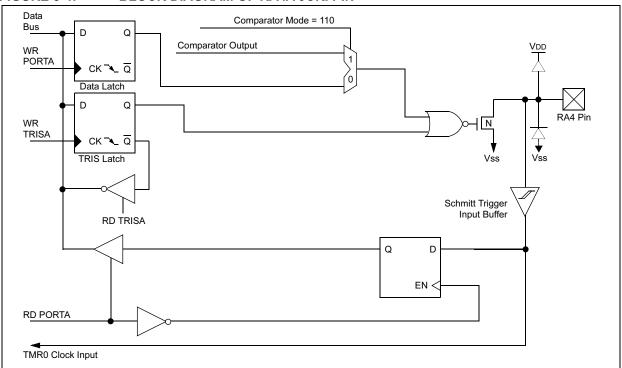

# PIC16F62X

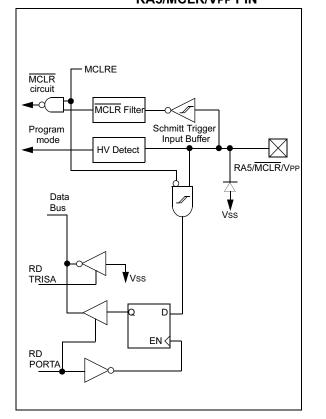

# BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

FIGURE 5-6:

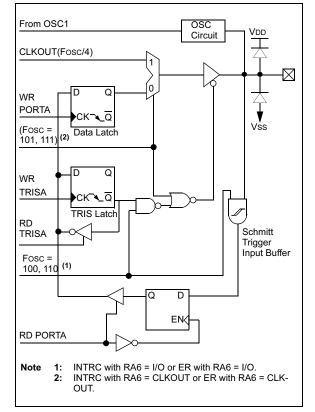

BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

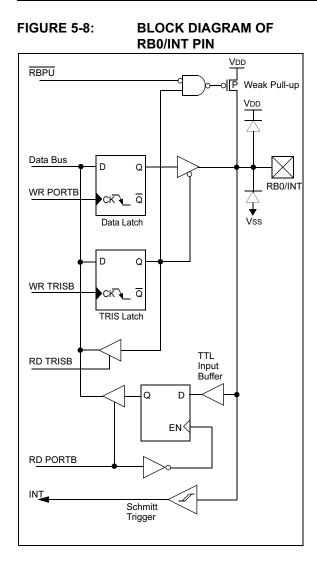

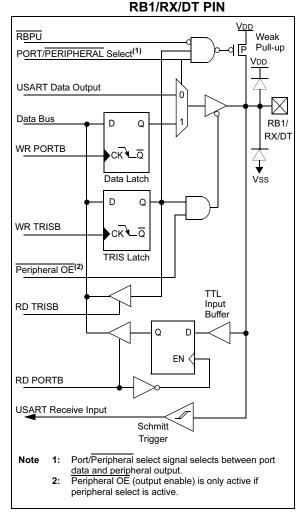

# FIGURE 5-9: BLOCK DIAGRAM OF

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information available in the PICmicro™ Mid Pange MCLL Eamily Reference

PICmicro™ Mid-Range MCU Family Reference Manual, DS31010A.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

# 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-7.

# 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2).

In Asynchronous Counter mode, Timer1 can not be used as a time-base for capture or compare operations.

#### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high-time and low-time requirements. Refer to the appropriate Electrical Specifications section, Timing Parameters 45, 46, and 47.

#### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVF TMR1H, W ;Read high byte

MOVWF TMPH

MOVF

TMR1L, W ;Read low byte

MOVWF TMPL

;

MOVF

TMR1H, W ;Read high byte

SUBWF

TMPH, W

;Sub 1st read

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

GOTO

CONTINUE ;Good 16-bit read

;

TMR1L may have rolled over between the read

;

; of the high and low bytes. Reading the high

; and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

MOVF

TMR1L, W

;Read low byte

MOVWF TMPL

;

; Re-enable the Interrupts (if required)

;Continue with your code

CONTINUE

```

| <b>REGISTER 8-1:</b> | T2CO       | N: TIMER C    |              | REGISTER     | (ADDRESS:   | 12h)   |         |         |

|----------------------|------------|---------------|--------------|--------------|-------------|--------|---------|---------|

|                      | U-0        | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |

|                      | _          | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |

|                      | bit 7      |               |              |              |             |        |         | bit 0   |

|                      |            |               |              |              |             |        |         |         |

| bit 7                | Unimplem   | ented: Read   | as '0'       |              |             |        |         |         |

| bit 6-3              | TOUTPS3:   | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |

|                      | 0000 = 1:1 | Postscale V   | alue         |              |             |        |         |         |

|                      | 0001 = 1:2 | Postscale V   | alue         |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | 1111 = 1:1 | 6 Postscale   |              |              |             |        |         |         |

|                      |            |               |              |              |             |        |         |         |

| bit 2                | TMR2ON:    | Timer2 On bi  | it           |              |             |        |         |         |

|                      | 1 = Timer2 | is on         |              |              |             |        |         |         |

|                      | 0 = Timer2 | is off        |              |              |             |        |         |         |

| bit 1-0              | T2CKPS1:   | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |

|                      | 00 = 1:1 P | rescaler Valu | е            |              |             |        |         |         |

|                      |            | rescaler Valu | -            |              |             |        |         |         |

|                      | 1x = 1:16  | Prescaler Val | ue           |              |             |        |         |         |

|                      | <b></b>    |               |              |              |             |        |         | 1       |

|                      | Legend:    |               |              |              |             |        |         |         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name                          | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|-------------------------------|-------|---------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                        | GIE   | PEIE    | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1                          | EEIF  | CMIF    | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1                          | EEIE  | CMIE    | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2 Timer2 module's register |       |         |         |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON                         | _     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2 Timer2 Period Register    |       |         |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

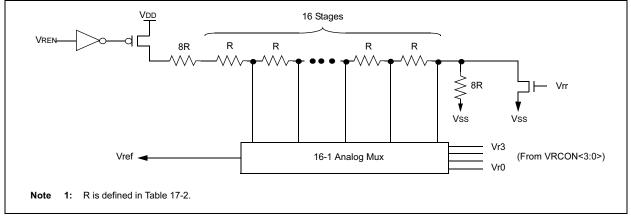

# 10.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 10-1. The block diagram is given in Figure 10-1.

REGISTER 10-1: VRCON REGISTER (ADDRESS: 9Fh)

# 10.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

voltage of 1.25V with VDD = 5.0V.

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 17-2). Example 10-1 shows an example of how to configure the Voltage Reference for an output

|         |                          | LOISTER                       |           | 5. 31 11)                                  |       |       |       |       |

|---------|--------------------------|-------------------------------|-----------|--------------------------------------------|-------|-------|-------|-------|

|         | R/W-0                    | R/W-0                         | R/W-0     | U-0                                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         | VREN                     | VROE                          | Vrr       | _                                          | VR3   | VR2   | VR1   | VR0   |

|         | bit 7                    |                               |           |                                            |       |       |       | bit   |

| bit 7   | Vren: Vrei               | F Enable                      |           |                                            |       |       |       |       |

|         |                          | ircuit power<br>ircuit power  |           | o IDD drain                                |       |       |       |       |

| bit 6   | VROE: VRE                | F Output En                   | able      |                                            |       |       |       |       |

|         |                          | s output on F<br>s disconnect | •         | 2 pin                                      |       |       |       |       |

| bit 5   | VRR: VREF                | Range sele                    | ction     |                                            |       |       |       |       |

|         | 1 = Low Ra<br>0 = High R | 0                             |           |                                            |       |       |       |       |

| bit 4   | Unimplem                 | ented: Rea                    | d as '0'  |                                            |       |       |       |       |

| bit 3-0 | When VRR                 | = 1: Vref =                   | (VR<3:0>/ | ≦ VR [3:0] ≤ 1<br>24) * VDD<br>⊦ (VR<3:0>/ |       |       |       |       |

|         |                          |                               |           |                                            |       |       |       |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | bit, read as '0'     |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### FIGURE 10-1: VOLTAGE REFERENCE BLOCK DIAGRAM

#### 12.4.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RB1/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is RESET by the hardware. In this case, it is RESET when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th

receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 12.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

| Address | Name  | Bit 7     | Bit 6                  | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR | Value on all<br>other<br>RESETS |

|---------|-------|-----------|------------------------|----------|-------|-------|--------|-----------|-----------|------------------|---------------------------------|

| 0Ch     | PIR1  | EEIF      | CMIF                   | RCIF     | TXIF  | _     | CCP1IF | TMR2IF    | TMR1IF    | 0000 -000        | 0000 -000                       |

| 18h     | RCSTA | SPEN      | RX9                    | SREN     | CREN  | ADEN  | FERR   | OERR      | RX9D      | 0000 -00x        | 0000 -00x                       |

| 1Ah     | RCREG | USART R   | USART Receive Register |          |       |       |        | 0000 0000 | 0000 0000 |                  |                                 |

| 8Ch     | PIE1  | EEPIE     | CMIE                   | RCIE     | TXIE  | _     | CCP1IE | TMR2IE    | TMR1IE    | -000 0000        | -000 -000                       |

| 98h     | TXSTA | CSRC      | TX9                    | TXEN     | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010        | 0000 -010                       |

| 99h     | SPBRG | Baud Rate | e Genera               | ator Reg | ister |       |        |           |           | 0000 0000        | 0000 0000                       |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

#### 13.3 READING THE EEPROM DATA MEMORY

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

# EXAMPLE 13-1: DATA EEPROM READ

| BSF   | STATUS, RPO | ; Bank 1          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | ;                 |

| MOVWF | EEADR       | ; Address to read |

| BSF   | EECON1, RD  | ; EE Read         |

| MOVF  | EEDATA, W   | ; W = EEDATA      |

| BCF   | STATUS, RPO | ; Bank 0          |

#### 13.4 WRITING TO THE EEPROM DATA MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

# EXAMPLE 13-2: DATA EEPROM WRITE

| WOVWW       SSN       ;         MOVWF       EECON2       ;         Write       SSN       ;         MOVWF       EECON2       ;         WOVWF       EECON2       ;         Write       AAh       ;         BSF       EECON1,WR       ;         BSF       EECON1,WR       ;         BSF       INTCON, GIE       ;         Enable       INTs. | Required<br>Sequence | MOVLW AAh<br>MOVWF EECON2<br>BSF EECON1,WR | ;<br>; Write AAh<br>; Set WR bit<br>; begin write |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will cause the data not to be written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit in the PIR1 registers must be cleared by software.

# 13.5 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 13-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

#### EXAMPLE 13-3: WRITE VERIFY

```

BSF

STATUS, RP0 ; Bank 1

MOVF

EEDATA, W

BSF

EECON1, RD

; Read the

; value written

; Is the value written (in W reg) and

; read (in EEDATA) the same?

SUBWF EEDATA, W

BCF STATUS, RPO ; Bank0

BTFSS STATUS, Z

; Is difference 0?

GOTO WRITE ERR

; NO, Write error

; YES, Good write

:

; Continue program

.

```

# 13.6 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence, and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

#### 13.7 DATA EEPROM OPERATION DURING CODE PROTECT

When the device is code protected, the CPU is able to read and write unscrambled data to the Data EEPROM.

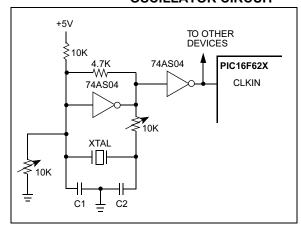

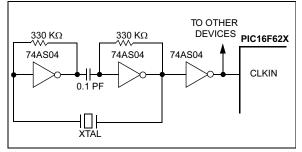

#### FIGURE 14-2: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 14-3 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-3: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

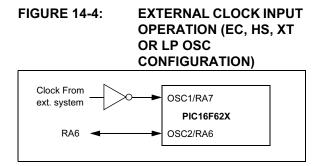

# 14.2.4 EXTERNAL CLOCK IN

For applications, where a clock is already available elsewhere, users may directly drive the PIC16F62X provided that this external clock source meets the AC/DC timing requirements listed in Section 17.4. Figure 14-4 shows how an external clock circuit should be configured.

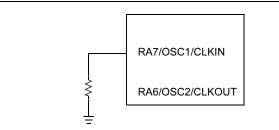

# 14.2.5 ER OSCILLATOR

For timing insensitive applications, the ER (External Resistor) Clock mode offers additional cost savings. Only one external component, a resistor to VSs, is needed to set the operating frequency of the internal oscillator. The resistor draws a DC bias current which controls the oscillation frequency. In addition to the resistance value, the oscillator frequency will vary from unit to unit, and as a function of supply voltage and temperature. Since the controlling parameter is a DC current and not a capacitance, the particular package type and lead frame will not have a significant effect on the resultant frequency.

Figure 14-5 shows how the controlling resistor is connected to the PIC16F62X. For REXT values below 10k, the oscillator operation becomes sensitive to temperature. For very high REXT values (e.g., 1M), the oscillator becomes sensitive to leakage and may stop completely. Thus, we recommend keeping REXT between 10k and 1M.

Table 14-3 shows the relationship between the resistance value and the operating frequency.

#### TABLE 14-3: RESISTANCE AND FREQUENCY RELATIONSHIP

| Resistance | Frequency |

|------------|-----------|

| 0          | 10.4 MHz  |

| 1K         | 10 MHz    |

| 10K        | 7.4 MHz   |

| 20K        | 5.3 MHz   |

| 47K        | 3 MHz     |

| 100K       | 1.6 MHz   |

| 220K       | 800 kHz   |

| 470K       | 300 kHz   |

| 1M         | 200 kHz   |

The ER Oscillator mode has two options that control the unused OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as an output providing the Fosc signal (internal clock divided by 4) for test or external synchronization purposes. Note: The graphs and tables provided in this section are for design guidance and are not tested.

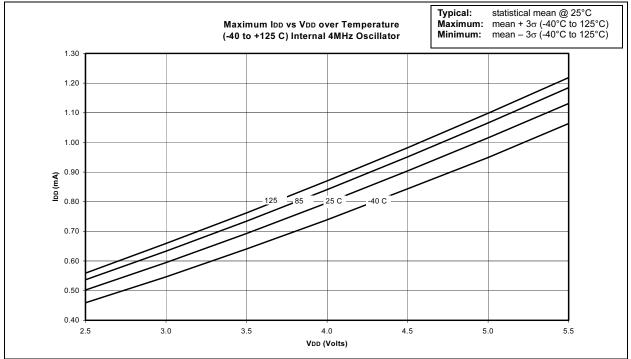

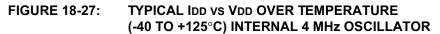

#### FIGURE 18-26: MAXIMUM IDD vs VDD OVER TEMPERATURE (-40 TO +125°C) INTERNAL 4 MHz OSCILLATOR

# PIC16F62X

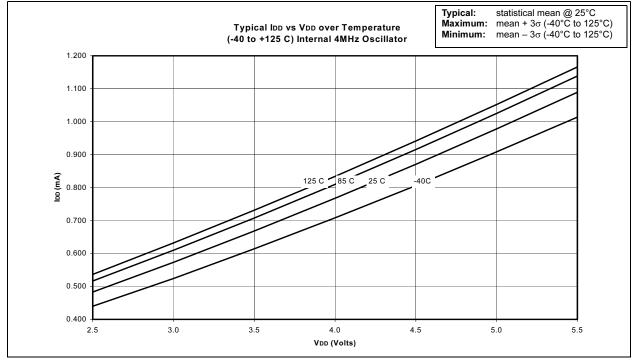

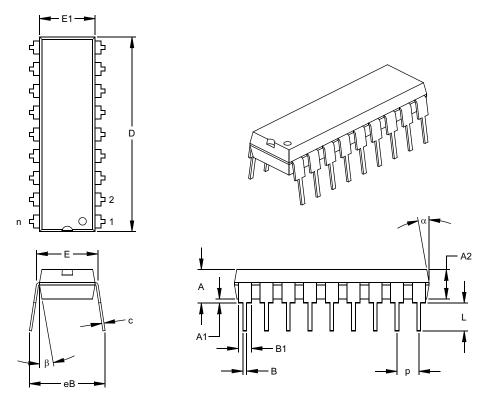

# K04-007 18-Lead Plastic Dual In-line (P) - 300 mil

| s MIN<br>.140 | NOM<br>18<br>.100                            | MAX                                                                                                                                                                                                               | MIN                                                                                                                                                                                                                                                                                                                    | NOM<br>18                                                                                                                                                                                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -             | .100                                         |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                        | 18                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -             |                                              |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -             |                                              |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                        | 2.54                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               | .155                                         | .170                                                                                                                                                                                                              | 3.56                                                                                                                                                                                                                                                                                                                   | 3.94                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .115          | .130                                         | .145                                                                                                                                                                                                              | 2.92                                                                                                                                                                                                                                                                                                                   | 3.30                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .015          |                                              |                                                                                                                                                                                                                   | 0.38                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| .300          | .313                                         | .325                                                                                                                                                                                                              | 7.62                                                                                                                                                                                                                                                                                                                   | 7.94                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .240          | .250                                         | .260                                                                                                                                                                                                              | 6.10                                                                                                                                                                                                                                                                                                                   | 6.35                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .890          | .898                                         | .905                                                                                                                                                                                                              | 22.61                                                                                                                                                                                                                                                                                                                  | 22.80                                                                                                                                                                                                                                                                                                                                                                                                                        | 22.99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| .125          | .130                                         | .135                                                                                                                                                                                                              | 3.18                                                                                                                                                                                                                                                                                                                   | 3.30                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .008          | .012                                         | .015                                                                                                                                                                                                              | 0.20                                                                                                                                                                                                                                                                                                                   | 0.29                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .045          | .058                                         | .070                                                                                                                                                                                                              | 1.14                                                                                                                                                                                                                                                                                                                   | 1.46                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .014          | .018                                         | .022                                                                                                                                                                                                              | 0.36                                                                                                                                                                                                                                                                                                                   | 0.46                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .310          | .370                                         | .430                                                                                                                                                                                                              | 7.87                                                                                                                                                                                                                                                                                                                   | 9.40                                                                                                                                                                                                                                                                                                                                                                                                                         | 10.92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5             | 10                                           | 15                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F             | 10                                           | 15                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               | .240<br>.890<br>.125<br>.008<br>.045<br>.014 | .240         .250           .890         .898           .125         .130           .008         .012           .045         .058           .014         .018           .310         .370           5         .10 | .240         .250         .260           .890         .898         .905           .125         .130         .135           .008         .012         .015           .045         .058         .070           .014         .018         .022           .310         .370         .430           5         10         15 | .240         .250         .260         6.10           .890         .898         .905         22.61           .125         .130         .135         3.18           .008         .012         .015         0.20           .045         .058         .070         1.14           .014         .018         .022         0.36           .310         .370         .430         7.87           5         10         15         5 | .240         .250         .260         6.10         6.35           .890         .898         .905         22.61         22.80           .125         .130         .135         3.18         3.30           .008         .012         .015         0.20         0.29           .045         .058         .070         1.14         1.46           .014         .018         .022         0.36         0.46           .310         .370         .430         7.87         9.40           5         10         15         5         10 |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

| MOVLW                    |     |

|--------------------------|-----|

| MOVWF                    | 116 |

| NOP                      |     |

| OPTION                   |     |

| RETFIE                   | 116 |

| RETLW                    |     |

| RETURN                   |     |

| RLF                      |     |

| RRF                      |     |

| SLEEP                    |     |

| SUBLW                    |     |

| SUBWF                    |     |

| SWAPF                    | 119 |

| TRIS                     | 119 |

| XORLW                    | 120 |

| XORWF                    | 120 |

| Instruction Set Summary  |     |

| INT Interrupt            | 102 |

| INTCON Register          | 21  |

| Interrupt Sources        |     |

| Capture Complete (CCP)   | 62  |

| Compare Complete (CCP)   | 63  |

| TMR2 to PR2 Match (PWM)  | 64  |

| Interrupts               | 101 |

| Interrupts, Enable Bits  |     |

| CCP1 Enable (CCP1IE Bit) | 62  |

| Interrupts, Flag Bits    |     |

| CCP1 Flag (CCP1IF Bit)   | 62  |

| IORLW Instruction        | 115 |

| IORWF Instruction        |     |

# Μ

| Memory Organization                             |          |

|-------------------------------------------------|----------|

| Data EEPROM Memory                              |          |

| MOVF Instruction                                |          |

| MOVLW Instruction                               | 115      |

| MOVWF Instruction                               | 116      |

| MPLAB C17 and MPLAB C18 C Compilers             | 122      |

| MPLAB ICD In-Circuit Debugger                   | 123      |

| MPLAB ICE High Performance Universal In-Circuit | Emulator |

| with MPLAB IDE                                  | 123      |

| MPLAB Integrated Development Environment Softw  | vare 121 |

| MPLINK Object Linker/MPLIB Object Librarian     | 122      |

|                                                 |          |

# Ν

# 0

| OPTION Instruction              |  |

|---------------------------------|--|

| OPTION Register                 |  |

| Oscillator Configurations       |  |

| Oscillator Start-up Timer (OST) |  |

| Output of TMR2.                 |  |

# Ρ

| 157   |

|-------|

| 157   |

| 25    |

| 24    |

| 24    |

| 124   |

| 124   |

| 124   |

| r 123 |

| 22    |

|       |

| Pin Functions                           |       |

|-----------------------------------------|-------|

| RC6/TX/CK                               | 67–84 |

| RC7/RX/DT                               | 67–84 |

| PIR1                                    | 23    |

| PIR1 Register                           | 23    |

| Port RB Interrupt                       |       |

| PORTA                                   | 29    |

| PORTB                                   | 34    |

| Power Control/Status Register (PCON)    |       |

| Power-Down Mode (SLEEP)                 |       |

| Power-On Reset (POR)                    |       |

| Power-up Timer (PWRT)                   |       |

| PR2 Register                            | 50    |

| Prescaler                               | 44    |

| Prescaler, Capture                      | 62    |

| Prescaler, Timer2                       | 65    |

| PRO MATE II Universal Device Programmer | 123   |

| Program Memory Organization             |       |