Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

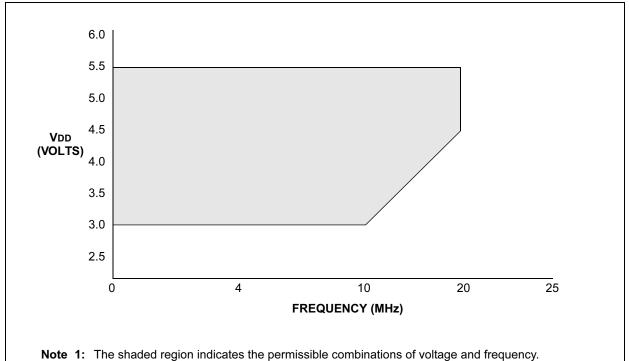

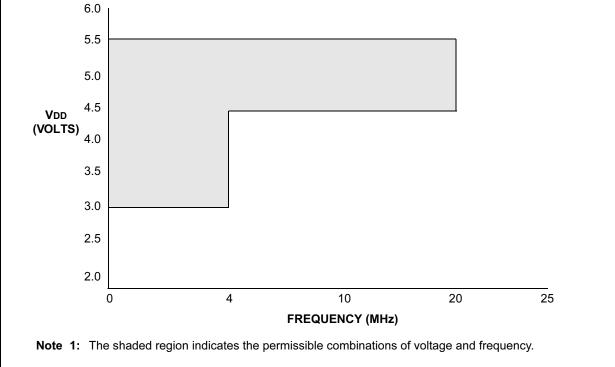

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-20e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 3.0 MEMORY ORGANIZATION

## 3.1 Program Memory Organization

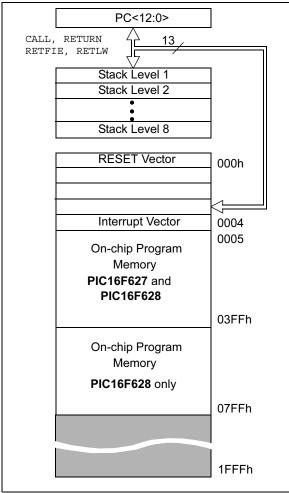

The PIC16F62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) for the PIC16F627 and 2K x 14 (0000h - 07FFh) for the PIC16F628 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space (PIC16F627) or 2K x 14 space (PIC16F628). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 3-1).

FIGURE 3-1: PROGRAM MEMORY MAP AND STACK

## 3.2 Data Memory Organization

The data memory (Figure 3-2) is partitioned into four banks, which contain the general purpose registers and the Special Function Registers (SFR). The SFR's are located in the first 32 locations of each Bank. Register locations 20-7Fh, A0h-FFh, 120h-14Fh, 170h-17Fh and 1F0h-1FFh are general purpose registers implemented as static RAM.

The Table below lists how to access the four banks of registers:

|       | RP1 | RP0 |

|-------|-----|-----|

| Bank0 | 0   | 0   |

| Bank1 | 0   | 1   |

| Bank2 | 1   | 0   |

| Bank3 | 1   | 1   |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

#### 3.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F62X. Each is accessed either directly or indirectly through the File Select Register FSR (See Section 3.4).

NOTES:

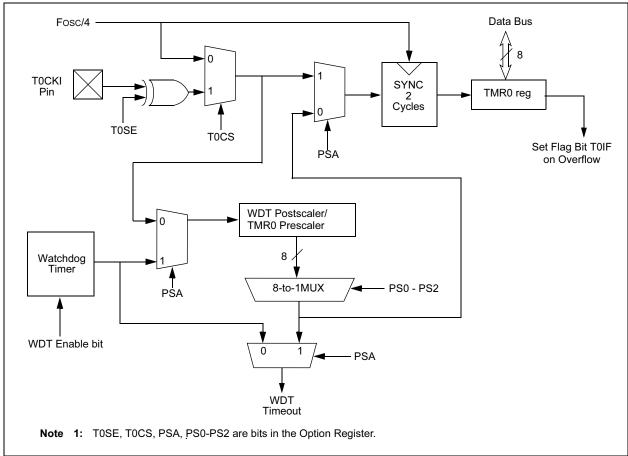

## 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

## 7.3 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 7.3.2).

In Asynchronous Counter mode, Timer1 can not be used as a time-base for capture or compare operations.

#### 7.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit  $\overline{T1SYNC}$  is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high-time and low-time requirements. Refer to the appropriate Electrical Specifications section, Timing Parameters 45, 46, and 47.

#### 7.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 7-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

### EXAMPLE 7-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVF TMR1H, W ;Read high byte

MOVWF TMPH

MOVF

TMR1L, W ;Read low byte

MOVWF TMPL

;

MOVF

TMR1H, W ;Read high byte

SUBWF

TMPH, W

;Sub 1st read

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

GOTO

CONTINUE ;Good 16-bit read

;

TMR1L may have rolled over between the read

;

; of the high and low bytes. Reading the high

; and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

MOVF

TMR1L, W

;Read low byte

MOVWF TMPL

;

; Re-enable the Interrupts (if required)

;Continue with your code

CONTINUE

```

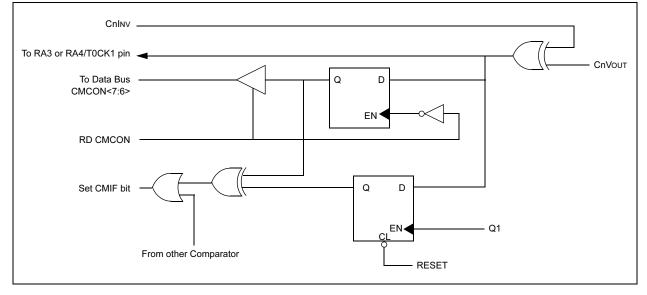

## 9.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4/T0CK1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4/T0CK1 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 9-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

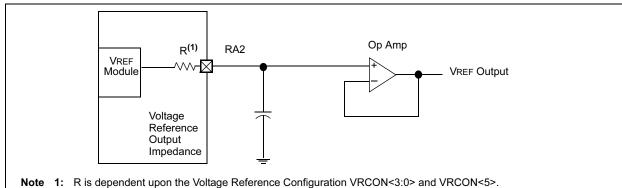

## 10.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

## 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

## 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

| BAUD     | Fosc = 20 M | Hz     | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615       | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230      | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878      | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818      | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636     | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250         | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625         | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250        | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 MHz |        | SPBRG              | 5.068 MHz |         | SPBRG              | 4 MHz    |         | SPBRG              |

|----------|-----------------|--------|--------------------|-----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) | KBAUD           | ERROR  | value<br>(decimal) | KBAUD     | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520           | -0.83% | 46                 | 9598.485  | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454          | +1.32% | 22                 | 18632.35  | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286          | -2.90% | 11                 | 39593.75  | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930          | -2.90% | 7                  | 52791.67  | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860         | -2.90% | 3                  | 105583.3  | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA              | _      | _                  | 316750    | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA              | _      | _                  | NA        | _       | _                  | NA       | _       | _                  |

| 1250000  | NA              |        | —                  | NA        | —       | _                  | NA       | —       |                    |

| BAUD        | Fosc = 3.579 MHz SPBRG |          | 1 MHz              |         | SPBRG    | 32.768 MHz         |       | SPBRG |                    |

|-------------|------------------------|----------|--------------------|---------|----------|--------------------|-------|-------|--------------------|

| RATE<br>(K) | KBAUD                  | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD | ERROR | value<br>(decimal) |

| 9600        | 9725.543               | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA    | NA    | NA                 |

| 19200       | 18640.63               | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA    | NA    | NA                 |

| 38400       | 37281.25               | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA    | NA    | NA                 |

| 57600       | 55921.88               | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA    | NA    | NA                 |

| 115200      | 111243.8               | -2.913%  | 1                  | NA      | _        | _                  | NA    | NA    | NA                 |

| 250000      | 223687.5               | -10.525% | 0                  | NA      | _        | _                  | NA    | NA    | NA                 |

| 625000      | NA                     | _        | _                  | NA      | _        | _                  | NA    | NA    | NA                 |

| 1250000     | NA                     | —        | —                  | NA      | —        | —                  | NA    | NA    | NA                 |

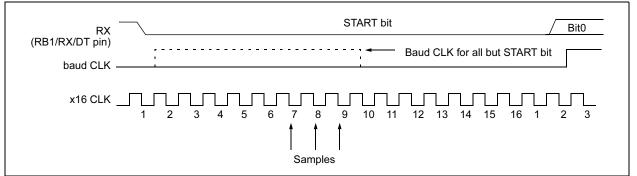

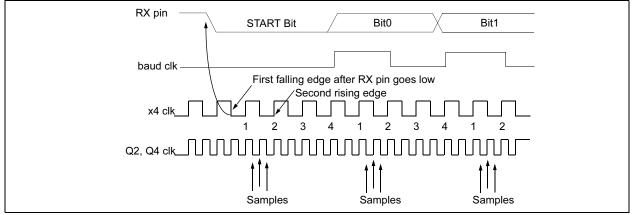

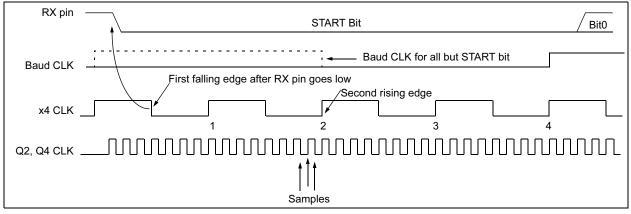

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

### FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

## FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

### FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

| Address | Name  | Bit 7                        | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|---------|-------|------------------------------|----------|---------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF     | RCIF    | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA | SPEN                         | RX9      | SREN    | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 -00x       | 0000 -00x                       |

| 1Ah     | RCREG | USART Re                     | ceive Re | egister |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1  | EEIE                         | CMIE     | RCIE    | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA | CSRC                         | TX9      | TXEN    | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |          |         |       |       |        |        |        | 0000 0000       | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

NOTES:

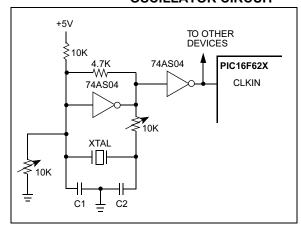

#### FIGURE 14-2: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

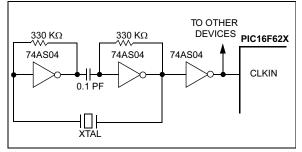

Figure 14-3 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-3: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

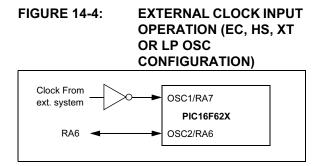

## 14.2.4 EXTERNAL CLOCK IN

For applications, where a clock is already available elsewhere, users may directly drive the PIC16F62X provided that this external clock source meets the AC/DC timing requirements listed in Section 17.4. Figure 14-4 shows how an external clock circuit should be configured.

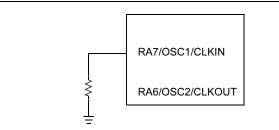

## 14.2.5 ER OSCILLATOR

For timing insensitive applications, the ER (External Resistor) Clock mode offers additional cost savings. Only one external component, a resistor to VSs, is needed to set the operating frequency of the internal oscillator. The resistor draws a DC bias current which controls the oscillation frequency. In addition to the resistance value, the oscillator frequency will vary from unit to unit, and as a function of supply voltage and temperature. Since the controlling parameter is a DC current and not a capacitance, the particular package type and lead frame will not have a significant effect on the resultant frequency.

Figure 14-5 shows how the controlling resistor is connected to the PIC16F62X. For REXT values below 10k, the oscillator operation becomes sensitive to temperature. For very high REXT values (e.g., 1M), the oscillator becomes sensitive to leakage and may stop completely. Thus, we recommend keeping REXT between 10k and 1M.

Table 14-3 shows the relationship between the resistance value and the operating frequency.

#### TABLE 14-3: RESISTANCE AND FREQUENCY RELATIONSHIP

| Resistance | Frequency |

|------------|-----------|

| 0          | 10.4 MHz  |

| 1K         | 10 MHz    |

| 10K        | 7.4 MHz   |

| 20K        | 5.3 MHz   |

| 47K        | 3 MHz     |

| 100K       | 1.6 MHz   |

| 220K       | 800 kHz   |

| 470K       | 300 kHz   |

| 1M         | 200 kHz   |

The ER Oscillator mode has two options that control the unused OSC2 pin. The first allows it to be used as a general purpose I/O port. The other configures the pin as an output providing the Fosc signal (internal clock divided by 4) for test or external synchronization purposes.

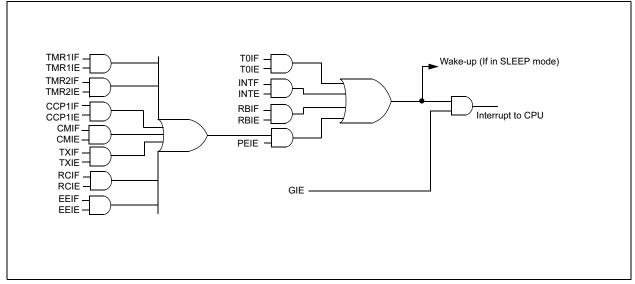

## 14.6 Interrupts

The PIC16F62X has 10 sources of interrupt:

- External Interrupt RB0/INT

- TMR0 Overflow Interrupt

- PORTB Change Interrupts (pins RB7:RB4)

- Comparator Interrupt

- USART Interrupt TX

- USART Interrupt RX

- CCP Interrupt

- TMR1 Overflow Interrupt

- TMR2 Match Interrupt

- EEPROM

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits interrupt routine as well as sets the GIE bit, which reenable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-15). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### FIGURE 14-14: INTERRUPT LOGIC

## TABLE 15-2: PIC16F62X INSTRUCTION SET

| Mnemonic,  |         | Description                  | Cycles           |     | 14-Bit | Opcode | •     | Status   | Notes |

|------------|---------|------------------------------|------------------|-----|--------|--------|-------|----------|-------|

| Operar     | nds     | Description                  | Cycles           | MSb |        |        | LSb   | Affected | Notes |

| BYTE-ORIE  | NTED F  | ILE REGISTER OPERATIONS      |                  |     |        |        |       |          |       |

| ADDWF      | f, d    | Add W and f                  | 1                | 00  | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF      | f, d    | AND W with f                 | 1                | 00  | 0101   | dfff   | ffff  | Z        | 1,2   |

| CLRF       | f       | Clear f                      | 1                | 00  | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW       | _       | Clear W                      | 1                | 00  | 0001   | 0000   | 0011  | Z        |       |

| COMF       | f, d    | Complement f                 | 1                | 00  | 1001   | dfff   | ffff  | Z        | 1,2   |

| DECF       | f, d    | Decrement f                  | 1                | 00  | 0011   | dfff   | ffff  | Z        | 1,2   |

| DECFSZ     | f, d    | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 00  | 1011   | dfff   | ffff  |          | 1,2,3 |

| INCF       | f, d    | Increment f                  | 1                | 00  | 1010   | dfff   | ffff  | Z        | 1,2   |

| INCFSZ     | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 00  | 1111   | dfff   | ffff  |          | 1,2,3 |

| IORWF      | f, d    | Inclusive OR W with f        | 1                | 00  | 0100   | dfff   | ffff  | Z        | 1,2   |

| MOVF       | f, d    | Move f                       | 1                | 00  | 1000   | dfff   | ffff  | Z        | 1,2   |

| MOVWF      | f       | Move W to f                  | 1                | 00  | 0000   | lfff   | ffff  |          |       |

| NOP        | _       | No Operation                 | 1                | 00  | 0000   | 0xx0   | 0000  |          |       |

| RLF        | f, d    | Rotate Left f through Carry  | 1                | 00  | 1101   | dfff   | ffff  | С        | 1,2   |

| RRF        | f, d    | Rotate Right f through Carry | 1                | 00  | 1100   | dfff   | ffff  | С        | 1,2   |

| SUBWF      | f, d    | Subtract W from f            | 1                | 0.0 | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |

| SWAPF      | f, d    | Swap nibbles in f            | 1                | 0.0 | 1110   | dfff   | ffff  | -, -,    | 1,2   |

| XORWF      | f, d    | Exclusive OR W with f        | 1                | 00  | 0110   | dfff   | ffff  | Z        | 1,2   |

| BIT-ORIENT | ED FILE | EREGISTER OPERATIONS         |                  |     |        |        |       |          |       |

| BCF        | f, b    | Bit Clear f                  | 1                | 01  | 00bb   | bfff   | ffff  |          | 1,2   |

| BSF        | f, b    | Bit Set f                    | 1                | 01  | 01bb   | bfff   | ffff  |          | 1,2   |

| BTFSC      | f, b    | Bit Test f, Skip if Clear    | 1 <sup>(2)</sup> | 01  | 10bb   | bfff   | ffff  |          | 3     |

| BTFSS      | f, b    | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 01  | 11bb   |        | ffff  |          | 3     |

| LITERAL AN | ND CON  | TROL OPERATIONS              |                  |     |        |        |       |          |       |

| ADDLW      | k       | Add literal and W            | 1                | 11  | 111x   | kkkk   | kkkk  | C,DC,Z   |       |

| ANDLW      | k       | AND literal with W           | 1                | 11  | 1001   | kkkk   | kkkk  | Z        |       |

| CALL       | k       | Call subroutine              | 2                | 10  | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT     | _       | Clear Watchdog Timer         | 1                | 00  | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO       | k       | Go to address                | 2                | 10  | 1kkk   | kkkk   | kkkk  | ,        |       |

| IORLW      | k       | Inclusive OR literal with W  | 1                | 11  | 1000   | kkkk   | kkkk  | Z        |       |

| MOVLW      | k       | Move literal to W            | 1                | 11  | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE     | _       | Return from interrupt        | 2                | 0.0 | 0000   | 0000   | 1001  |          |       |

| RETLW      | k       | Return with literal in W     | 2                | 11  | 01xx   | kkkk   | kkkk  |          |       |

| RETURN     | _       | Return from Subroutine       | 2                | 00  | 0000   | 0000   | 1000  |          |       |

| SLEEP      | _       | Go into Standby mode         | 1                | 00  | 0000   | 0110   | 0011  | TO, PD   |       |

| SUBLW      | k       | Subtract W from literal      | 1                | 11  | 110x   | kkkk   | kkkk  | C,DC,Z   |       |

| XORLW      | k       | Exclusive OR literal with W  | 1                | 11  | 1010   | kkkk   | kkkk  | Z        |       |

|            | IX.     |                              |                  | **  | T0T0   | VVVV   | VIVIV | -        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# PIC16F62X

| MOVWF            | Move W to f                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                              |

| Operands:        | $0 \leq f \leq 127$                                                                                   |

| Operation:       | $(W) \rightarrow (f)$                                                                                 |

| Status Affected: | None                                                                                                  |

| Encoding:        | 00 0000 1fff ffff                                                                                     |

| Description:     | Move data from W register to register 'f'.                                                            |

| Words:           | 1                                                                                                     |

| Cycles:          | 1                                                                                                     |

| Example          | MOVWF REG1                                                                                            |

|                  | Before Instruction<br>REG1 = $0xFF$<br>W = $0x4F$<br>After Instruction<br>REG1 = $0x4F$<br>W = $0x4F$ |

| OPTION           | Load Option Register                                                                                                                                                                                                                                                                                  |       |      |      |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                                                             | OPTIO | N    |      |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                                                  |       |      |      |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                                                              |       |      |      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |       |      |      |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                                                                    | 0000  | 0110 | 0010 |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a<br>readable/writable register, the<br>user can directly address it. Using<br>only register instruction such as<br>MOVWF. |       |      |      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                     |       |      |      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                     |       |      |      |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                                                                       |       |      |      |  |  |  |  |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                                                                                                                                                |       |      |      |  |  |  |  |  |

| NOP              | No Operation      |        |   |  |  |  |  |  |

|------------------|-------------------|--------|---|--|--|--|--|--|

| Syntax:          | [ label ]         | NOP    |   |  |  |  |  |  |

| Operands:        | None              |        |   |  |  |  |  |  |

| Operation:       | No oper           | ation  |   |  |  |  |  |  |

| Status Affected: | None              |        |   |  |  |  |  |  |

| Encoding:        | 00 0000 0xx0 0000 |        |   |  |  |  |  |  |

| Description:     | No oper           | ation. | • |  |  |  |  |  |

| Words:           | 1                 |        |   |  |  |  |  |  |

| Cycles:          | 1                 |        |   |  |  |  |  |  |

| Example          | NOP               |        |   |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                            |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS)<br>is loaded in the PC. Interrupts<br>are enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-<br>cycle instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                |  |  |  |  |  |  |  |

# PIC16F62X

## 17.3 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

2. TppS

| 2. TppS  |                                        |     |              |  |

|----------|----------------------------------------|-----|--------------|--|

| т        |                                        |     |              |  |

| F        | Frequency                              | Т   | Time         |  |

| Lowercas | se subscripts (pp) and their meanings: | _   |              |  |

| рр       |                                        |     |              |  |

| ck       | CLKOUT                                 | osc | OSC1         |  |

| io       | I/O port                               | tO  | TOCKI        |  |

| mc       | MCLR                                   |     |              |  |

| Uppercas | se letters and their meanings:         |     |              |  |

| S        |                                        |     |              |  |

| F        | Fall                                   | Р   | Period       |  |

| Н        | High                                   | R   | Rise         |  |

| I        | Invalid (Hi-impedance)                 | V   | Valid        |  |

| L        | Low                                    | Z   | Hi-Impedance |  |

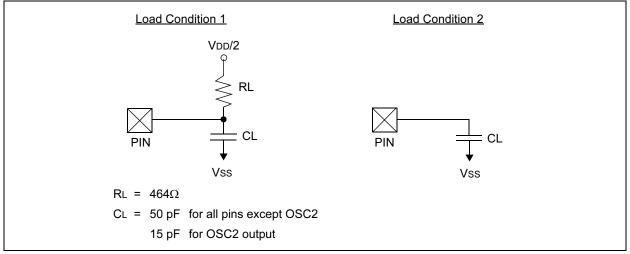

## FIGURE 17-5: LOAD CONDITIONS

| Param<br>No. | Sym        |                        | Min            | Тур†    | Max                   | Units | Conditions |    |                                   |

|--------------|------------|------------------------|----------------|---------|-----------------------|-------|------------|----|-----------------------------------|

| 50*          | TccL       | ССР                    | No Prescaler   |         | 0.5Tcy + 20           | —     | _          | ns |                                   |

|              |            | input low time         |                | 16F62X  | 10                    | —     | _          | ns |                                   |

|              |            | With Prescaler         | 16LF62X        | 20      | —                     | _     | ns         |    |                                   |

| 51*          |            |                        | No Prescaler   |         | 0.5Tcy + 20           | —     | _          | ns |                                   |

|              | input high | input high time        | e              | 16F62X  | 10                    |       |            | ns |                                   |

|              |            |                        | With Prescaler | 16LF62X | 20                    |       |            | ns |                                   |

| 52*          | TccP       | CCP input period       |                |         | <u>3Tcy + 40</u><br>N | _     |            | ns | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR       | CCP output rise time   |                | 16F62X  |                       | 10    | 25         | ns |                                   |

|              |            |                        |                | 16LF62X |                       | 25    | 45         | ns |                                   |

| 54*          | TccF       | F CCP output fall time |                | 16F62X  |                       | 10    | 25         | ns |                                   |

|              |            |                        |                | 16LF62X |                       | 25    | 45         | ns |                                   |

TABLE 17-8: CAPTURE/COMPARE/PWM REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

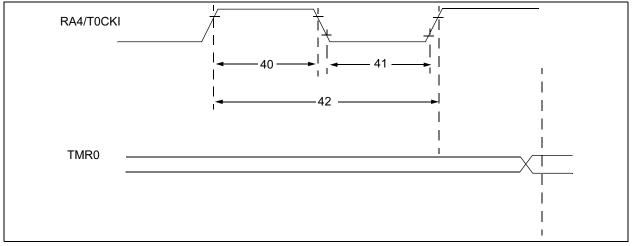

#### FIGURE 17-12: TIMER0 CLOCK TIMING

#### TABLE 17-9: TIMER0 CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Мах | Units | Conditions                            |

|--------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | —    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | _    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _    | _   | ns    | N = prescale value (1, 2,<br>4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

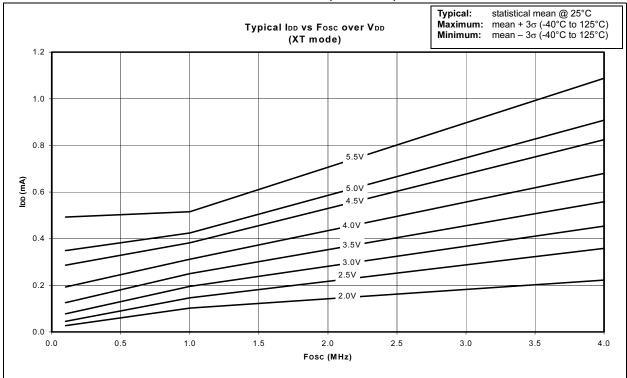

#### FIGURE 18-4: TYPICAL IDD vs Fosc OVER VDD (XT MODE)

# PIC16F62X

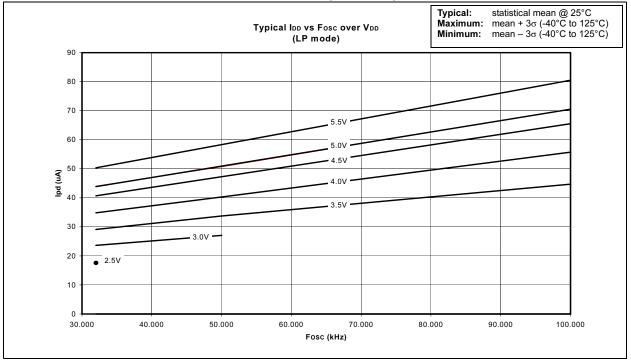

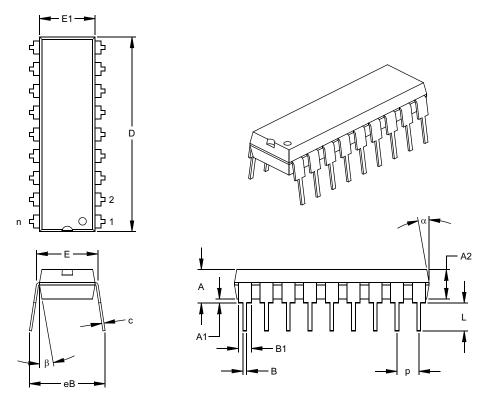

# K04-007 18-Lead Plastic Dual In-line (P) - 300 mil

| n Limits | MIN                                                                 | 11014                                                                                                                                                                                                                                                                                                           |                                                        |                                                        | MILLIMETERS                                            |                                                        |  |  |  |

|----------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|--|

|          |                                                                     | NOM                                                                                                                                                                                                                                                                                                             | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |  |  |  |

| n        |                                                                     | 18                                                                                                                                                                                                                                                                                                              |                                                        |                                                        | 18                                                     |                                                        |  |  |  |

| р        |                                                                     | .100                                                                                                                                                                                                                                                                                                            |                                                        |                                                        | 2.54                                                   |                                                        |  |  |  |

| А        | .140                                                                | .155                                                                                                                                                                                                                                                                                                            | .170                                                   | 3.56                                                   | 3.94                                                   | 4.32                                                   |  |  |  |

| A2       | .115                                                                | .130                                                                                                                                                                                                                                                                                                            | .145                                                   | 2.92                                                   | 3.30                                                   | 3.68                                                   |  |  |  |

| A1       | .015                                                                |                                                                                                                                                                                                                                                                                                                 |                                                        | 0.38                                                   |                                                        |                                                        |  |  |  |

| E        | .300                                                                | .313                                                                                                                                                                                                                                                                                                            | .325                                                   | 7.62                                                   | 7.94                                                   | 8.26                                                   |  |  |  |

| E1       | .240                                                                | .250                                                                                                                                                                                                                                                                                                            | .260                                                   | 6.10                                                   | 6.35                                                   | 6.60                                                   |  |  |  |

| D        | .890                                                                | .898                                                                                                                                                                                                                                                                                                            | .905                                                   | 22.61                                                  | 22.80                                                  | 22.99                                                  |  |  |  |

| L        | .125                                                                | .130                                                                                                                                                                                                                                                                                                            | .135                                                   | 3.18                                                   | 3.30                                                   | 3.43                                                   |  |  |  |

| С        | .008                                                                | .012                                                                                                                                                                                                                                                                                                            | .015                                                   | 0.20                                                   | 0.29                                                   | 0.38                                                   |  |  |  |

| B1       | .045                                                                | .058                                                                                                                                                                                                                                                                                                            | .070                                                   | 1.14                                                   | 1.46                                                   | 1.78                                                   |  |  |  |

| В        | .014                                                                | .018                                                                                                                                                                                                                                                                                                            | .022                                                   | 0.36                                                   | 0.46                                                   | 0.56                                                   |  |  |  |

| eB       | .310                                                                | .370                                                                                                                                                                                                                                                                                                            | .430                                                   | 7.87                                                   | 9.40                                                   | 10.92                                                  |  |  |  |

| α        | 5                                                                   | 10                                                                                                                                                                                                                                                                                                              | 15                                                     | 5                                                      | 10                                                     | 15                                                     |  |  |  |

| β        | 5                                                                   | 10                                                                                                                                                                                                                                                                                                              | 15                                                     | 5                                                      | 10                                                     | 15                                                     |  |  |  |

|          | A<br>A2<br>A1<br>E<br>E1<br>D<br>L<br>C<br>B1<br>B1<br>B<br>eB<br>α | p           A         .140           A2         .115           A1         .015           E         .300           E1         .240           D         .890           L         .125           C         .008           B1         .045           B         .014           eB         .310           α         5 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |  |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007