Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 224 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f628-20i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | General Description                                                    | 5     |

|------|------------------------------------------------------------------------|-------|

| 2.0  | General Description PIC16F62X Device Varieties                         | 7     |

| 3.0  | Architectural Overview                                                 | 9     |

| 4.0  | Memory Organization                                                    | 15    |

| 5.0  | I/O Ports                                                              | 29    |

| 6.0  | Timer0 Module                                                          | 43    |

| 7.0  | Timer1 Module                                                          | 46    |

| 8.0  | Timer2 Module                                                          | 50    |

| 9.0  | Comparator Module<br>Voltage Reference Module                          | 53    |

| 10.0 | Voltage Reference Module                                               | 59    |

| 11.0 | Capture/Compare/PWM (CCP) Module                                       | 61    |

| 12.0 | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) Module | 67    |

| 13.0 | Data EEPROM Memory                                                     | 87    |

| 14.0 | Special Features of the CPU                                            | 91    |

| 15.0 | Instruction Set Summary                                                | . 107 |

| 16.0 | Development Support                                                    | . 121 |

| 17.0 | Electrical Specifications                                              | . 127 |

| 18.0 | DC and AC Characteristics Graphs and Tables                            | . 143 |

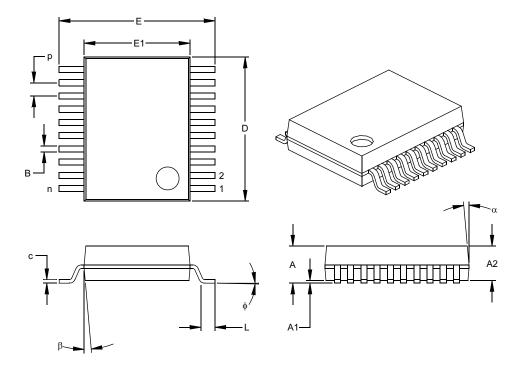

| 19.0 | Packaging Information                                                  | . 157 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

NOTES:

# 3.0 MEMORY ORGANIZATION

## 3.1 Program Memory Organization

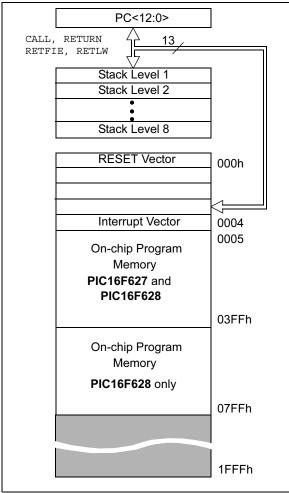

The PIC16F62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) for the PIC16F627 and 2K x 14 (0000h - 07FFh) for the PIC16F628 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space (PIC16F627) or 2K x 14 space (PIC16F628). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 3-1).

FIGURE 3-1: PROGRAM MEMORY MAP AND STACK

# 3.2 Data Memory Organization

The data memory (Figure 3-2) is partitioned into four banks, which contain the general purpose registers and the Special Function Registers (SFR). The SFR's are located in the first 32 locations of each Bank. Register locations 20-7Fh, A0h-FFh, 120h-14Fh, 170h-17Fh and 1F0h-1FFh are general purpose registers implemented as static RAM.

The Table below lists how to access the four banks of registers:

|       | RP1 | RP0 |

|-------|-----|-----|

| Bank0 | 0   | 0   |

| Bank1 | 0   | 1   |

| Bank2 | 1   | 0   |

| Bank3 | 1   | 1   |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

#### 3.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F62X. Each is accessed either directly or indirectly through the File Select Register FSR (See Section 3.4).

| Address | Name   | Bit 7               | Bit 6                                                                                        | Bit 5       | Bit 4         | Bit 3        | Bit 2         | Bit 1       | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|---------------------|----------------------------------------------------------------------------------------------|-------------|---------------|--------------|---------------|-------------|---------|-----------------------------------------|--------------------|

| Bank 1  |        |                     |                                                                                              |             |               |              |               |             |         |                                         |                    |

| 80h     | INDF   | Addressin register) | ddressing this location uses contents of FSR to address data memory (not a physical egister) |             |               |              |               |             | nysical | XXXX XXXX                               | 25                 |

| 81h     | OPTION | RBPU                | INTEDG                                                                                       | TOCS        | T0SE          | PSA          | PS2           | PS1         | PS0     | 1111 1111                               | 20                 |

| 82h     | PCL    | Program (           | Counter's (PC                                                                                | ) Least Sig | nificant Byte | e            |               |             |         | 0000 0000                               | 25                 |

| 83h     | STATUS | IRP                 | RP1                                                                                          | RP0         | TO            | PD           | Z             | DC          | С       | 0001 1xxx                               | 19                 |

| 84h     | FSR    | Indirect da         | ata memory a                                                                                 | ddress poir | nter          |              |               |             |         | xxxx xxxx                               | 25                 |

| 85h     | TRISA  | TRISA7              | TRISA6                                                                                       | TRISA5      | TRISA4        | TRISA3       | TRISA2        | TRISA1      | TRISA0  | 1111 1111                               | 29                 |

| 86h     | TRISB  | TRISB7              | TRISB6                                                                                       | TRISB5      | TRISB4        | TRISB3       | TRISB2        | TRISB1      | TRISB0  | 1111 1111                               | 34                 |

| 87h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 88h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       |                    |

| 89h     | _      | Unimplem            | Unimplemented                                                                                |             |               |              | _             | _           |         |                                         |                    |

| 8Ah     | PCLATH | _                   | _                                                                                            | _           | Write buffe   | er for upper | 5 bits of pro | ogram count | ter     | 0 0000                                  | 25                 |

| 8Bh     | INTCON | GIE                 | PEIE                                                                                         | T0IE        | INTE          | RBIE         | TOIF          | INTF        | RBIF    | 0000 000x                               | 21                 |

| 8Ch     | PIE1   | EEIE                | CMIE                                                                                         | RCIE        | TXIE          | _            | CCP1IE        | TMR2IE      | TMR1IE  | 0000 -000                               | 22                 |

| 8Dh     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 8Eh     | PCON   | _                   | _                                                                                            | _           | _             | OSCF         | _             | POR         | BOD     | 1-0x                                    | 24                 |

| 8Fh     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 90h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       |                    |

| 91h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 92h     | PR2    | Timer2 Pe           | eriod Register                                                                               |             |               |              |               |             |         | 1111 1111                               | 50                 |

| 93h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 94h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | _                                       | _                  |

| 95h     | _      | Unimplem            | ented                                                                                        |             |               |              |               |             |         | —                                       | _                  |

| 96h     |        | Unimplem            | ented                                                                                        |             |               |              |               |             |         | —                                       | —                  |

| 97h     |        | Unimplem            | ented                                                                                        |             |               |              |               |             |         | —                                       | —                  |

| 98h     | TXSTA  | CSRC                | TX9                                                                                          | TXEN        | SYNC          |              | BRGH          | TRMT        | TX9D    | 0000 -010                               | 69                 |

| 99h     | SPBRG  | Baud Rate           | e Generator F                                                                                | Register    |               |              |               |             |         | 0000 0000                               | 69                 |

| 9Ah     | EEDATA | EEPROM              | data register                                                                                |             |               |              |               |             |         | xxxx xxxx                               | 87                 |

| 9Bh     | EEADR  | _                   | EEPROM a                                                                                     | ddress regi | ster          |              |               | -           |         | xxxx xxxx                               | 87                 |

| 9Ch     | EECON1 | _                   | —                                                                                            | _           | _             | WRERR        | WREN          | WR          | RD      | x000                                    | 87                 |

| 9Dh     | EECON2 | EEPROM              | control regist                                                                               | er 2 (not a | physical reg  | gister)      |               |             |         |                                         | 87                 |

| 9Eh     | —      | Unimplem            | 1                                                                                            |             |               |              |               |             |         | _                                       | _                  |

| 9Fh     | VRCON  | VREN                | VROE                                                                                         | VRR         | —             | VR3          | VR2           | VR1         | VR0     | 000- 0000                               | 59                 |

| <b>TABLE 3-2:</b> | SPECIAL FUNCTION REGISTERS SUMMARY BANK 1 |

|-------------------|-------------------------------------------|

|                   |                                           |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

# 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The Operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 11.0). Register 7-1 shows the Timer1 Control register.

For the PIC16F627 and PIC16F628, when the Timer1 oscillator is enabled (T1OSCEN is set), the RB7/T1OSI and RB6/T1OSO/T1CKI pins become inputs. That is, the TRISB<7:6> value is ignored.

| U-0                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0               | R/W-0             | R/W-0        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0      |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| —                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T1CKPS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | T1CKPS0             | T1OSCEN           | T1SYNC       | TMR1CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TMR10N     |  |

| bit 7                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 0      |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

| Unimplem                                                 | ented: Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                 | id as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

| T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

| T1OSCEN                                                  | : Timer1 Os                                                                                                                                                                                                                                                                                                                                                                                                                                                | cillator Enat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ole Control b       | it                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rnal Clock Ir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nput Synchro        | nization Contro   | ol bit       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | a al ciana ut       |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

|                                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                   |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

| -                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | at                  |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

| This bit is i                                            | gnored. Tim                                                                                                                                                                                                                                                                                                                                                                                                                                                | ner1 uses the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e internal clo      | ck when TMR1      | CS = 0.      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |

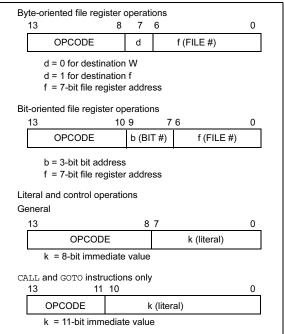

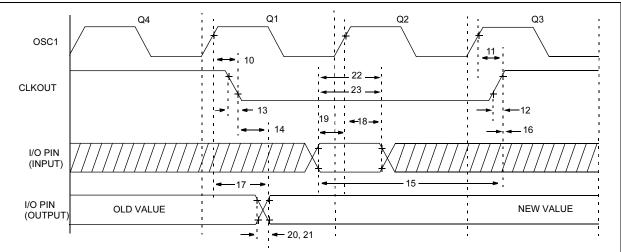

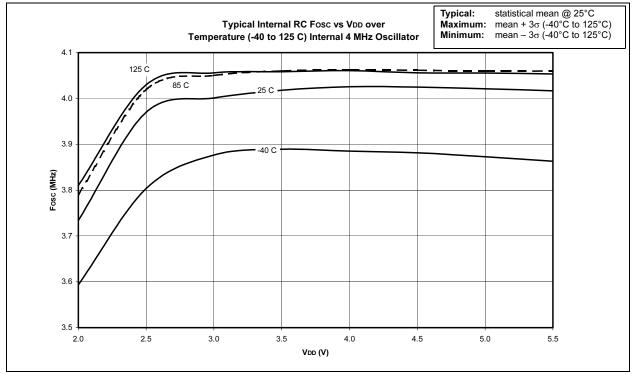

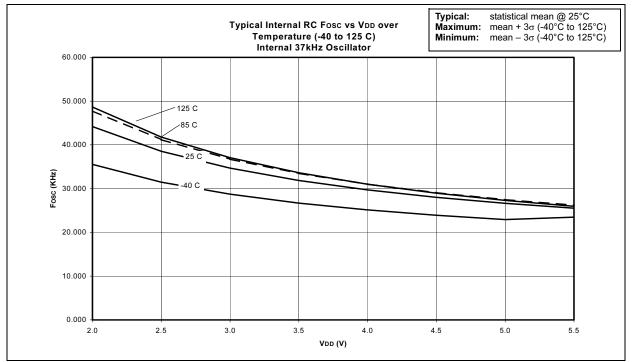

| TMR1CS:                                                  | Timer1 Cloo                                                                                                                                                                                                                                                                                                                                                                                                                                                | k Source Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | elect bit           |                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |