Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name   | Bit 7               | Bit 6           | Bit 5       | Bit 4         | Bit 3        | Bit 2         | Bit 1         | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|---------------------|-----------------|-------------|---------------|--------------|---------------|---------------|---------|-----------------------------------------|--------------------|

| Bank 1  |        |                     |                 |             |               |              |               |               |         |                                         |                    |

| 80h     | INDF   | Addressin register) | g this locatior | n uses cont | ents of FSF   | to address   | s data memo   | ory (not a ph | nysical | XXXX XXXX                               | 25                 |

| 81h     | OPTION | RBPU                | INTEDG          | TOCS        | T0SE          | PSA          | PS2           | PS1           | PS0     | 1111 1111                               | 20                 |

| 82h     | PCL    | Program (           | Counter's (PC   | ) Least Sig | nificant Byte | e            |               |               |         | 0000 0000                               | 25                 |

| 83h     | STATUS | IRP                 | RP1             | RP0         | TO            | PD           | Z             | DC            | С       | 0001 1xxx                               | 19                 |

| 84h     | FSR    | Indirect da         | ata memory a    | ddress poir | nter          |              |               |               |         | xxxx xxxx                               | 25                 |

| 85h     | TRISA  | TRISA7              | TRISA6          | TRISA5      | TRISA4        | TRISA3       | TRISA2        | TRISA1        | TRISA0  | 1111 1111                               | 29                 |

| 86h     | TRISB  | TRISB7              | TRISB6          | TRISB5      | TRISB4        | TRISB3       | TRISB2        | TRISB1        | TRISB0  | 1111 1111                               | 34                 |

| 87h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 88h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       |                    |

| 89h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 8Ah     | PCLATH | _                   | _               | _           | Write buffe   | er for upper | 5 bits of pro | ogram count   | ter     | 0 0000                                  | 25                 |

| 8Bh     | INTCON | GIE                 | PEIE            | T0IE        | INTE          | RBIE         | TOIF          | INTF          | RBIF    | 0000 000x                               | 21                 |

| 8Ch     | PIE1   | EEIE                | CMIE            | RCIE        | TXIE          | _            | CCP1IE        | TMR2IE        | TMR1IE  | 0000 -000                               | 22                 |

| 8Dh     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 8Eh     | PCON   | _                   | _               | _           | _             | OSCF         | _             | POR           | BOD     | 1-0x                                    | 24                 |

| 8Fh     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 90h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       |                    |

| 91h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 92h     | PR2    | Timer2 Pe           | eriod Register  |             |               |              |               |               |         | 1111 1111                               | 50                 |

| 93h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 94h     | _      | Unimplem            | ented           |             |               |              |               |               |         | _                                       | _                  |

| 95h     | _      | Unimplem            | ented           |             |               |              |               |               |         | —                                       | _                  |

| 96h     |        | Unimplem            | ented           |             |               |              |               |               |         | —                                       | —                  |

| 97h     |        | Unimplem            | ented           |             |               |              |               |               |         | —                                       | —                  |

| 98h     | TXSTA  | CSRC                | TX9             | TXEN        | SYNC          |              | BRGH          | TRMT          | TX9D    | 0000 -010                               | 69                 |

| 99h     | SPBRG  | Baud Rate           | e Generator F   | Register    |               |              |               |               |         | 0000 0000                               | 69                 |

| 9Ah     | EEDATA | EEPROM              | data register   |             |               |              |               |               |         | xxxx xxxx                               | 87                 |

| 9Bh     | EEADR  | _                   | EEPROM a        | ddress regi | ster          |              |               | -             |         | xxxx xxxx                               | 87                 |

| 9Ch     | EECON1 | _                   | —               | _           | _             | WRERR        | WREN          | WR            | RD      | x000                                    | 87                 |

| 9Dh     | EECON2 | EEPROM              | control regist  | er 2 (not a | physical reg  | gister)      |               |               |         |                                         | 87                 |

| 9Eh     | —      | Unimplem            | 1               |             |               |              |               |               |         | _                                       | _                  |

| 9Fh     | VRCON  | VREN                | VROE            | VRR         | —             | VR3          | VR2           | VR1           | VR0     | 000- 0000                               | 59                 |

| <b>TABLE 3-2:</b> | SPECIAL FUNCTION REGISTERS SUMMARY BANK 1 |

|-------------------|-------------------------------------------|

|                   |                                           |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### 3.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT     |  |  |  |  |  |  |  |

|       | (PSA = 1). See Section 6.3.1              |  |  |  |  |  |  |  |

#### **REGISTER 3-2:** OPTION REGISTER (ADDRESS: 81h, 181h)

101

110 111

Legend:

R = Readable bit

-n = Value at POR

1:64

1:128

1:256

|         |                                                                                                                             |                                  | UBBILL                    | <i></i> , , , ,    | ,,                         |       |       |       |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|--------------------|----------------------------|-------|-------|-------|--|--|--|

|         | R/W-1                                                                                                                       | R/W-1                            | R/W-1                     | R/W-1              | R/W-1                      | R/W-1 | R/W-1 | R/W-1 |  |  |  |

|         | RBPU                                                                                                                        | INTEDG                           | TOCS                      | TOSE               | PSA                        | PS2   | PS1   | PS0   |  |  |  |

|         | bit 7                                                                                                                       |                                  | •                         |                    |                            |       |       | bit 0 |  |  |  |

| bit 7   | <b>RBPU</b> : PO                                                                                                            | RTB Pull-up                      | o Enable bit              | :                  |                            |       |       |       |  |  |  |

|         | <ul> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |                                  |                           |                    |                            |       |       |       |  |  |  |

| bit 6   | INTEDG: In                                                                                                                  | nterrupt Edg                     | je Select bi              | t                  |                            |       |       |       |  |  |  |

|         |                                                                                                                             | pt on rising o<br>pt on falling  | 0                         |                    |                            |       |       |       |  |  |  |

| bit 5   | TOCS: TM                                                                                                                    | R0 Clock Sc                      | ource Selec               | t bit              |                            |       |       |       |  |  |  |

|         |                                                                                                                             | ion on RA4/<br>I instruction     |                           | (CLKOUT)           |                            |       |       |       |  |  |  |

| bit 4   | TOSE: TMF                                                                                                                   | R0 Source E                      | Edge Select               | bit                |                            |       |       |       |  |  |  |

|         |                                                                                                                             | -                                |                           |                    | 4/T0CKI pin<br>4/T0CKI pin |       |       |       |  |  |  |

| bit 3   | PSA: Pres                                                                                                                   | caler Assigr                     | ment bit                  |                    |                            |       |       |       |  |  |  |

|         |                                                                                                                             | ller is assigr<br>ller is assigr |                           | /DT<br>imer0 modu  | le                         |       |       |       |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                                    | Prescaler R                      | ate Select k              | oits               |                            |       |       |       |  |  |  |

|         | E                                                                                                                           | Bit Value T                      | MR0 Rate                  | WDT Rate           |                            |       |       |       |  |  |  |

|         | -                                                                                                                           | 000<br>001                       | 1:2<br>1:4                | 1:1<br>1:2         |                            |       |       |       |  |  |  |

|         |                                                                                                                             | 010<br>011<br>100                | 1 : 8<br>1 : 16<br>1 : 32 | 1:4<br>1:8<br>1:16 |                            |       |       |       |  |  |  |

1:32 1:64

1:128

W = Writable bit

'1' = Bit is set

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### PIR1 Register 3.2.2.5

This register contains interrupt flag bits.

| Note: | Interrupt flag bits get set when an interrupt<br>condition occurs regardless of the state of |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|       | 0                                                                                            |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the global                                                   |  |  |  |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User                                                            |  |  |  |  |  |  |  |  |

|       | software should ensure the appropriate                                                       |  |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling                                              |  |  |  |  |  |  |  |  |

|       | an interrupt.                                                                                |  |  |  |  |  |  |  |  |

| REGISTER 3-5: | PIR1 REG | ISTER (AD | DRESS: | 0Ch) |  |

|---------------|----------|-----------|--------|------|--|

|               | R/W-0    | R/W-0     | R-0    | R-0  |  |

|       | R/W-0                                                                                                                                                          | R/W-0                       | R-0                            | R-0                        | U-0                      | R/W-0       | R/W-0          | R/W-0  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------|----------------------------|--------------------------|-------------|----------------|--------|--|--|--|--|

|       | EEIF                                                                                                                                                           | CMIF                        | RCIF                           | TXIF                       |                          | CCP1IF      | TMR2IF         | TMR1IF |  |  |  |  |

|       | bit 7                                                                                                                                                          |                             |                                |                            |                          | I           |                | bit 0  |  |  |  |  |

| bit 7 | EEIF: EEP                                                                                                                                                      | ROM Write                   | Operation I                    | nterrupt Flag              | a bit                    |             |                |        |  |  |  |  |

|       | <ul> <li>1 = The write operation completed (must be cleared in software)</li> <li>0 = The write operation has not completed or has not been started</li> </ul> |                             |                                |                            |                          |             |                |        |  |  |  |  |

| bit 6 | CMIF: Com                                                                                                                                                      | parator Inte                | errupt Flag b                  | oit                        |                          |             |                |        |  |  |  |  |

|       | •                                                                                                                                                              | •                           | has chang<br>has not ch        |                            |                          |             |                |        |  |  |  |  |

| bit 5 | RCIF: USA                                                                                                                                                      | RT Receive                  | Interrupt F                    | lag bit                    |                          |             |                |        |  |  |  |  |

|       |                                                                                                                                                                |                             | e buffer is f<br>e buffer is e |                            |                          |             |                |        |  |  |  |  |

| bit 4 |                                                                                                                                                                |                             |                                |                            |                          |             |                |        |  |  |  |  |

| DIL 4 |                                                                                                                                                                |                             | t Interrupt F<br>nit buffer is | -                          |                          |             |                |        |  |  |  |  |

|       |                                                                                                                                                                |                             | nit buffer is                  |                            |                          |             |                |        |  |  |  |  |

| bit 3 | Unimplem                                                                                                                                                       | ented: Rea                  | d as '0'                       |                            |                          |             |                |        |  |  |  |  |

| bit 2 | CCP1IF: C                                                                                                                                                      | CP1 Interru                 | pt Flag bit                    |                            |                          |             |                |        |  |  |  |  |

|       | 0 <b>= No T</b>                                                                                                                                                | IR1 register<br>MR1 regist  | r capture oc<br>er capture c   |                            | at be cleared in         | software)   |                |        |  |  |  |  |

|       |                                                                                                                                                                | IR1 register<br>MR1 registe | •                              | natch occuri<br>match occu | red (must be cle<br>rred | eared in so | ftware)        |        |  |  |  |  |

|       |                                                                                                                                                                | <u>-</u><br>in this mode    | 9                              |                            |                          |             |                |        |  |  |  |  |

| bit 1 | TMR2IF: T                                                                                                                                                      | MR2 to PR2                  | 2 Match Inte                   | errupt Flag b              | it                       |             |                |        |  |  |  |  |

|       | 1 = TMR2 1                                                                                                                                                     | o PR2 mate                  |                                | (must be cl                | eared in softwa          | re)         |                |        |  |  |  |  |

| bit 0 | TMR1IF: T                                                                                                                                                      | MR1 Overf                   | low Interrup                   | t Flag bit                 |                          |             |                |        |  |  |  |  |

|       |                                                                                                                                                                |                             | rflowed (mu<br>not overflov    |                            | ed in software)          |             |                |        |  |  |  |  |

|       | Legend:                                                                                                                                                        |                             |                                |                            |                          |             |                |        |  |  |  |  |

|       | R = Reada                                                                                                                                                      | ble bit                     | VV = V                         | Vritable bit               | U = Unimpl               | emented b   | it, read as '( | )'     |  |  |  |  |

|       | -n = Value                                                                                                                                                     | at POR                      | '1' = E                        | Bit is set                 | '0' = Bit is c           | leared      | x = Bit is ur  | nknown |  |  |  |  |

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000       | xxxu 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

TABLE 5-2:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTA<sup>(1)</sup>

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTA.

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

PORTB is multiplexed with the external interrupt, USART, CCP module and the TMR1 clock input/output. The standard port functions and the alternate port functions are shown in Table 5-3. Alternate port functions override TRIS setting when enabled.

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-onchange comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       | when a read operation is being executed       |  |  |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

| <b>REGISTER 8-1:</b> | EGISTER 8-1: T2CON: TIMER CONTROL REGISTER (ADDRESS: 12h) |               |              |              |             |        |         |         |  |  |  |  |

|----------------------|-----------------------------------------------------------|---------------|--------------|--------------|-------------|--------|---------|---------|--|--|--|--|

|                      | U-0                                                       | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |  |  |  |  |

|                      | _                                                         | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |  |  |

|                      | bit 7                                                     |               |              |              |             |        |         | bit 0   |  |  |  |  |

|                      |                                                           |               |              |              |             |        |         |         |  |  |  |  |

| bit 7                | Unimplem                                                  | ented: Read   | as '0'       |              |             |        |         |         |  |  |  |  |

| bit 6-3              | TOUTPS3:                                                  | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |  |  |  |  |

|                      | 0000 = 1:1                                                | Postscale V   | alue         |              |             |        |         |         |  |  |  |  |

|                      | 0001 = 1:2                                                | Postscale V   | alue         |              |             |        |         |         |  |  |  |  |

|                      | •                                                         |               |              |              |             |        |         |         |  |  |  |  |

|                      | •                                                         |               |              |              |             |        |         |         |  |  |  |  |

|                      | 1111 = 1:1                                                | 6 Postscale   |              |              |             |        |         |         |  |  |  |  |

|                      |                                                           |               |              |              |             |        |         |         |  |  |  |  |

| bit 2                | TMR2ON:                                                   | Timer2 On bi  | it           |              |             |        |         |         |  |  |  |  |

|                      | 1 = Timer2                                                | is on         |              |              |             |        |         |         |  |  |  |  |

|                      | 0 = Timer2                                                | is off        |              |              |             |        |         |         |  |  |  |  |

| bit 1-0              | T2CKPS1:                                                  | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |  |  |  |  |

|                      | 00 = 1:1 P                                                | rescaler Valu | е            |              |             |        |         |         |  |  |  |  |

|                      |                                                           | rescaler Valu | -            |              |             |        |         |         |  |  |  |  |

|                      | 1x = 1:16                                                 | Prescaler Val | ue           |              |             |        |         |         |  |  |  |  |

|                      | <b></b>                                                   |               |              |              |             |        |         |         |  |  |  |  |

|                      | Legend:                                                   |               |              |              |             |        |         |         |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE         | PEIE           | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF        | CMIF           | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE        | CMIE           | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod  | lule's registe | r       |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

## 9.0 COMPARATOR MODULE

The Comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-chip Voltage Reference (Section 10.0) can also be an input to the comparators.

The CMCON register, shown in Register 9-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 9-1.

## REGISTER 9-1: CMCON REGISTER (ADDRESS: 01Fh)

| IER 9-1. |                                                                                                                                              | EGISTER                                                                              | (ADDRES    | 53. UTFII)    |                  |             |               |       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------|---------------|------------------|-------------|---------------|-------|

|          | R-0                                                                                                                                          | R-0                                                                                  | R/W-0      | R/W-0         | R/W-0            | R/W-0       | R/W-0         | R/W-0 |

|          | C2OUT                                                                                                                                        | C10UT                                                                                | C2INV      | C1INV         | CIS              | CM2         | CM1           | CM0   |

|          | bit 7                                                                                                                                        | 1                                                                                    | •          | •             |                  | -           | •             | bit 0 |

| bit 7    | <b>C2OUT</b> : Cor<br><u>When C2IN</u><br>1 = C2 VIN+<br>0 = C2 VIN+                                                                         | > C2 VIN-                                                                            | utput      |               |                  |             |               |       |

| bit 6    | When C2IN*           1 = C2 VIN+           0 = C2 VIN+           C1OUT: Cor           When C1IN*           1 = C1 VIN+           0 = C1 VIN+ | < C2 VIN-<br>> C2 VIN-<br>mparator 1 Or<br><u>V = 0:</u><br>> C1 VIN-                | utput      |               |                  |             |               |       |

|          | <u>When C1IN</u><br>1 = C1 Vin+<br>0 = C1 Vin+                                                                                               | < C1 VIN-                                                                            |            |               |                  |             |               |       |

| bit 5    | 1 = C2 Outp                                                                                                                                  | nparator 2 Ou<br>out inverted<br>out not inverte                                     |            | n             |                  |             |               |       |

| bit 4    | 1 = C1 Outp                                                                                                                                  | nparator 1 Ou<br>out inverted<br>out not inverte                                     |            | n             |                  |             |               |       |

| bit 3    | <u>When CM2:</u><br>Then:<br>1 = C1 VIN-                                                                                                     | rator Input Sv<br><u>CM0: = 001</u><br>connects to F<br>connects to F                | RA3        |               |                  |             |               |       |

|          | C2 VIN-<br>0 = C1 VIN-                                                                                                                       | <u>CM0 = 010</u><br>connects to F<br>connects to F<br>connects to F<br>connects to F | RA2<br>RA0 |               |                  |             |               |       |

| bit 2-0  |                                                                                                                                              | Comparator M<br>hows the Cor                                                         |            | des and CM2:0 | CM0 bit settings | 3           |               |       |

|          | Legend:                                                                                                                                      |                                                                                      |            |               |                  |             |               |       |

|          | R = Reada                                                                                                                                    | ble bit                                                                              | W = V      | Vritable bit  | U = Unimp        | plemented b | it, read as ' | 0'    |

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 11.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### EQUATION 11-1: PWM DUTY CYCLE

PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

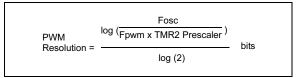

Maximum PWM resolution (bits) for a given PWM frequency:

## EQUATION 11-2: MAXIMUM PWM RESOLUTION

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

For an example on the PWM period and duty cycle calculation, see the PICmicro<sup>™</sup> Mid-Range Reference Manual (DS33023).

#### 11.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISB<3> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

#### TABLE 11-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 6.5       |

#### TABLE 11-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                               | Bit 6         | Bit 5      | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0              | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|---------|-------------------------------------|---------------|------------|---------|---------|--------|---------|--------------------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON  | GIE                                 | PEIE          | T0IE       | INTE    | RBIE    | T0IF   | INTF    | RBIF               | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1    | EEIF                                | CMIF          | RCIF       | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF             | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1    | EEIE                                | CMIE          | RCIE       | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE             | 0000 -000       | 0000 -000                       |

| 87h                   | TRISB   | PORTB D                             | ata Directior | Register   |         |         |        |         |                    | 1111 1111       | 1111 1111                       |

| 11h                   | TMR2    | Timer2 mo                           | dule's regis  | ter        |         |         |        |         |                    | 0000 0000       | 0000 0000                       |

| 92h                   | PR2     | Timer2 mo                           | dule's perio  | d register |         |         |        |         |                    | 1111 1111       | 1111 1111                       |

| 12h                   | T2CON   | —                                   | TOUTPS3       | TOUTPS2    | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0            | -000 0000       | uuuu                            |

| 15h                   | CCPR1L  | Capture/Compare/PWM register1 (LSB) |               |            |         |         |        |         | xxxx xxxx uuuu uuu |                 |                                 |

| 16h                   | CCPR1H  | Capture/Compare/PWM register1 (MSB) |               |            |         |         |        |         | xxxx xxxx          | uuuu uuuu       |                                 |

| 17h                   | CCP1CON | —                                   | _             | CCP1X      | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0             | 00 0000         | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

## 12.3 USART Function

The USART function is similar to that on the PIC16C74B, which includes the BRGH = 1 fix.

#### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed so when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer. The ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if, and only, if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (='1'), all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = '1'). When ADEN is disabled (='0'), all data bytes are received and the 9th bit can be used as the PARITY bit.

The USART Receive Block Diagram is shown in Figure 12-8.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Steps to follow when setting up an Asynchronous or Synchronous Reception with Address Detect Enabled:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable asynchronous or synchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. Set bit RX9 to enable 9-bit reception.

- 5. Set ADEN to enable address detect.

- 6. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 9. If any error occurred, clear the error by clearing enable bit CREN if it was already set.

- If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name  | Bit 7     | Bit 6    | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR |      |      | e on<br>other<br>ETS |

|---------|-------|-----------|----------|-------------|-------|-------|--------|--------|--------|-----------------|------|------|----------------------|

| 0Ch     | PIR1  | EEIF      | CMIF     | RCIF        | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF | 0000            | -000 | 0000 | -000                 |

| 18h     | RCSTA | SPEN      | RX9      | SREN        | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000            | -00x | 0000 | -00x                 |

| 1Ah     | RCREG | RX7       | RX6      | RX5         | RX4   | RX3   | RX2    | RX1    | RX0    | 0000            | 0000 | 0000 | 0000                 |

| 8Ch     | PIE1  | EEIE      | CMIE     | RCIE        | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000            | -000 | 0000 | -000                 |

| 98h     | TXSTA | CSRC      | TX9      | TXEN        | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000            | -010 | 0000 | -010                 |

| 99h     | SPBRG | Baud Rate | e Genera | ator Regist | er    |       |        |        |        | 0000            | 0000 | 0000 | 0000                 |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

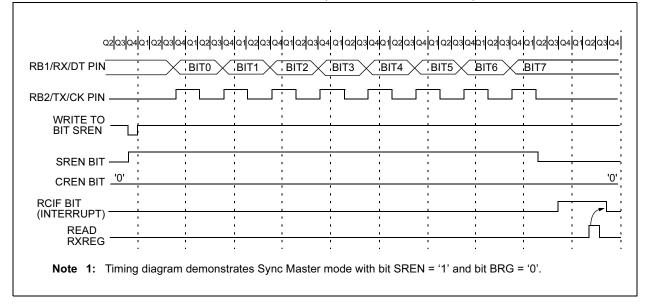

### 12.4 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RB2/TX/CK and RB1/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART Transmitter Block Diagram is shown in Figure 12-5. The heart of the transmitter is the Transmit (serial) Shift register (TSR). The Shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will RESET only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will RESET the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set, during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however is not RESET although it is disconnected from the pins. In order to RESET the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from Hi-impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

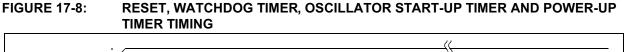

## 14.5 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Detect (BOD)

#### 14.5.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

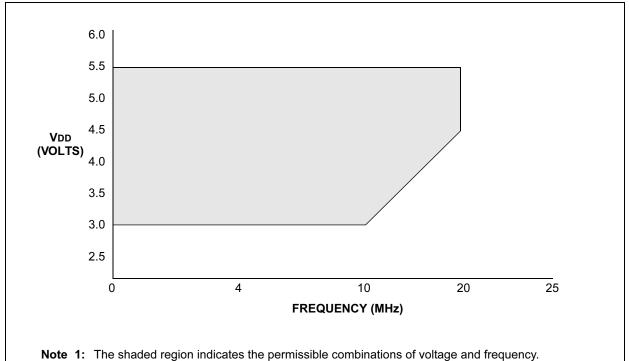

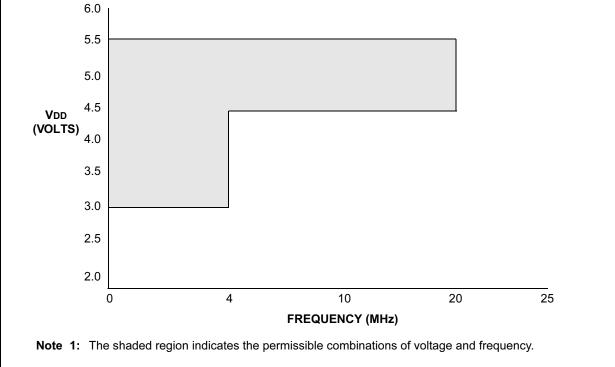

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 14.5.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) timeout on power-up only, from POR or Brown-out Detect Reset. The PWRT operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. The PWRT should always be enabled when Brown-out Detect Reset is enabled. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 14.5.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

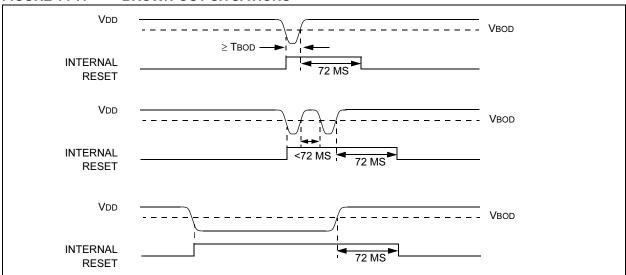

#### 14.5.4 BROWN-OUT DETECT (BOD) RESET

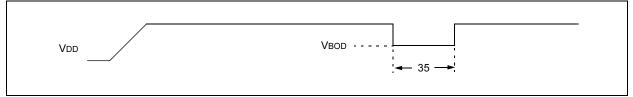

The PIC16F62X members have on-chip BOD circuitry. A configuration bit, BODEN, can disable (if clear/ programmed) or enable (if set) the BOD Reset circuitry. If VDD falls below VBOD for longer than TBOD, the brown-out situation will RESET the chip. A RESET is not guaranteed to occur if VDD falls below VBOD for shorter than TBOD. VBOD and TBOD are defined in Table 17-1 and Table 17-6, respectively.

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above VBOD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below VBOD while the Power-up Timer is running, the chip will go back into a Brown-out Detect Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Detect is enabled. Figure 14-7 shows typical Brown-out situations.

FIGURE 14-7: BROWN-OUT SITUATIONS

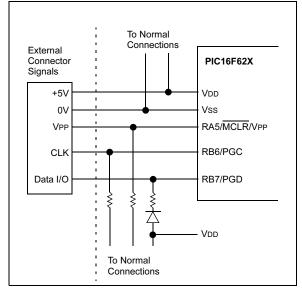

## 14.12 In-Circuit Serial Programming

The PIC16F62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 14-18.

#### FIGURE 14-18: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 14.13 Low Voltage Programming

The LVP bit of the configuration word, enables the low voltage programming. This mode allows the microcontroller to be programmed via ICSP using only a 5V source. This mode removes the requirement of VIHH to be placed on the MCLR pin. The LVP bit is normally erased to '1', which enables the low voltage programming. In this mode, the RB4/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. The device will enter Programming mode when a '1' is placed on the RB4/PGM pin. The HV Programming mode is still available by placing VIHH on the MCLR pin.

- Note 1: While in this mode, the RB4 pin can no longer be used as a general purpose I/O pin.

- 2: VDD must be 5.0V <u>+</u>10% during erase/ program operations while in low voltage Programming mode.

If Low voltage Programming mode is not used, the LVP bit can be programmed to a '0', and RB4/PGM becomes a digital I/O pin. To program the device, VIHH must be placed onto MCLR during programming. The LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit cannot be programmed when programming is entered with RB4/PGM.

It should be noted, that once the LVP bit is programmed to 0, High voltage Programming mode can be used to program the device.

|          | MPLAB Integrated<br>Development Environment | MPLAB C17 C Compiler | MPLAB C18 C Compiler | MPASM Assembler/<br>MPLINK Object Linker | MPLAB C30 C Compiler | MPLAB ASM30<br>Assembler/Linker/Librarian | MPLAB ICE 2000<br>In-Circuit Emulator | MPLAB ICE 4000<br>In-Circuit Emulator | MPLAB ICD 2 In-Circuit<br>Debugger | PICSTART Plus Entry Level<br>Development Programmer | PRO MATE II<br>Universal Device Programmer | <b>PICDEM 1</b> Demonstration Board | PICDEM.net Demonstration<br>Board | PICDEM 2 Plus Demonstration<br>Board | <b>PICDEM 3 Demonstration Board</b> | PICDEM 14A Demonstration<br>Board | PICDEM 17 Demonstration<br>Board | PICDEM 18R Demonstration<br>Board | PICDEM LIN Demonstration<br>Board | PICDEM USB Demonstration<br>Board     |

|----------|---------------------------------------------|----------------------|----------------------|------------------------------------------|----------------------|-------------------------------------------|---------------------------------------|---------------------------------------|------------------------------------|-----------------------------------------------------|--------------------------------------------|-------------------------------------|-----------------------------------|--------------------------------------|-------------------------------------|-----------------------------------|----------------------------------|-----------------------------------|-----------------------------------|---------------------------------------|

| PIC12CXX | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC12FXX | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       | >                                  | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC14000 | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     | >                                 |                                  |                                   |                                   |                                       |

| PIC16C5  | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          | >                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C6  | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     | * ^                                | >                                                   | >                                          |                                     |                                   | 7                                    |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16CX) | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          | >                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C4: | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   | >                                 |                                       |

| PIC16F6  | >                                           |                      |                      | >                                        |                      |                                           | **`^                                  |                                       |                                    | **^                                                 | **/                                        |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16C   | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     | *^                                 | >                                                   | >                                          | ⁺,                                  |                                   | ,                                    |                                     |                                   |                                  |                                   |                                   |                                       |

| (2091019 | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| (7081019 | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   |                                   | >                                     |

| PIC16C8  | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          | ~                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |

| PIC16F8X | >                                           |                      |                      | >                                        |                      |                                           | >                                     |                                       | ^                                  | ~                                                   | >                                          |                                     |                                   |                                      |                                     |                                   |                                  |                                   | ~                                 | ^                                     |

| Kecalouq | >                                           |                      |                      | >                                        |                      |                                           | >                                     | >                                     |                                    | >                                                   | >                                          |                                     |                                   |                                      | >                                   |                                   |                                  |                                   |                                   | >           -           -           - |

| PIC17C4  | >                                           | ~                    |                      | >                                        |                      |                                           | >                                     |                                       |                                    | >                                                   | >                                          | >                                   |                                   |                                      |                                     |                                   |                                  |                                   |                                   |                                       |