Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627a-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | General Description                                                    | 5     |

|------|------------------------------------------------------------------------|-------|

| 2.0  | General Description PIC16F62X Device Varieties                         | 7     |

| 3.0  | Architectural Overview                                                 | 9     |

| 4.0  | Memory Organization                                                    | 15    |

| 5.0  | I/O Ports                                                              | 29    |

| 6.0  | Timer0 Module                                                          | 43    |

| 7.0  | Timer1 Module                                                          | 46    |

| 8.0  | Timer2 Module                                                          | 50    |

| 9.0  | Comparator Module<br>Voltage Reference Module                          | 53    |

| 10.0 | Voltage Reference Module                                               | 59    |

| 11.0 | Capture/Compare/PWM (CCP) Module                                       | 61    |

| 12.0 | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) Module | 67    |

| 13.0 | Data EEPROM Memory                                                     | 87    |

| 14.0 | Special Features of the CPU                                            | 91    |

| 15.0 | Instruction Set Summary                                                | . 107 |

| 16.0 | Development Support                                                    | . 121 |

| 17.0 | Electrical Specifications                                              | . 127 |

| 18.0 | DC and AC Characteristics Graphs and Tables                            | . 143 |

| 19.0 | Packaging Information                                                  | . 157 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |

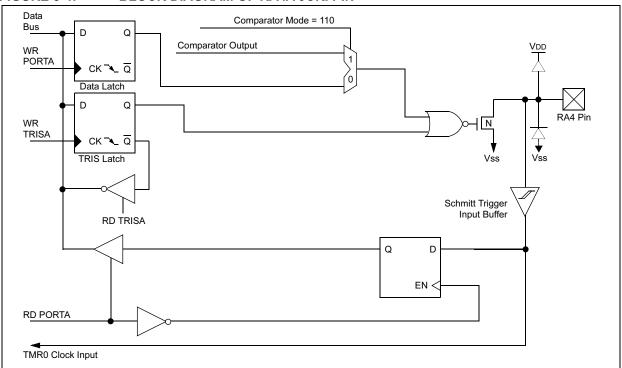

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |

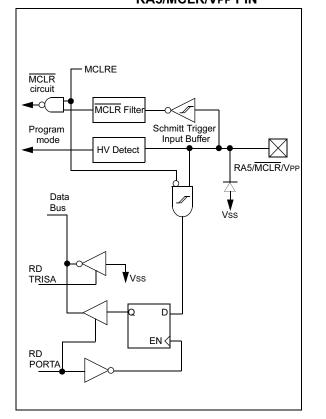

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |

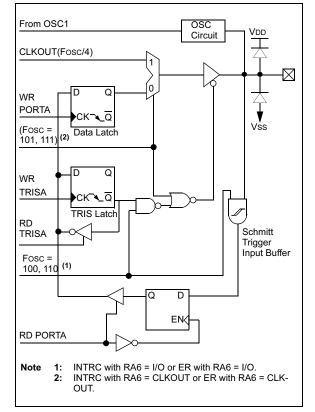

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

# TABLE 2-1:PIC16F62X PINOUT DESCRIPTION (CONTINUED)

| Name                                                  | Function | Input Type                    | Output Type | Description                                                                                                                                                                          |  |  |

|-------------------------------------------------------|----------|-------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RB4/PGM                                               | RB4      | TTL                           | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                       |  |  |

|                                                       | PGM      | ST                            | _           | Low voltage programming input pin. Interrupt-<br>on-pin change. When low voltage program-<br>ming is enabled, the interrupt-on-pin change<br>and weak pull-up resistor are disabled. |  |  |

| RB5                                                   | RB5      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |  |  |

| RB6/T1OSO/T1CKI/PGC                                   | RB6      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |  |  |

|                                                       | T10SO    | —                             | XTAL        | Timer1 oscillator output.                                                                                                                                                            |  |  |

|                                                       | T1CKI    | ST                            | —           | Timer1 clock input.                                                                                                                                                                  |  |  |

|                                                       | PGC      | ST                            | _           | ICSP™ Programming Clock.                                                                                                                                                             |  |  |

| RB7/T1OSI/PGD                                         | RB7      | TTL                           | CMOS        | Bi-directional I/O port. Interrupt-on-pin<br>change. Can be software programmed for<br>internal weak pull-up.                                                                        |  |  |

|                                                       | T1OSI    | XTAL                          | _           | Timer1 oscillator input. Wake-up from SLEEP<br>on pin change. Can be software programmed<br>for internal weak pull-up.                                                               |  |  |

|                                                       | PGD      | ST                            | CMOS        | ICSP Data I/O                                                                                                                                                                        |  |  |

| Vss                                                   | Vss      | Power                         | _           | Ground reference for logic and I/O pins                                                                                                                                              |  |  |

| Vdd                                                   | Vdd      | Power                         | —           | Positive supply for logic and I/O pins                                                                                                                                               |  |  |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Input |          | CMOS = CI<br>I = In<br>OD = O |             | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                               |  |  |

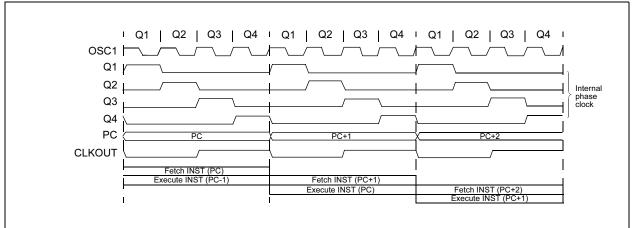

## 2.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN/RA7 pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 2-2.

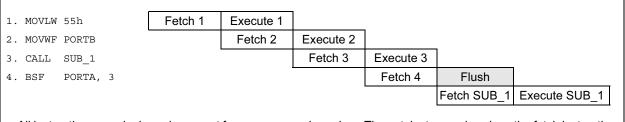

# 2.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change, (e.g., GOTO) then two cycles are required to complete the instruction (Example 2-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 2-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 2-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 3.2.2.1 STATUS Register

The STATUS register, shown in Register 3-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory (SRAM).

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect any STATUS bit. For other instructions, not affecting any STATUS bits, see the "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

|         | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                                         | R/W-0 | R-1                        | R-1                           | R/W-x | R/W-x                          | R/W-x |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|----------------------------|-------------------------------|-------|--------------------------------|-------|--|--|--|

|         | IRP                                                                                                                                                                                                                                                                          | RP1                                           | RP0   | TO                         | PD                            | Z     | DC                             | С     |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                        |                                               |       |                            |                               |       |                                | bit 0 |  |  |  |

| bit 7   | 1 = Bank 2                                                                                                                                                                                                                                                                   | ter Bank Se<br>, 3 (100h - 1<br>, 1 (00h - FF | FFh)  | d for indired              | t addressing)                 |       |                                |       |  |  |  |

| bit 6-5 | <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h - 7Fh)<br>01 = Bank 1 (80h - FFh)<br>10 = Bank 2 (100h - 17Fh)<br>11 = Bank 3 (180h - 1FFh)                                                                                      |                                               |       |                            |                               |       |                                |       |  |  |  |

| bit 4   | TO: Timeout bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT timeout occurred                                                                                                                                                                |                                               |       |                            |                               |       |                                |       |  |  |  |

| bit 3   |                                                                                                                                                                                                                                                                              | ower-up or t                                  | •     |                            | on                            |       |                                |       |  |  |  |

| bit 2   | <ul> <li>0 = By execution of the SLEEP instruction</li> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                               |                                               |       |                            |                               |       |                                |       |  |  |  |

| bit 1   | <ul> <li>DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)</li> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul> |                                               |       |                            |                               |       |                                |       |  |  |  |

| bit 0   | <ul> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                               |                                               |       |                            |                               |       |                                |       |  |  |  |

|         | <b>Note 1:</b> For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.                     |                                               |       |                            |                               |       |                                |       |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                      |                                               |       |                            |                               |       |                                |       |  |  |  |

|         | R = Reada<br>-n = Value                                                                                                                                                                                                                                                      |                                               |       | Vritable bit<br>Bit is set | U = Unimple<br>'0' = Bit is c |       | it, read as '<br>x = Bit is ui |       |  |  |  |

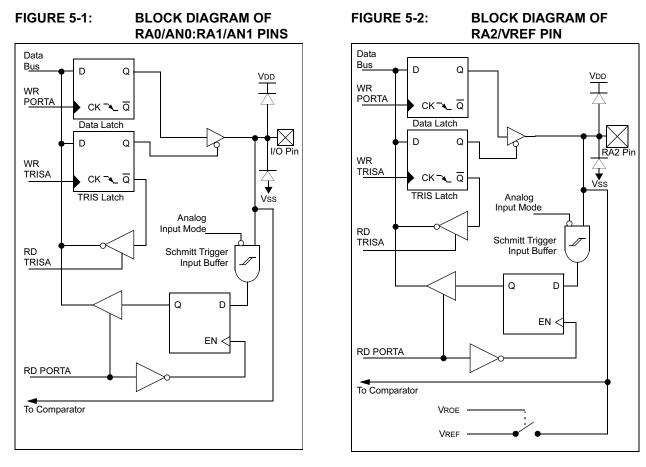

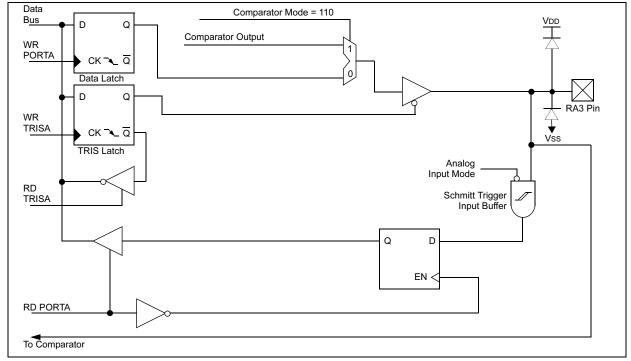

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3 PIN

# BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

FIGURE 5-6:

BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

## 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on Bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on Bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., Bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if Bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings:PORTB<7:4> Inputs

;

;

; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-up and are not ;connected to other circuitry ;

| BCF STATUS, RPO ;                                                                                              |                                                 | PORT latchPORT Pins |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|

| BCF PORTB, /;01pp pppp 11pp pppBSF STATUS, RP0;BCF TRISB, 7;10pp pppp 11pp pppBCF TRISB, 6;10pp pppp 10pp pppp | BCF PORTB, 7<br>BSF STATUS, RP0<br>BCF TRISB, 7 |                     |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

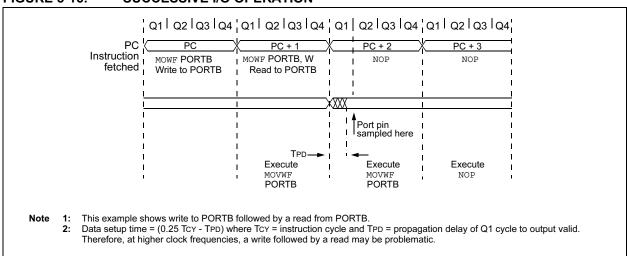

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-16: SUCCESSIVE I/O OPERATION

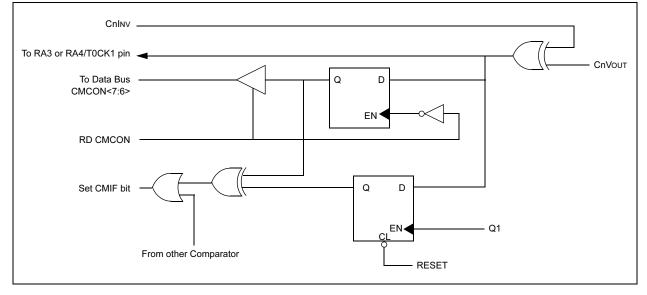

# 9.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4/T0CK1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4/T0CK1 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 9-3: COMPARATOR OUTPUT BLOCK DIAGRAM

| BAUD     | Fosc = 20 M | Hz     |                    | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _      | _                  | NA     | _      |                    | NA     | _      |                    |

| 1.2      | 1.221       | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404       | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2       | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5       | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5       | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221       | —      | 255                | 0.977  |        | 255                | 0.6104 |        | 255                |

| TABLE 12-4: | BAUD RATES FOR ASYNCHRONOUS MODE ( | BRGH=0) |

|-------------|------------------------------------|---------|

|-------------|------------------------------------|---------|

| BAUD     | Fosc = 7.15909 MHz |        | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|--------------------|--------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD              | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA                 | _      | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203              | +0.23% | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380              | -0.83% | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322              | -2.90% | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64              | -2.90% | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA                 | _      | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 500      | NA                 |        | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9              | _      | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437              | _      | 255                | 0.3094     |        | 255                | 3.906  |        | 255                |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |         | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3         | 0.301        | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2         | 1.190        | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4         | 2.432        | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6         | 9.322        | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2        | 18.64        | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8        | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96          | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH        | 55.93        | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW         | 0.2185       | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

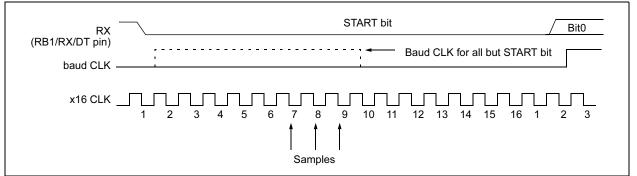

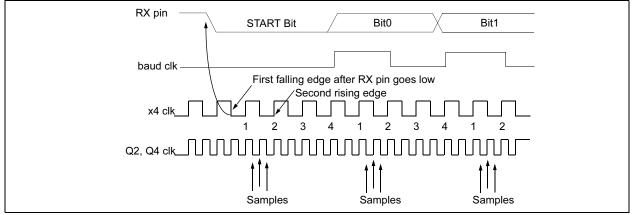

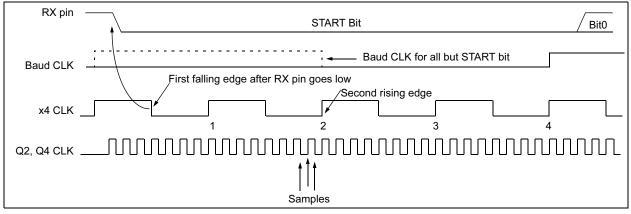

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

## FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

# FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

## FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

## 14.5 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Detect (BOD)

#### 14.5.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

### 14.5.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) timeout on power-up only, from POR or Brown-out Detect Reset. The PWRT operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. The PWRT should always be enabled when Brown-out Detect Reset is enabled. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 14.5.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

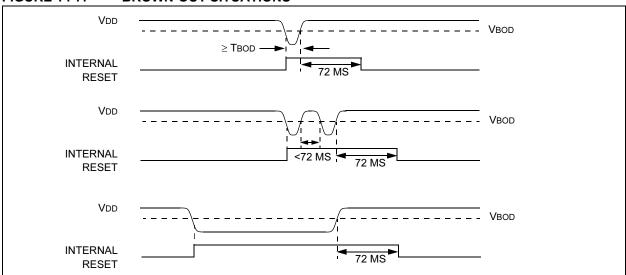

#### 14.5.4 BROWN-OUT DETECT (BOD) RESET

The PIC16F62X members have on-chip BOD circuitry. A configuration bit, BODEN, can disable (if clear/ programmed) or enable (if set) the BOD Reset circuitry. If VDD falls below VBOD for longer than TBOD, the brown-out situation will RESET the chip. A RESET is not guaranteed to occur if VDD falls below VBOD for shorter than TBOD. VBOD and TBOD are defined in Table 17-1 and Table 17-6, respectively.

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above VBOD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below VBOD while the Power-up Timer is running, the chip will go back into a Brown-out Detect Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Detect is enabled. Figure 14-7 shows typical Brown-out situations.

FIGURE 14-7: BROWN-OUT SITUATIONS

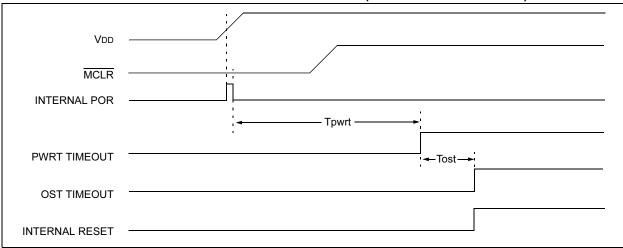

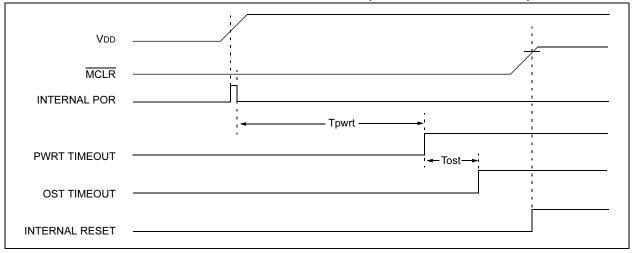

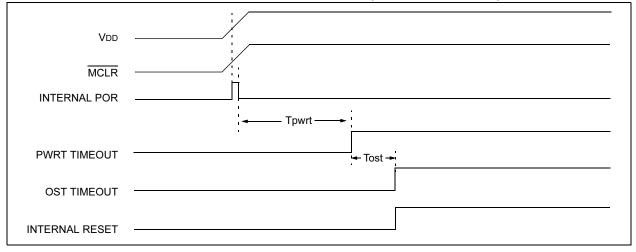

## 14.5.5 TIMEOUT SEQUENCE

On power-up the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired. Then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in ER mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 14-8, Figure 14-9 and Figure 14-10 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16F62X device operating in parallel.

Table 14-7 shows the RESET conditions for some special registers, while Table 14-8 shows the RESET conditions for all the registers.

#### 14.5.6 POWER CONTROL (PCON) STATUS REGISTER

The Power Control/STATUS register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{BOD}$  (Brown-out).  $\overline{BOD}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOD} = 0$  indicating that a brown-out has occurred. The  $\overline{BOD}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Detect  |            |  |  |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|--|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | Reset             | from SLEEP |  |  |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |  |  |

| ER, INTRC, EC            | 72 ms             | _         | 72 ms             | —          |  |  |  |

## TABLE 14-4: TIMEOUT IN VARIOUS SITUATIONS

| TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE |     |    |    |                                    |

|-----------------------------------------------------|-----|----|----|------------------------------------|

| POR                                                 | BOD | то | PD |                                    |

| 0                                                   | Х   | 1  | 1  | Power-on Reset                     |

| 0                                                   | х   | 0  | х  | Illegal, TO is set on POR          |

| 0                                                   | х   | х  | 0  | Illegal, PD is set on POR          |

| 1                                                   | 0   | Х  | Х  | Brown-out Detect Reset             |

| 1                                                   | 1   | 0  | u  | WDT Reset                          |

| 1                                                   | 1   | 0  | 0  | WDT Wake-up                        |

| 1                                                   | 1   | u  | u  | MCLR Reset during normal operation |

| 1                                                   | 1   | 1  | 0  | MCLR Reset during SLEEP            |

### TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Legend: u = unchanged, x = unknown.

#### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     | _     | -     | OSCF  | Reset | POR   | BOD   | 1-0x                  | u-uq                                           |

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect Reset and Watchdog Timer Reset during normal operation.

FIGURE 14-9: TIMEOUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 14-10: TIMEOUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

© 2003 Microchip Technology Inc.

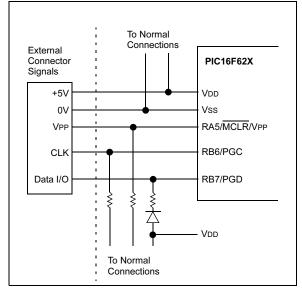

# 14.12 In-Circuit Serial Programming

The PIC16F62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 14-18.

#### FIGURE 14-18: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## 14.13 Low Voltage Programming

The LVP bit of the configuration word, enables the low voltage programming. This mode allows the microcontroller to be programmed via ICSP using only a 5V source. This mode removes the requirement of VIHH to be placed on the MCLR pin. The LVP bit is normally erased to '1', which enables the low voltage programming. In this mode, the RB4/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. The device will enter Programming mode when a '1' is placed on the RB4/PGM pin. The HV Programming mode is still available by placing VIHH on the MCLR pin.

- Note 1: While in this mode, the RB4 pin can no longer be used as a general purpose I/O pin.

- 2: VDD must be 5.0V <u>+</u>10% during erase/ program operations while in low voltage Programming mode.

If Low voltage Programming mode is not used, the LVP bit can be programmed to a '0', and RB4/PGM becomes a digital I/O pin. To program the device, VIHH must be placed onto MCLR during programming. The LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit cannot be programmed when programming is entered with RB4/PGM.

It should be noted, that once the LVP bit is programmed to 0, High voltage Programming mode can be used to program the device.

# PIC16F62X

| INCF             | Increment f                                                                                                                                                          | INCFSZ           | Increment f, Skip if 0                                                                                                                                               |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                            | Syntax:          | [label] INCFSZ f,d                                                                                                                                                   |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                   | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                   |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                     |  |  |  |

| Status Affected: | Z                                                                                                                                                                    | Status Affected: | None                                                                                                                                                                 |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                    | Encoding:        | 00 1111 dfff ffff                                                                                                                                                    |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result<br>is placed in the W register. If 'd'<br>is 1 the result is placed back in<br>register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result<br>is placed in the W register. If 'd'<br>is 1 the result is placed back in<br>register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                    |                  | If the result is 0, the next instruction, which is already                                                                                                           |  |  |  |

| Cycles:          | 1                                                                                                                                                                    |                  | fetched, is discarded. A NOP is                                                                                                                                      |  |  |  |

| Example          | INCF REG1, 1                                                                                                                                                         |                  | executed instead making it a                                                                                                                                         |  |  |  |

|                  | Before Instruction                                                                                                                                                   |                  | two-cycle instruction.                                                                                                                                               |  |  |  |

|                  | REG1 = 0xFF                                                                                                                                                          | Words:           | 1                                                                                                                                                                    |  |  |  |

|                  | Z = 0<br>After Instruction                                                                                                                                           | Cycles:          | 1 <sup>(2)</sup>                                                                                                                                                     |  |  |  |

|                  | $\begin{array}{r} \text{REG1} = 0 \\ \text{Z} \end{array} = 1 \end{array}$                                                                                           | Example          | HERE INCFSZ REG1, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                             |  |  |  |

|                  |                                                                                                                                                                      |                  | Before Instruction<br>PC = address HERE                                                                                                                              |  |  |  |

PC = address HERE After Instruction REG1 = REG1 + 1 if CNT = 0, PC = address CONTINUE if REG1≠ 0, PC = address HERE +1

-

| SUBWF               | Subtract W from f                                                                                                                                                                     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                            |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                    |

| Operation:          | (f) - (W) $\rightarrow$ (dest)                                                                                                                                                        |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                              |

| Encoding:           | 00 0010 dfff ffff                                                                                                                                                                     |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0<br>the result is stored in the W register.<br>If 'd' is 1 the result is stored back in<br>register 'f'. |

| Words:              | 1                                                                                                                                                                                     |

| Cycles:             | 1                                                                                                                                                                                     |

| Example 1:          | SUBWF REG1, 1                                                                                                                                                                         |

|                     | Before Instruction<br>REG1 = 3 $W = 2$ $C = ?$ After Instruction<br>REG1 = 1 $W = 2$ $C = 1; result is positive$ $Z = DC = 1$                                                         |

| Example 2:          | Before Instruction                                                                                                                                                                    |

|                     | REG1 = 2<br>W = 2<br>C = ?                                                                                                                                                            |

|                     | After Instruction                                                                                                                                                                     |

|                     | REG1 = 0<br>W = 2<br>C = 1; result is zero<br>Z = DC = 1                                                                                                                              |

| Example 3:          | Before Instruction                                                                                                                                                                    |

|                     | REG1 = 1<br>W = 2<br>C = ?                                                                                                                                                            |

|                     | After Instruction                                                                                                                                                                     |

|                     | REG1 = 0xFF $W = 2$ $C = 0; result is negative$ $Z = DC = 0$                                                                                                                          |

| SWAPF                                                                                                              | Swap Nibbles in f                                                                                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                                                                            | [label] SWAPF f,d                                                                                                                                                                  |  |  |  |

| Operands:                                                                                                          | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                 |  |  |  |

| Operation:                                                                                                         | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                                  |  |  |  |

| Status Affected:                                                                                                   | None                                                                                                                                                                               |  |  |  |

| Encoding:                                                                                                          | 00 1110 dfff ffff                                                                                                                                                                  |  |  |  |

| Description:                                                                                                       | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0 the result is placed in W<br>register. If 'd' is 1 the result is<br>placed in register 'f'.           |  |  |  |

| Words:                                                                                                             | 1                                                                                                                                                                                  |  |  |  |

| Cycles:                                                                                                            | 1                                                                                                                                                                                  |  |  |  |

| Example                                                                                                            | SWAPF REG1, 0                                                                                                                                                                      |  |  |  |

|                                                                                                                    | Before Instruction                                                                                                                                                                 |  |  |  |

|                                                                                                                    | REG1 = 0xA5                                                                                                                                                                        |  |  |  |

|                                                                                                                    | After Instruction                                                                                                                                                                  |  |  |  |

|                                                                                                                    | REG1 = 0xA5<br>W = 0x5A                                                                                                                                                            |  |  |  |

| TRIS                                                                                                               | Load TRIS Register                                                                                                                                                                 |  |  |  |

| Syntax:                                                                                                            | [ <i>label</i> ] TRIS f                                                                                                                                                            |  |  |  |

| Operands:                                                                                                          | $5 \le f \le 7$                                                                                                                                                                    |  |  |  |

| Operation:                                                                                                         | $(W) \rightarrow TRIS$ register f;                                                                                                                                                 |  |  |  |

| Status Affected:                                                                                                   | None                                                                                                                                                                               |  |  |  |

| Encoding:                                                                                                          | 00 0000 0110 0fff                                                                                                                                                                  |  |  |  |

| Description:                                                                                                       | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and<br>writable, the user can directly<br>address them. |  |  |  |

| Words:                                                                                                             | 1                                                                                                                                                                                  |  |  |  |

| Cycles:                                                                                                            | 1                                                                                                                                                                                  |  |  |  |

| Example                                                                                                            |                                                                                                                                                                                    |  |  |  |

| To maintain upward<br>compatibility with future<br>PICmicro <sup>®</sup> products, do not<br>use this instruction. |                                                                                                                                                                                    |  |  |  |

# PIC16F62X

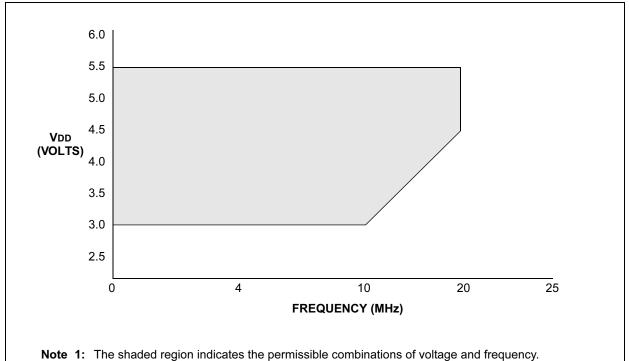

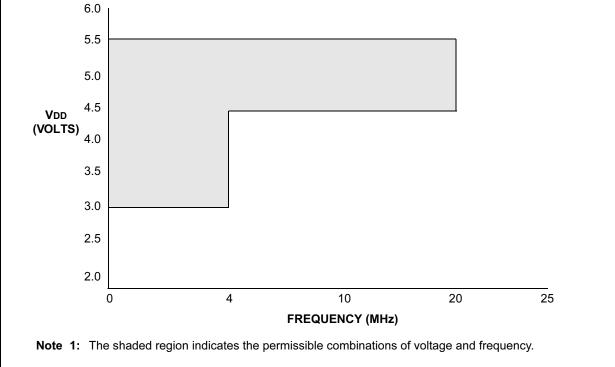

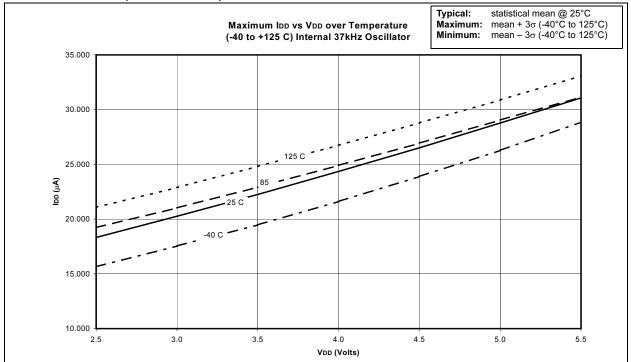

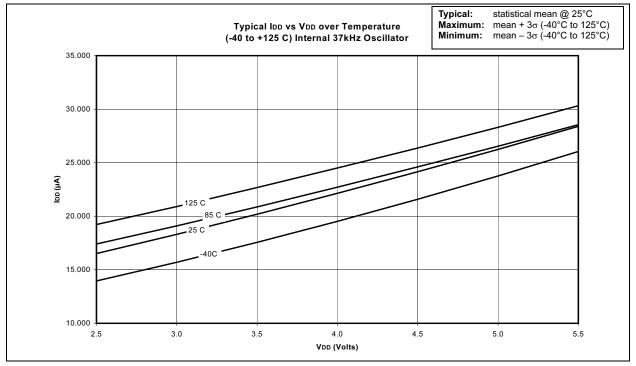

**Note:** The graphs and tables provided in this section are for design guidance and are not tested.

# FIGURE 18-24: MAXIMUM IDD vs VDD OVER TEMPERATURE (-40 TO +125°C) INTERNAL 37 kHz OSCILLATOR

FIGURE 18-25: TYPICAL IDD VS VDD OVER TEMPERATURE (-40 TO +125°C) INTERNAL 37 kHz OSCILLATOR

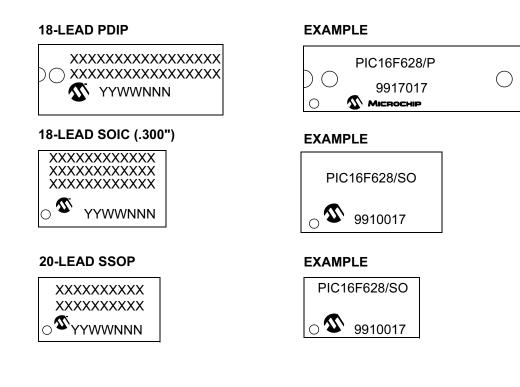

# **19.0 PACKAGING INFORMATION**

# **19.1** Package Marking Information

| Legend: | MMM | Microchip part number information                                                                                                                                                   |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | XXX | Customer specific information(1)                                                                                                                                                    |

|         | YY  | Year code (last 2 digits of calendar year)                                                                                                                                          |

|         | WW  | Week code (week of January 1 is week '01')                                                                                                                                          |

|         | NNN | Alphanumeric traceability code                                                                                                                                                      |

| Note:   |     | vent the full Microchip part number cannot be marked on one line, it will be carried<br>he next line thus limiting the number of available characters for customer specific<br>ion. |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.