Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627a-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

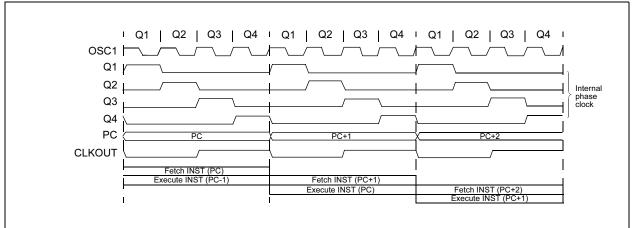

#### 2.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN/RA7 pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 2-2.

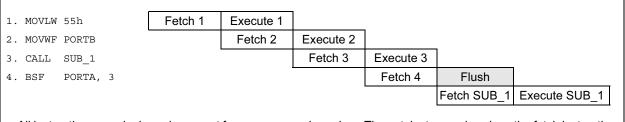

# 2.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change, (e.g., GOTO) then two cycles are required to complete the instruction (Example 2-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 2-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 2-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

NOTES:

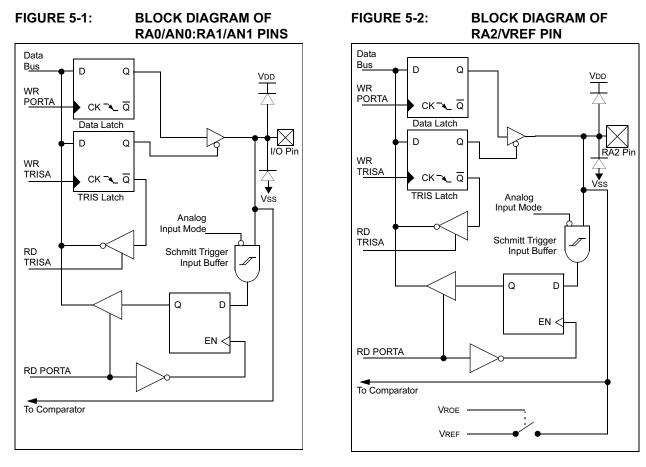

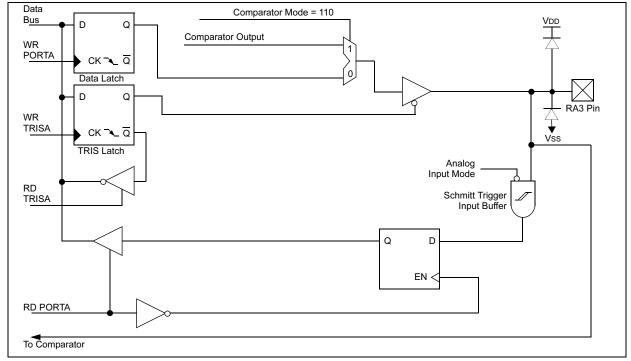

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3 PIN

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000       | xxxu 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

TABLE 5-2:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTA<sup>(1)</sup>

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTA.

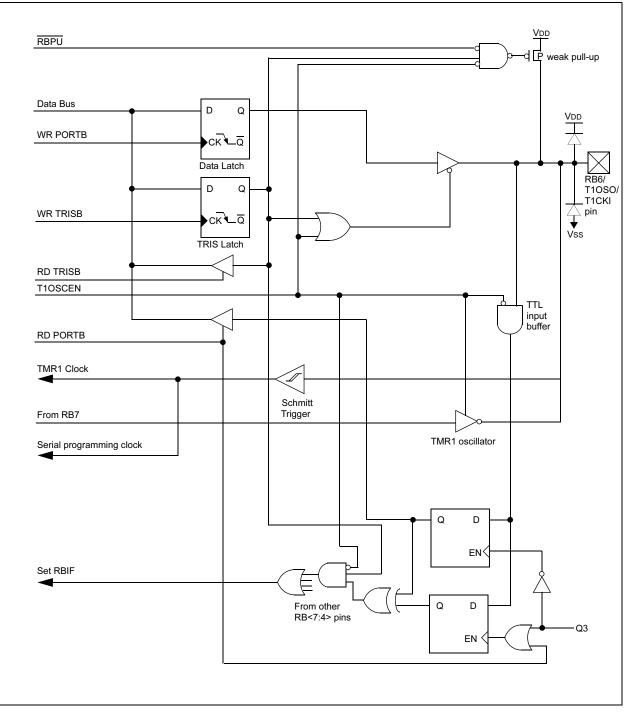

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

PORTB is multiplexed with the external interrupt, USART, CCP module and the TMR1 clock input/output. The standard port functions and the alternate port functions are shown in Table 5-3. Alternate port functions override TRIS setting when enabled.

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-onchange comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | when a read operation is being executed       |  |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

© 2003 Microchip Technology Inc.

| <b>REGISTER 8-1:</b> | REGISTER 8-1: T2CON: TIMER CONTROL REGISTER (ADDRESS: 12h) |                                                      |             |             |           |        |         |         |  |  |  |  |  |

|----------------------|------------------------------------------------------------|------------------------------------------------------|-------------|-------------|-----------|--------|---------|---------|--|--|--|--|--|

|                      | U-0                                                        | R/W-0                                                | R/W-0       | R/W-0       | R/W-0     | R/W-0  | R/W-0   | R/W-0   |  |  |  |  |  |

|                      | _                                                          | TOUTPS3                                              | TOUTPS2     | TOUTPS1     | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |  |  |  |

|                      | bit 7                                                      |                                                      |             |             |           |        |         | bit 0   |  |  |  |  |  |

|                      |                                                            |                                                      |             |             |           |        |         |         |  |  |  |  |  |

| bit 7                | Unimplem                                                   | Unimplemented: Read as '0'                           |             |             |           |        |         |         |  |  |  |  |  |

| bit 6-3              | TOUTPS3:                                                   | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |             |             |           |        |         |         |  |  |  |  |  |

|                      | 0000 = 1:1                                                 | 0000 = 1:1 Postscale Value                           |             |             |           |        |         |         |  |  |  |  |  |

|                      | 0001 = 1:2                                                 | Postscale V                                          | alue        |             |           |        |         |         |  |  |  |  |  |

|                      | •                                                          |                                                      |             |             |           |        |         |         |  |  |  |  |  |

|                      | •                                                          |                                                      |             |             |           |        |         |         |  |  |  |  |  |

|                      | 1111 = 1:1                                                 | 6 Postscale                                          |             |             |           |        |         |         |  |  |  |  |  |

|                      |                                                            |                                                      |             |             |           |        |         |         |  |  |  |  |  |

| bit 2                | TMR2ON:                                                    | Timer2 On bi                                         | it          |             |           |        |         |         |  |  |  |  |  |

|                      | 1 = Timer2                                                 | is on                                                |             |             |           |        |         |         |  |  |  |  |  |

|                      | 0 = Timer2                                                 | is off                                               |             |             |           |        |         |         |  |  |  |  |  |

| bit 1-0              | T2CKPS1:                                                   | T2CKPS0: T                                           | imer2 Clock | Prescale Se | lect bits |        |         |         |  |  |  |  |  |

|                      | 00 = 1:1 P                                                 | rescaler Valu                                        | е           |             |           |        |         |         |  |  |  |  |  |

|                      |                                                            | rescaler Valu                                        | -           |             |           |        |         |         |  |  |  |  |  |

|                      | 1x = 1:16                                                  | Prescaler Val                                        | ue          |             |           |        |         |         |  |  |  |  |  |

|                      | <b></b>                                                    |                                                      |             |             |           |        |         |         |  |  |  |  |  |

|                      | Legend:                                                    |                                                      |             |             |           |        |         |         |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE         | PEIE           | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF        | CMIF           | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE        | CMIE           | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod  | lule's registe | r       |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

# 9.0 COMPARATOR MODULE

The Comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The On-chip Voltage Reference (Section 10.0) can also be an input to the comparators.

The CMCON register, shown in Register 9-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 9-1.

### REGISTER 9-1: CMCON REGISTER (ADDRESS: 01Fh)

| IER 9-1. |                                                                                                                                              | EGISTER                                                                              | (ADDRES    | 53. UTFII)   |           |             |               |       |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------|--------------|-----------|-------------|---------------|-------|--|--|

|          | R-0                                                                                                                                          | R-0                                                                                  | R/W-0      | R/W-0        | R/W-0     | R/W-0       | R/W-0         | R/W-0 |  |  |

|          | C2OUT                                                                                                                                        | C10UT                                                                                | C2INV      | C1INV        | CIS       | CM2         | CM1           | CM0   |  |  |

|          | bit 7                                                                                                                                        | 1                                                                                    | •          |              |           | -           | •             | bit 0 |  |  |

| bit 7    | <b>C2OUT</b> : Cor<br><u>When C2IN</u><br>1 = C2 VIN+<br>0 = C2 VIN+                                                                         | > C2 VIN-                                                                            | utput      |              |           |             |               |       |  |  |

| bit 6    | When C2IN*           1 = C2 VIN+           0 = C2 VIN+           C1OUT: Cor           When C1IN*           1 = C1 VIN+           0 = C1 VIN+ | < C2 VIN-<br>> C2 VIN-<br>mparator 1 Or<br><u>V = 0:</u><br>> C1 VIN-                | utput      |              |           |             |               |       |  |  |

|          | <u>When C1IN</u><br>1 = C1 Vin+<br>0 = C1 Vin+                                                                                               | < C1 VIN-                                                                            |            |              |           |             |               |       |  |  |

| bit 5    | 1 = C2 Outp                                                                                                                                  | nparator 2 Ou<br>out inverted<br>out not inverte                                     |            | n            |           |             |               |       |  |  |

| bit 4    | 1 = C1 Outp                                                                                                                                  | nparator 1 Ou<br>out inverted<br>out not inverte                                     |            | n            |           |             |               |       |  |  |

| bit 3    | <u>When CM2:</u><br>Then:<br>1 = C1 VIN-                                                                                                     | rator Input Sv<br><u>CM0: = 001</u><br>connects to F<br>connects to F                | RA3        |              |           |             |               |       |  |  |

|          | C2 VIN-<br>0 = C1 VIN-                                                                                                                       | <u>CM0 = 010</u><br>connects to F<br>connects to F<br>connects to F<br>connects to F | RA2<br>RA0 |              |           |             |               |       |  |  |

| bit 2-0  | <b>CM2:CM0</b> : Comparator Mode<br>Figure 9-1 shows the Comparator modes and CM2:CM0 bit settings                                           |                                                                                      |            |              |           |             |               |       |  |  |

|          | Legend:                                                                                                                                      |                                                                                      |            |              |           |             |               |       |  |  |

|          | R = Reada                                                                                                                                    | ble bit                                                                              | W = V      | Vritable bit | U = Unimp | plemented b | it, read as ' | 0'    |  |  |

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

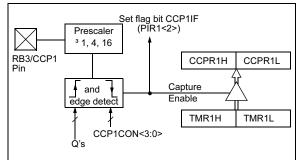

# 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the Interrupt Request Flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 11.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# TABLE 11-2:CAPTURE MODE OPERATION<br/>BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 11-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

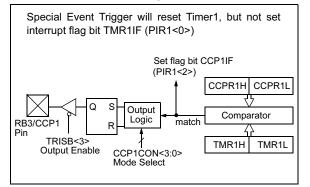

#### 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 11-1: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 11.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an output by clearing the TRISB<3> bit.

Note: Clearing the CCP1CON register will force the RB3/CCP1 compare output latch to the default low level. This is not the data latch.

| BAUD     | Fosc = 20 MHz |        | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|---------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD         | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615         | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230        | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878        | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818        | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636       | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250           | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625           | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250          | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 MHz |        | SPBRG              | 5.068 MHz |         | SPBRG              | 4 MHz    |         | SPBRG              |

|----------|-----------------|--------|--------------------|-----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) | KBAUD           | ERROR  | value<br>(decimal) | KBAUD     | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520           | -0.83% | 46                 | 9598.485  | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454          | +1.32% | 22                 | 18632.35  | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286          | -2.90% | 11                 | 39593.75  | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930          | -2.90% | 7                  | 52791.67  | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860         | -2.90% | 3                  | 105583.3  | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA              | _      | _                  | 316750    | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA              | _      | _                  | NA        | _       | _                  | NA       | _       | _                  |

| 1250000  | NA              |        | —                  | NA        | —       | _                  | NA       | —       |                    |

| BAUD        | Fosc = 3.579 | osc = 3.579 MHz SPBRG 1 |                    | 1 MHz   |          | SPBRG              | 32.768 MHz |       | SPBRG              |

|-------------|--------------|-------------------------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR                   | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600        | 9725.543     | 1.308%                  | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200       | 18640.63     | -2.913%                 | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400       | 37281.25     | -2.913%                 | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600       | 55921.88     | -2.913%                 | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200      | 111243.8     | -2.913%                 | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000      | 223687.5     | -10.525%                | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000      | NA           | _                       | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000     | NA           | —                       | —                  | NA      | —        | —                  | NA         | NA    | NA                 |

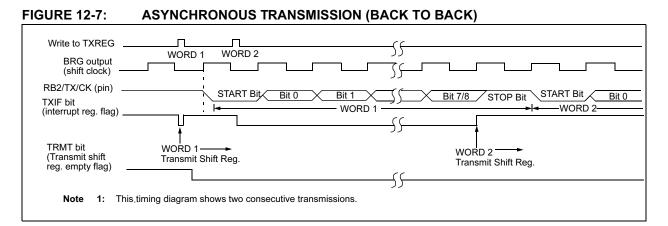

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                               | Bit 7     | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on<br>all other<br>RESETS |

|---------|------------------------------------|-----------|-------------------------|-------|-------|-------|--------|--------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF      | CMIF                    | RCIF  | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN      | RX9                     | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG                              | USART Tra | USART Transmit Register |       |       |       |        |        |           | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE      | CMIE                    | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC      | TX9                     | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |           |                         |       |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission. NOTES:

#### 13.3 READING THE EEPROM DATA MEMORY

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>). The data is available, in the very next cycle, in the EEDATA register; therefore it can be read in the next instruction. EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

### EXAMPLE 13-1: DATA EEPROM READ

| BSF   | STATUS, RPO | ; Bank 1          |

|-------|-------------|-------------------|

| MOVLW | CONFIG_ADDR | ;                 |

| MOVWF | EEADR       | ; Address to read |

| BSF   | EECON1, RD  | ; EE Read         |

| MOVF  | EEDATA, W   | ; W = EEDATA      |

| BCF   | STATUS, RPO | ; Bank 0          |

#### 13.4 WRITING TO THE EEPROM DATA MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte.

# EXAMPLE 13-2: DATA EEPROM WRITE

| WOVWW       SSN       ;         MOVWF       EECON2       ;         Write       SSN       ;         MOVWF       EECON2       ;         WOVWF       EECON2       ;         Write       AAh       ;         BSF       EECON1,WR       ;         BSF       EECON1,WR       ;         BSF       INTCON, GIE       ;         Enable       INTs. | Required<br>Sequence | MOVLW AAh<br>MOVWF EECON2<br>BSF EECON1,WR | ;<br>; Write AAh<br>; Set WR bit<br>; begin write |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|---------------------------------------------------|

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will cause the data not to be written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit in the PIR1 registers must be cleared by software.

# 13.5 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the Data EEPROM should be verified (Example 13-3) to the desired value to be written. This should be used in applications where an EEPROM bit will be stressed near the specification limit.

#### EXAMPLE 13-3: WRITE VERIFY

```

BSF

STATUS, RP0 ; Bank 1

MOVF

EEDATA, W

BSF

EECON1, RD

; Read the

; value written

; Is the value written (in W reg) and

; read (in EEDATA) the same?

SUBWF EEDATA, W

BCF STATUS, RPO ; Bank0

BTFSS STATUS, Z

; Is difference 0?

GOTO WRITE ERR

; NO, Write error

; YES, Good write

:

; Continue program

.

```

# 13.6 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence, and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

#### 13.7 DATA EEPROM OPERATION DURING CODE PROTECT

When the device is code protected, the CPU is able to read and write unscrambled data to the Data EEPROM.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                      | CALL             | Call Subroutine                                                                                                                                                                                                                |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ]BTFSS f,b                                                                                                                                                                                                                                                    | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                        |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                                                                          | Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                             |  |  |  |

|                  | $0 \le b \le 7$                                                                                                                                                                                                                                                              | Operation:       | (PC)+ 1 $\rightarrow$ TOS,                                                                                                                                                                                                     |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                      |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                                                                            |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                         | Status Affected: | None                                                                                                                                                                                                                           |  |  |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                                                            | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                              |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next<br>instruction fetched during the<br>current instruction execution, is<br>discarded and a NOP is executed<br>instead, making this a two-cycle<br>instruction. | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven bit<br>immediate address is loaded<br>into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                            |                  | instruction.                                                                                                                                                                                                                   |  |  |  |

| Cycles:          | 1 <sup>(2)</sup>                                                                                                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                              |  |  |  |

| Example          | HERE BTFSS REG1                                                                                                                                                                                                                                                              | Cycles:          | 2                                                                                                                                                                                                                              |  |  |  |

|                  | FALSE GOTO PROCESS_CODE<br>TRUE •                                                                                                                                                                                                                                            | Example          | HERE CALL THERE                                                                                                                                                                                                                |  |  |  |

|                  | •                                                                                                                                                                                                                                                                            |                  | Before Instruction<br>PC = Address HERE                                                                                                                                                                                        |  |  |  |

|                  | •<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,                                                                                                                                                                                         |                  | After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                                                |  |  |  |

|                  | PC = address FALSE<br>if FLAG<1> = 1,                                                                                                                                                                                                                                        | CLRF             | Clear f                                                                                                                                                                                                                        |  |  |  |

|                  | PC = address TRUE                                                                                                                                                                                                                                                            | Syntax:          | [label] CLRF f                                                                                                                                                                                                                 |  |  |  |

|                  |                                                                                                                                                                                                                                                                              | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                            |  |  |  |

|                  |                                                                                                                                                                                                                                                                              | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                                                                          |  |  |  |

|                  |                                                                                                                                                                                                                                                                              | Status Affected: | 7                                                                                                                                                                                                                              |  |  |  |

| Status Affected: | Z             |                                             |                            |      |

|------------------|---------------|---------------------------------------------|----------------------------|------|

| Encoding:        | 00            | 0001                                        | lfff                       | ffff |

| Description:     |               |                                             | register 'l<br>Z bit is se |      |

| Words:           | 1             |                                             |                            |      |

| Cycles:          | 1             |                                             |                            |      |

| Example          | CLRF          | REG1                                        |                            |      |

|                  | R<br>After In | Instructic<br>REG1 =<br>struction<br>REG1 = | = 0x5A                     |      |

# 16.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

# 16.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 16.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

# 16.18 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.

# 17.0 ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings†

| Ambient temperature under bias                                                                              | 40 to +125°C              |

|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                         |                           |

| Voltage on VDD with respect to Vss                                                                          |                           |

| Voltage on MCLR and RA4 with respect to Vss                                                                 |                           |

| Voltage on all other pins with respect to Vss                                                               | 0.3V to VDD + 0.3V        |

| Total power dissipation <sup>(1)</sup>                                                                      |                           |

| Maximum current out of Vss pin                                                                              |                           |

| Maximum current into VDD pin                                                                                |                           |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ±20 mA                    |

| Output clamp current, Iок (Vo < 0 or Vo >VDD)                                                               | ±20 mA                    |

| Maximum output current sunk by any I/O pin                                                                  |                           |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                     |

| Maximum current sunk by PORTA and PORTB                                                                     | 200 mA                    |

| Maximum current sourced by PORTA and PORTB                                                                  |                           |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | он) x Iон} + ∑(Vol x IoL) |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss

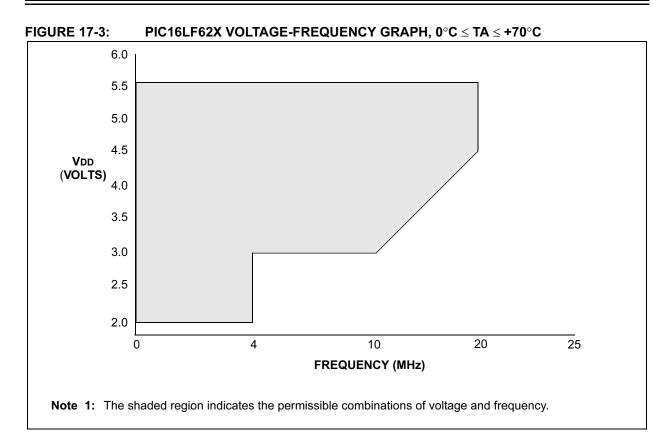

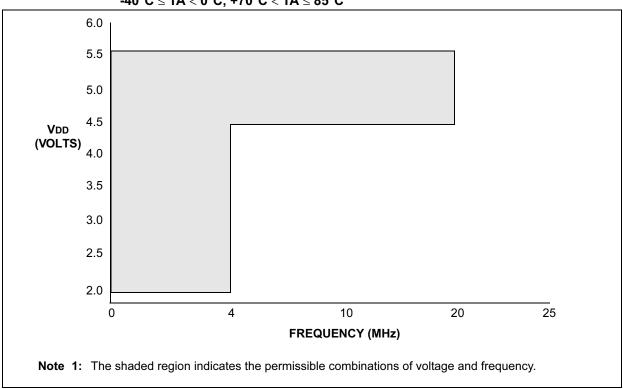

# FIGURE 17-4: PIC16LF62X VOLTAGE-FREQUENCY GRAPH, -40°C $\leq$ TA < 0°C, +70°C < TA $\leq$ 85°C

© 2003 Microchip Technology Inc.

#### 17.2 DC Characteristics: PIC16F62X (Commercial, Industrial, Extended) PIC16LF62X (Commercial, Industrial)

| DC CHAF       | RACTERIS | TICS                                      | Standard Opera<br>Operating tempe<br>Operating voltage | rature     | -40°C ≤ TA<br>0°C ≤ TA<br>-40°C ≤ TA | ≤ +85°0<br>≤ +70°<br>≤ +125 | <b>rwise stated)</b><br>C for industrial and<br>°C for commercial and<br>°C for extended<br>C spec Table 17-1 and Table 17-2 |  |  |  |

|---------------|----------|-------------------------------------------|--------------------------------------------------------|------------|--------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Sym      | Characteristic/Device                     | Min                                                    | Conditions |                                      |                             |                                                                                                                              |  |  |  |

|               | VIL      | Input Low Voltage                         |                                                        |            |                                      |                             |                                                                                                                              |  |  |  |

|               |          | I/O ports                                 |                                                        |            |                                      |                             |                                                                                                                              |  |  |  |

| D030          |          | with TTL buffer                           | Vss                                                    | _          | 0.8                                  | V                           | VDD = 4.5V to 5.5V                                                                                                           |  |  |  |

|               |          |                                           |                                                        |            | 0.15 VDD                             | V                           | otherwise                                                                                                                    |  |  |  |

| D031          |          | with Schmitt Trigger input                | Vss                                                    |            | 0.2 VDD                              | V                           |                                                                                                                              |  |  |  |

| D032          |          | MCLR, RA4/T0CKI,OSC1<br>(in ER mode)      | Vss                                                    | —          | 0.2 VDD                              | V                           | (Note1)                                                                                                                      |  |  |  |

| D033          |          | OSC1 (in XT and HS)                       | Vss                                                    | _          | 0.3 VDD                              | V                           |                                                                                                                              |  |  |  |

|               |          | OSC1 (in LP)                              | Vss                                                    | _          | 0.6 Vdd - 1.0                        | V                           |                                                                                                                              |  |  |  |

|               | Vін      | Input High Voltage                        |                                                        |            |                                      |                             | •                                                                                                                            |  |  |  |

|               |          | I/O ports                                 |                                                        |            |                                      |                             |                                                                                                                              |  |  |  |

| D040          |          | with TTL buffer                           | 2.0V                                                   | —          | Vdd                                  | V                           | VDD = 4.5V to 5.5V                                                                                                           |  |  |  |

|               |          |                                           | .25 VDD + 0.8V                                         |            | Vdd                                  | V                           | otherwise                                                                                                                    |  |  |  |

| D041          |          | with Schmitt Trigger input                | 0.8 VDD                                                | —          | VDD                                  | V                           |                                                                                                                              |  |  |  |

| D042          |          | MCLR RA4/T0CKI                            | 0.8 VDD                                                | _          | VDD                                  | V                           |                                                                                                                              |  |  |  |

| D043<br>D043A |          | OSC1 (XT, HS and LP)                      | 0.7 VDD<br>0.9 VDD                                     |            | Vdd                                  | V<br>V                      | (Noto1)                                                                                                                      |  |  |  |

| D043A         |          | OSC1 (in ER mode)                         | 50                                                     | 200        | 400                                  |                             | (Note1)<br>VDD = 5.0V, VPIN = VSS                                                                                            |  |  |  |

| D070          | IPURB    | PORTB weak pull-up<br>current             | 50                                                     | 200        | 400                                  | μA                          | VDD = 5.0V, VPIN = VSS                                                                                                       |  |  |  |

|               | lı∟      | Input Leakage Current <sup>(2), (3)</sup> |                                                        |            |                                      |                             | •                                                                                                                            |  |  |  |

|               |          | I/O ports (Except PORTA)                  |                                                        |            | ±1.0                                 | μΑ                          | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                                                                              |  |  |  |

| D060          |          | PORTA                                     | —                                                      | —          | ±0.5                                 | μΑ                          | $VSS \le VPIN \le VDD$ , pin at hi-impedance                                                                                 |  |  |  |

| D061          |          | RA4/T0CKI                                 | —                                                      | _          | ±1.0                                 | μA                          | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                     |  |  |  |

| D063          |          | OSC1, MCLR                                | —                                                      | —          | ±5.0                                 | μΑ                          | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc                                                                                |  |  |  |

|               |          |                                           |                                                        |            |                                      |                             | configuration                                                                                                                |  |  |  |

|               | Vol      | Output Low Voltage                        | 1                                                      |            | 1                                    |                             |                                                                                                                              |  |  |  |

| D080          |          | I/O ports                                 | —                                                      | —          | 0.6                                  | V                           | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                                                                          |  |  |  |

|               |          |                                           | —                                                      | _          | 0.6                                  | V                           | IOL=7.0 mA, VDD=4.5V, +125°C                                                                                                 |  |  |  |

| D083          |          | OSC2/CLKOUT (ER only)                     |                                                        | _          | 0.6<br>0.6                           | V<br>V                      | IOL=1.6 mA, VDD=4.5V, -40° to +85°C<br>IOL=1.2 mA, VDD=4.5V, +125°C                                                          |  |  |  |

|               | Voн      | Output High Voltage <sup>(3)</sup>        | 1                                                      | 1          | 0.0                                  | v                           |                                                                                                                              |  |  |  |

| D090          |          | I/O ports (Except RA4)                    | VDD - 0.7                                              | _          | _                                    | V                           | Іон=-3.0 mA. VDD=4.5V40° to +85°С                                                                                            |  |  |  |

| 2000          |          |                                           | VDD - 0.7<br>VDD - 0.7                                 | _          | _                                    | v                           | IOH=-2.5 mA, VDD=4.5V, +125°C                                                                                                |  |  |  |

| D092          |          | OSC2/CLKOUT (ER only)                     | VDD - 0.7                                              | _          | _                                    | v                           | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C                                                                                         |  |  |  |

|               |          |                                           | VDD - 0.7                                              | —          | —                                    | V                           | Іон=-1.0 mA, VDD=4.5V, +125°С                                                                                                |  |  |  |

| D150          | Vod      | Open-Drain High Voltage                   |                                                        |            | 8.5                                  | V                           | RA4 pin PIC16F62X, PIC16LF62X*                                                                                               |  |  |  |

|               |          | Capacitive Loading Specs on               | Output Pins                                            |            |                                      |                             |                                                                                                                              |  |  |  |

|               |          |                                           |                                                        |            |                                      | -                           |                                                                                                                              |  |  |  |

| D100*         | COSC2    | OSC2 pin                                  |                                                        |            | 15                                   | pF                          | In XT, HS and LP modes when external<br>clock used to drive OSC1.                                                            |  |  |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In ER oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16F62X be driven with external clock in ER mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

| Param<br>No. | Sym                   |                   | Characteristic  |         | Min                   | Тур† | Max | Units | Conditions                        |

|--------------|-----------------------|-------------------|-----------------|---------|-----------------------|------|-----|-------|-----------------------------------|

| 50*          | TccL CCP No Prescaler |                   | No Prescaler    |         | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |                       | input low time    |                 | 16F62X  | 10                    | —    | _   | ns    |                                   |

|              |                       |                   | With Prescaler  | 16LF62X | 20                    | —    | _   | ns    |                                   |

| 51*          | TccH                  | ССР               | No Prescaler    | ·       | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|              |                       | input high time   |                 | 16F62X  | 10                    |      |     | ns    |                                   |

|              |                       |                   | With Prescaler  | 16LF62X | 20                    |      |     | ns    |                                   |

| 52*          | TccP                  | CCP input perio   | CP input period |         | <u>3Tcy + 40</u><br>N | _    |     | ns    | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR                  | CCP output rise   | time            | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |                       |                   |                 | 16LF62X |                       | 25   | 45  | ns    |                                   |

| 54*          | TccF                  | CCP output fall t | ime             | 16F62X  |                       | 10   | 25  | ns    |                                   |

|              |                       |                   |                 | 16LF62X |                       | 25   | 45  | ns    |                                   |

TABLE 17-8: CAPTURE/COMPARE/PWM REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

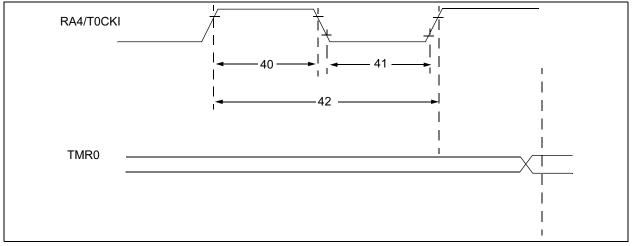

#### FIGURE 17-12: TIMER0 CLOCK TIMING

#### TABLE 17-9: TIMER0 CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Мах | Units | Conditions                            |

|--------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | —    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | _    | —   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _    | _   | ns    | N = prescale value (1, 2,<br>4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| -xx                  | ×                                                                                                                                                                                                             | / <b>XX</b>                                                                                                                                                                                                                                                                                                                                                                  | XXX                                                                                                                                                                                                                                                                                                                                                                                                                                              | Exa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | imples:                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|