Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627at-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

#### FIGURE 3-2: DATA MEMORY MAP OF THE PIC16F627 AND PIC16F628

| ndirect addr. <sup>(1)</sup> | 00h        | Indirect addr. <sup>(1)</sup> | 80h         | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> |

|------------------------------|------------|-------------------------------|-------------|-------------------------------|------|-------------------------------|

| TMR0                         | 01h        | OPTION                        | 81h         | TMR0                          | 101h | OPTION                        |

| PCL                          | 02h        | PCL                           | 82h         | PCL                           | 102h | PCL                           |

| STATUS                       | 03h        | STATUS                        | 83h         | STATUS                        | 103h | STATUS                        |

| FSR                          | 04h        | FSR                           | 84h         | FSR                           | 104h | FSR                           |

| PORTA                        | 05h        | TRISA                         | 85h         |                               | 105h |                               |

| PORTB                        | 06h        | TRISB                         | 86h         | PORTB                         | 106h | TRISB                         |

|                              | 07h        |                               | 87h         |                               | 107h |                               |

|                              | 08h        |                               | 88h         |                               | 108h |                               |

|                              | 09h        |                               | 89h         |                               | 109h |                               |

| PCLATH                       | 0Ah        | PCLATH                        | 8Ah         | PCLATH                        | 10Ah | PCLATH                        |

| INTCON                       | 0Bh        | INTCON                        | 8Bh         | INTCON                        | 10Bh | INTCON                        |

| PIR1                         | 0Ch        | PIE1                          | 8Ch         |                               | 10Ch |                               |

|                              | 0Dh        |                               | 8Dh         |                               | 10Dh |                               |

| TMR1L                        | 0Eh        | PCON                          | 8Eh         |                               | 10Eh |                               |

| TMR1H                        | 0Fh        |                               | 8Fh         |                               | 10Fh |                               |

| T1CON                        | 10h        |                               | 90h         |                               |      |                               |

| TMR2                         | 11h        |                               | 91h         |                               |      |                               |

| T2CON                        | 12h        | PR2                           | 92h         |                               |      |                               |

|                              | 13h        |                               | 93h         |                               |      |                               |

|                              | 14h        |                               | 94h         |                               |      |                               |

| CCPR1L                       | 15h        |                               | 95h         |                               |      |                               |

| CCPR1H                       | 16h        |                               | 96h         |                               |      |                               |

| CCP1CON                      | 17h        |                               | 97h         |                               |      |                               |

| RCSTA                        | 18h        | TXSTA                         | 98h         |                               |      |                               |

| TXREG                        | 19h        | SPBRG                         | 99h         |                               |      |                               |

| RCREG                        | 1Ah        | EEDATA                        | 9Ah         |                               |      |                               |

| RONEO                        | 1Bh        | EEADR                         | 9Bh         |                               |      |                               |

|                              | 1Ch        | EECON1                        | 9Ch         |                               |      |                               |

|                              | 1Dh        | EECON2 <sup>(1)</sup>         | 9Dh         |                               |      |                               |

|                              | 1Eh        |                               | 9Eh         |                               |      |                               |

| CMCON                        | 1Fh        | VRCON                         | 9Fh         |                               | 11Fh |                               |

| GINOOIN                      | 20h        |                               |             | General                       | 120h |                               |

| General                      | 2011       | General                       | A0h         | Purpose                       |      |                               |

| Purpose                      |            | Purpose                       |             | Register<br>48 Bytes          | 14Fh |                               |

| Register                     |            | Register                      |             |                               | 150h |                               |

| 80 Bytes                     |            | 80 Bytes                      |             |                               |      |                               |

| -                            | 6Fh        |                               | EFh         |                               | 16Fh |                               |

|                              | 70h        |                               | F0h         |                               | 170h |                               |

| 16 Bytes                     |            | accesses                      |             | accesses                      |      | accesses                      |

|                              | 751        | 70h-7Fh                       |             | 70h-7Fh                       | 1754 | 70h - 7Fh                     |

| Bank 0                       | 7Fh        | Bank 1                        | FFh         | Bank 2                        | 17Fh | Bank 3                        |

| Burne                        |            | _and i                        |             |                               |      |                               |

| Unimplem                     | nented dat | a memory locations, i         | read as '0' |                               |      |                               |

#### PIR1 Register 3.2.2.5

This register contains interrupt flag bits.

| Note: | Interrupt flag bits get set when an interrupt condition occurs regardless of the state of |

|-------|-------------------------------------------------------------------------------------------|

|       | 0                                                                                         |

|       | its corresponding enable bit or the global                                                |

|       | enable bit, GIE (INTCON<7>). User                                                         |

|       | software should ensure the appropriate                                                    |

|       | interrupt flag bits are clear prior to enabling                                           |

|       | an interrupt.                                                                             |

| REGISTER 3-5: | PIR1 REG | ISTER (AD | DRESS: | 0Ch) |  |

|---------------|----------|-----------|--------|------|--|

|               | R/W-0    | R/W-0     | R-0    | R-0  |  |

|       | R/W-0                                                                                                                                                          | R/W-0                       | R-0                            | R-0                        | U-0                      | R/W-0       | R/W-0          | R/W-0  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------|----------------------------|--------------------------|-------------|----------------|--------|--|--|--|

|       | EEIF                                                                                                                                                           | CMIF                        | RCIF                           | TXIF                       |                          | CCP1IF      | TMR2IF         | TMR1IF |  |  |  |

|       | bit 7                                                                                                                                                          |                             |                                |                            |                          | I           |                | bit 0  |  |  |  |

| bit 7 | EEIF: EEP                                                                                                                                                      | ROM Write                   | Operation I                    | nterrupt Flag              | a bit                    |             |                |        |  |  |  |

|       | <ul> <li>1 = The write operation completed (must be cleared in software)</li> <li>0 = The write operation has not completed or has not been started</li> </ul> |                             |                                |                            |                          |             |                |        |  |  |  |

| bit 6 | CMIF: Com                                                                                                                                                      | parator Inte                | errupt Flag b                  | oit                        |                          |             |                |        |  |  |  |

|       | •                                                                                                                                                              | •                           | has chang<br>has not ch        |                            |                          |             |                |        |  |  |  |

| bit 5 | RCIF: USA                                                                                                                                                      | RT Receive                  | Interrupt F                    | lag bit                    |                          |             |                |        |  |  |  |

|       |                                                                                                                                                                |                             | e buffer is f<br>e buffer is e |                            |                          |             |                |        |  |  |  |

| bit 4 |                                                                                                                                                                |                             |                                |                            |                          |             |                |        |  |  |  |

| DIL 4 |                                                                                                                                                                |                             | t Interrupt F<br>nit buffer is | -                          |                          |             |                |        |  |  |  |

|       |                                                                                                                                                                |                             | nit buffer is                  |                            |                          |             |                |        |  |  |  |

| bit 3 | Unimplem                                                                                                                                                       | ented: Rea                  | d as '0'                       |                            |                          |             |                |        |  |  |  |

| bit 2 | CCP1IF: C                                                                                                                                                      | CP1 Interru                 | pt Flag bit                    |                            |                          |             |                |        |  |  |  |

|       | 0 <b>= No T</b>                                                                                                                                                | IR1 register<br>MR1 regist  | r capture oc<br>er capture c   |                            | at be cleared in         | software)   |                |        |  |  |  |

|       |                                                                                                                                                                | IR1 register<br>MR1 registe | •                              | natch occuri<br>match occu | red (must be cle<br>rred | eared in so | ftware)        |        |  |  |  |

|       |                                                                                                                                                                | <u>-</u><br>in this mode    | 9                              |                            |                          |             |                |        |  |  |  |

| bit 1 | TMR2IF: T                                                                                                                                                      | MR2 to PR2                  | 2 Match Inte                   | errupt Flag b              | it                       |             |                |        |  |  |  |

|       | 1 = TMR2 1                                                                                                                                                     | o PR2 mate                  |                                | (must be cl                | eared in softwa          | re)         |                |        |  |  |  |

| bit 0 | TMR1IF: T                                                                                                                                                      | MR1 Overf                   | low Interrup                   | t Flag bit                 |                          |             |                |        |  |  |  |

|       |                                                                                                                                                                |                             | rflowed (mu<br>not overflov    |                            | ed in software)          |             |                |        |  |  |  |

|       | Legend:                                                                                                                                                        |                             |                                |                            |                          |             |                |        |  |  |  |

|       | R = Reada                                                                                                                                                      | ble bit                     | VV = V                         | Vritable bit               | U = Unimpl               | emented b   | it, read as '( | )'     |  |  |  |

|       | -n = Value                                                                                                                                                     | at POR                      | '1' = E                        | Bit is set                 | '0' = Bit is c           | leared      | x = Bit is ur  | nknown |  |  |  |

#### 3.2.2.6 PCON Register

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR Reset, WDT Reset or a Brown-out Detect.

Note: BOD is unknown on Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if BOD is cleared, indicating a brown-out has occurred. The BOD STATUS bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

#### REGISTER 3-6: PCON REGISTER (ADDRESS: 0Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-------|-----|-------|-------|

| _     | _   | —   | —   | OSCF  | _   | POR   | BOD   |

| bit 7 |     |     |     |       |     |       | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3 OSCF: INTRC/ER oscillator frequency

- 1 = 4 MHz typical<sup>(1)</sup>

- 0 = 37 KHz typical

- bit 2 Unimplemented: Read as '0'

- bit 1 **POR**: Power-on Reset STATUS bit

- 1 = No Power-on Reset occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect STATUS bit

- 1 = No Brown-out Reset occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

- **Note 1:** When in ER Oscillator mode, setting OSCF = 1 will cause the oscillator frequency to change to the frequency specified by the external resistor.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

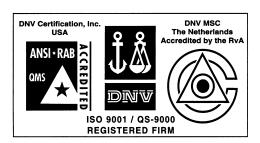

## 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

#### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

| <b>REGISTER 8-1:</b> | T2CO       | N: TIMER C    |              | REGISTER     | (ADDRESS:   | 12h)   |         |         |

|----------------------|------------|---------------|--------------|--------------|-------------|--------|---------|---------|

|                      | U-0        | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |

|                      | _          | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |

|                      | bit 7      |               |              |              |             |        |         | bit 0   |

|                      |            |               |              |              |             |        |         |         |

| bit 7                | Unimplem   | ented: Read   | as '0'       |              |             |        |         |         |

| bit 6-3              | TOUTPS3:   | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |

|                      | 0000 = 1:1 | Postscale V   | alue         |              |             |        |         |         |

|                      | 0001 = 1:2 | Postscale V   | alue         |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | 1111 = 1:1 | 6 Postscale   |              |              |             |        |         |         |

|                      |            |               |              |              |             |        |         |         |

| bit 2                | TMR2ON:    | Timer2 On bi  | it           |              |             |        |         |         |

|                      | 1 = Timer2 | is on         |              |              |             |        |         |         |

|                      | 0 = Timer2 | is off        |              |              |             |        |         |         |

| bit 1-0              | T2CKPS1:   | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |

|                      | 00 = 1:1 P | rescaler Valu | е            |              |             |        |         |         |

|                      |            | rescaler Valu | -            |              |             |        |         |         |

|                      | 1x = 1:16  | Prescaler Val | ue           |              |             |        |         |         |

|                      | <b></b>    |               |              |              |             |        |         |         |

|                      | Legend:    |               |              |              |             |        |         |         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name                          | Bit 7       | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|-------------------------------|-------------|-------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                        | GIE         | PEIE        | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1                          | EEIF        | CMIF        | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1                          | EEIE        | CMIE        | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2 Timer2 module's register |             |             |         |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON                         | _           | TOUTPS3     | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2                           | Timer2 Peri | od Register |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

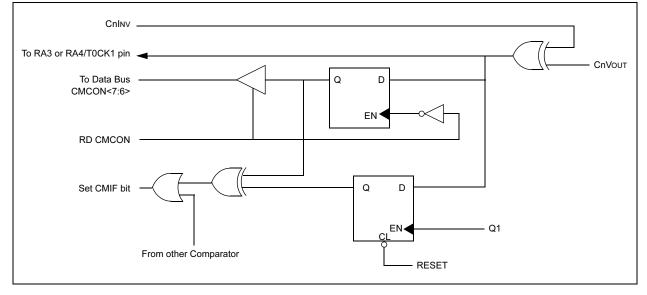

### 9.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4/T0CK1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4/T0CK1 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 9-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 12.4.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RB1/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is RESET by the hardware. In this case, it is RESET when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th

receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 12.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

| Address | Name                                   | Bit 7   | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR | Value on all<br>other<br>RESETS |

|---------|----------------------------------------|---------|----------|----------|-------|-------|--------|--------|-----------|------------------|---------------------------------|

| 0Ch     | PIR1                                   | EEIF    | CMIF     | RCIF     | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000        | 0000 -000                       |

| 18h     | RCSTA                                  | SPEN    | RX9      | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 -00x        | 0000 -00x                       |

| 1Ah     | RCREG                                  | USART R | eceive F | Register |       |       |        |        |           | 0000 0000        | 0000 0000                       |

| 8Ch     | PIE1                                   | EEPIE   | CMIE     | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | -000 0000        | -000 -000                       |

| 98h     | TXSTA                                  | CSRC    | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010        | 0000 -010                       |

| 99h     | 99h SPBRG Baud Rate Generator Register |         |          |          |       |       |        |        | 0000 0000 | 0000 0000        |                                 |

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

#### TABLE 14-7: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 1-0x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 1-uu             |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | 1-uu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 1-uu             |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-uu             |

| Brown-out Detect Reset             | 000h                  | 000x xuuu          | 1-u0             |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | u-uu             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note** 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register | Address | Power-on<br>Reset | <ul> <li>MCLR Reset during normal<br/>operation</li> <li>MCLR Reset during SLEEP</li> <li>WDT Reset</li> <li>Brown-out Detect Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP through<br/>interrupt</li> <li>Wake-up from SLEEP through<br/>WDT timeout</li> </ul> |

|----------|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| W        |         | XXXX XXXX         | սսսս սսսս                                                                                                                                                     | սսսս սսսս                                                                                                        |

| INDF     | 00h     | _                 | -                                                                                                                                                             | -                                                                                                                |

| TMR0     | 01h     | XXXX XXXX         | uuuu uuuu                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PCL      | 02h     | 0000 0000         | 0000 0000                                                                                                                                                     | PC + 1 <sup>(3)</sup>                                                                                            |

| STATUS   | 03h     | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                                                                                                                      | uuuq quuu <sup>(4)</sup>                                                                                         |

| FSR      | 04h     | XXXX XXXX         | սսսս սսսս                                                                                                                                                     | uuuu uuuu                                                                                                        |

| PORTA    | 05h     | xxxx 0000         | xxxx u000                                                                                                                                                     | xxxx 0000                                                                                                        |

| PORTB    | 06h     | xxxx xxxx         | uuuu uuuu                                                                                                                                                     | սսսս սսսս                                                                                                        |

| T1CON    | 10h     | 00 0000           | uu uuuu                                                                                                                                                       | uu uuuu                                                                                                          |

| T2CON    | 12h     | -000 0000         | -000 0000                                                                                                                                                     | -uuu uuuu                                                                                                        |

| CCP1CON  | 17h     | 00 0000           | 00 0000                                                                                                                                                       | uu uuuu                                                                                                          |

| RCSTA    | 18h     | 0000 -00x         | 0000 -00x                                                                                                                                                     | uuuu -uuu                                                                                                        |

| CMCON    | 1Fh     | 0000 0000         | 0000 0000                                                                                                                                                     | uu uuuu                                                                                                          |

| PCLATH   | 0Ah     | 0 0000            | 0 0000                                                                                                                                                        | u uuuu                                                                                                           |

| INTCON   | 0Bh     | 0000 000x         | 0000 000u                                                                                                                                                     | uuuu uqqq <sup>(2)</sup>                                                                                         |

| PIR1     | 0Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | -q (2,5)                                                                                                         |

| OPTION   | 81h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| TRISA    | 85h     | 11-1 1111         | 11 1111                                                                                                                                                       | uu-u uuuu                                                                                                        |

| TRISB    | 86h     | 1111 1111         | 1111 1111                                                                                                                                                     | սսսս սսսս                                                                                                        |

| PIE1     | 8Ch     | 0000 -000         | 0000 -000                                                                                                                                                     | uuuu -uuu                                                                                                        |

| PCON     | 8Eh     | 1-0x              | 1-uq <sup>(1,6)</sup>                                                                                                                                         | uu                                                                                                               |

| TXSTA    | 98h     | 0000 -010         | 0000 -010                                                                                                                                                     | นนนน -นนน                                                                                                        |

| EECON1   | 9Ch     | x000              | q000                                                                                                                                                          | uuuu                                                                                                             |

| VRCON    | 9Fh     | 000- 0000         | 000- 0000                                                                                                                                                     | սսս- սսսս                                                                                                        |

TABLE 14-8:

INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**4**: See Table 14-7 for RESET value for specific condition.

5: If wake-up was due to comparator input changing, then Bit 6 = 1. All other interrupts generating a wake-up will cause Bit 6 = u.

6: If RESET was due to brown-out, then Bit 0 = 0. All other RESETS will cause Bit 0 = u.

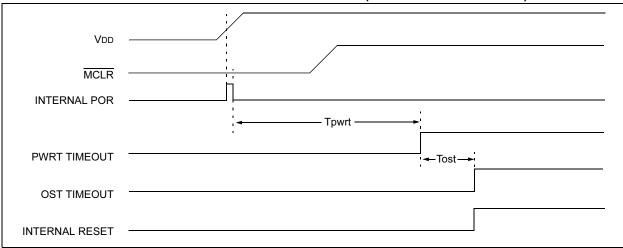

FIGURE 14-9: TIMEOUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

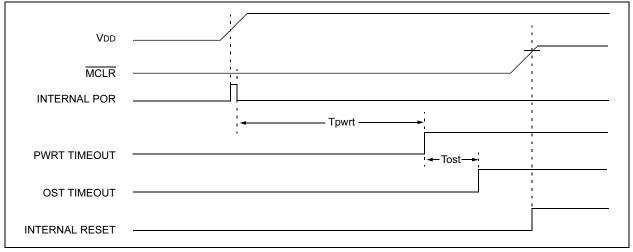

FIGURE 14-10: TIMEOUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 16.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of pre-compiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 16.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command-line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities, and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping, and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high level source debugging with the MPLAB IDE.

# 16.6 MPLAB ASM30 Assembler, Linker, and Librarian

MPLAB ASM30 assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 compiler uses the assembler to produce it's object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

#### 16.7 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC hosted environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any pin. The execution can be performed in Single-Step, Execute Until Break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and MPLAB C18 C Compilers, as well as the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

#### 16.8 MPLAB SIM30 Software Simulator

The MPLAB SIM30 software simulator allows code development in a PC hosted environment by simulating the dsPIC30F series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user defined key press, to any of the pins.

The MPLAB SIM30 simulator fully supports symbolic debugging using the MPLAB C30 C Compiler and MPLAB ASM30 assembler. The simulator runs in either a Command Line mode for automated tasks, or from MPLAB IDE. This high speed simulator is designed to debug, analyze and optimize time intensive DSP routines.

# 17.0 ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings†

| Ambient temperature under bias                                                                              | 40 to +125°C              |

|-------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                         |                           |

| Voltage on VDD with respect to Vss                                                                          |                           |

| Voltage on MCLR and RA4 with respect to Vss                                                                 |                           |

| Voltage on all other pins with respect to Vss                                                               | 0.3V to VDD + 0.3V        |

| Total power dissipation <sup>(1)</sup>                                                                      |                           |

| Maximum current out of Vss pin                                                                              |                           |

| Maximum current into VDD pin                                                                                |                           |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ±20 mA                    |

| Output clamp current, Iок (Vo < 0 or Vo >VDD)                                                               | ±20 mA                    |

| Maximum output current sunk by any I/O pin                                                                  |                           |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                     |

| Maximum current sunk by PORTA and PORTB                                                                     | 200 mA                    |

| Maximum current sourced by PORTA and PORTB                                                                  |                           |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-V | он) x Iон} + ∑(Vol x IoL) |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss

# PIC16F62X

#### 17.2 DC Characteristics: PIC16F62X (Commercial, Industrial, Extended) PIC16LF62X (Commercial, Industrial)

| DC CHARACTERISTICS |       |                                           | $ \begin{array}{ c c c c c } \hline \textbf{Standard Operating Conditions (unless otherwise stated)} \\ \hline \textbf{Operating temperature} & -40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for industrial and} \\ & 0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C} \text{ for commercial and} \\ & -40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for extended} \\ \hline \textbf{Operating voltage VDD range as described in DC spec Table 17-1 and Table 17-2} \end{array} $ |      |               |        |                                                                     |

|--------------------|-------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--------|---------------------------------------------------------------------|

| Param.<br>No.      | Sym   | Characteristic/Device                     | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Тур† | Мах           | Unit   | Conditions                                                          |

|                    | VIL   | Input Low Voltage                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        |                                                                     |

|                    |       | I/O ports                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        |                                                                     |

| D030               |       | with TTL buffer                           | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _    | 0.8           | V      | VDD = 4.5V to 5.5V                                                  |

|                    |       |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 0.15 VDD      | V      | otherwise                                                           |

| D031               |       | with Schmitt Trigger input                | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 0.2 VDD       | V      |                                                                     |

| D032               |       | MCLR, RA4/T0CKI,OSC1<br>(in ER mode)      | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —    | 0.2 VDD       | V      | (Note1)                                                             |

| D033               |       | OSC1 (in XT and HS)                       | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _    | 0.3 VDD       | V      |                                                                     |

|                    |       | OSC1 (in LP)                              | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _    | 0.6 Vdd - 1.0 | V      |                                                                     |

|                    | Vін   | Input High Voltage                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        | •                                                                   |

|                    |       | I/O ports                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        |                                                                     |

| D040               |       | with TTL buffer                           | 2.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —    | Vdd           | V      | VDD = 4.5V to 5.5V                                                  |

|                    |       |                                           | .25 VDD + 0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | Vdd           | V      | otherwise                                                           |

| D041               |       | with Schmitt Trigger input                | 0.8 VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —    | VDD           | V      |                                                                     |

| D042               |       | MCLR RA4/T0CKI                            | 0.8 VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _    | VDD           | V      |                                                                     |

| D043<br>D043A      |       | OSC1 (XT, HS and LP)                      | 0.7 VDD<br>0.9 VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Vdd           | V<br>V | (Noto1)                                                             |

| D043A              |       | OSC1 (in ER mode)                         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200  | 400           |        | (Note1)<br>VDD = 5.0V, VPIN = VSS                                   |

| D070               | IPURB | PORTB weak pull-up<br>current             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200  | 400           | μA     | VDD = 5.0V, VPIN = VSS                                              |

|                    | lı∟   | Input Leakage Current <sup>(2), (3)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        | •                                                                   |

|                    |       | I/O ports (Except PORTA)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | ±1.0          | μΑ     | Vss $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                     |

| D060               |       | PORTA                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —    | ±0.5          | μΑ     | $VSS \le VPIN \le VDD$ , pin at hi-impedance                        |

| D061               |       | RA4/T0CKI                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _    | ±1.0          | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                            |

| D063               |       | OSC1, MCLR                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —    | ±5.0          | μΑ     | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc                       |

|                    |       |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |               |        | configuration                                                       |

|                    | Vol   | Output Low Voltage                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | 1             |        |                                                                     |

| D080               |       | I/O ports                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —    | 0.6           | V      | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                 |

|                    |       |                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _    | 0.6           | V      | IOL=7.0 mA, VDD=4.5V, +125°C                                        |

| D083               |       | OSC2/CLKOUT (ER only)                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _    | 0.6<br>0.6    | V<br>V | IOL=1.6 mA, VDD=4.5V, -40° to +85°C<br>IOL=1.2 mA, VDD=4.5V, +125°C |

|                    | Voн   | Output High Voltage <sup>(3)</sup>        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1    | 0.0           | v      |                                                                     |