Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            |                                                                             |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf627at-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## PIC16F62X

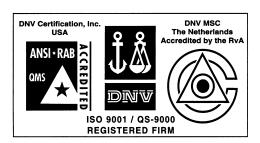

## **Pin Diagrams**

## **Device Differences**

| Device                                      | Voltage<br>Range           | Oscillator                      | Process<br>Technology<br>(Microns) |

|---------------------------------------------|----------------------------|---------------------------------|------------------------------------|

| PIC16F627                                   | 3.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16F628                                   | 3.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16LF627                                  | 2.0 - 5.5                  | (Note 1)                        | 0.7                                |

| PIC16LF628                                  | 2.0 - 5.5                  | (Note 1)                        | 0.7                                |

| Note 1: If you change from the application. | is device to another devic | e, please verify oscillator cha | aracteristics in your              |

| Address | Name   | Bit 7            | Bit 6                                         | Bit 5       | Bit 4       | Bit 3        | Bit 2        | Bit 1        | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|-----------------------------------------------|-------------|-------------|--------------|--------------|--------------|--------------|-----------------------------------------|--------------------|

| Bank 3  |        |                  |                                               |             |             |              |              |              |              |                                         |                    |

| 180h    | INDF   | Addressin ister) | ig this location                              | n uses cont | ents of FSF | R to address | s data mem   | ory (not a p | hysical reg- | XXXX XXXX                               | 25                 |

| 181h    | OPTION | RBPU             | INTEDG                                        | TOCS        | TOSE        | PSA          | PS2          | PS1          | PS0          | 1111 1111                               | 20                 |

| 182h    | PCL    | Program (        | Program Counter's (PC) Least Significant Byte |             |             |              |              |              |              |                                         | 25                 |

| 183h    | STATUS | IRP              | RP1                                           | RP0         | TO          | PD           | Z            | DC           | С            | 0001 1xxx                               | 19                 |

| 184h    | FSR    | Indirect da      | ata memory a                                  | ddress poir | nter        | . –          | -            |              | 1-           | xxxx xxxx                               | 25                 |

| 185h    | _      | Unimplem         |                                               |             |             |              |              |              |              | _                                       | _                  |

| 186h    | TRISB  | TRISB7           | TRISB6                                        | TRISB5      | TRISB4      | TRISB3       | TRISB2       | TRISB1       | TRISB0       | 1111 1111                               | 34                 |

| 187h    | _      | Unimplem         | nented                                        | •           |             | •            | •            |              |              | _                                       | —                  |

| 188h    |        | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 189h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              |                                         | _                  |

| 18Ah    | PCLATH | _                | _                                             | _           | Write buff  | er for upper | 5 bits of pr | ogram cour   | iter         | 0 0000                                  | 25                 |

| 18Bh    | INTCON | GIE              | PEIE                                          | T0IE        | INTE        | RBIE         | TOIF         | INTF         | RBIF         | 0000 000x                               | 21                 |

| 18Ch    | _      | Unimplem         | Unimplemented                                 |             |             |              |              |              |              |                                         | _                  |

| 18Dh    |        | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 18Eh    |        | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 18Fh    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 190h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 191h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 192h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              |                                         | _                  |

| 193h    | —      | Unimplem         | nented                                        |             |             |              |              |              |              |                                         | _                  |

| 194h    | —      | Unimplem         | nented                                        |             |             |              |              |              |              |                                         | _                  |

| 195h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              |                                         | _                  |

| 196h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | —                  |

| 197h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 198h    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | —                  |

| 199h    | —      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | —                  |

| 19Ah    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       |                    |

| 19Bh    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       |                    |

| 19Ch    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       |                    |

| 19Dh    | —      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       | _                  |

| 19Eh    | _      | Unimplem         | nented                                        |             |             |              |              |              |              | _                                       |                    |

| 19Fh    | —      | Unimplem         | nented                                        |             |             |              |              |              |              | —                                       | —                  |

#### TABLE 3-4: SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

## 3.2.2.4 PIE1 Register

This register contains interrupt enable bits.

| 51ER 3-4: | PIET REGI                             | SIER (AL                                                                                                              | DRESS:        | ocn)                            |                |           |               |        |  |  |  |  |  |

|-----------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------|----------------|-----------|---------------|--------|--|--|--|--|--|

|           | R/W-0                                 | R/W-0                                                                                                                 | R/W-0         | R/W-0                           | U-0            | R/W-0     | R/W-0         | R/W-0  |  |  |  |  |  |

|           | EEIE                                  | CMIE                                                                                                                  | RCIE          | TXIE                            |                | CCP1IE    | TMR2IE        | TMR1IE |  |  |  |  |  |

|           | bit 7                                 |                                                                                                                       |               |                                 |                |           |               | bit 0  |  |  |  |  |  |

|           |                                       |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 7     |                                       | •                                                                                                                     | •             | ot Enable Bit                   |                |           |               |        |  |  |  |  |  |

|           |                                       | <ul> <li>1 = Enables the EE write complete interrupt</li> <li>0 = Disables the EE write complete interrupt</li> </ul> |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 6     | CMIE: Comparator Interrupt Enable bit |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

|           |                                       | <ul><li>1 = Enables the comparator interrupt</li><li>0 = Disables the comparator interrupt</li></ul>                  |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 5     | RCIE: USA                             | RT Receive                                                                                                            | e Interrupt E | Enable bit                      |                |           |               |        |  |  |  |  |  |

|           |                                       | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul>         |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 4     | TXIE: USAF                            | RT Transmi                                                                                                            | t Interrupt E | Enable bit                      |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables<br>0 = Disable            |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 3     | Unimpleme                             | ented: Rea                                                                                                            | d as '0'      |                                 |                |           |               |        |  |  |  |  |  |

| bit 2     | CCP1IE: CO                            | CP1 Interru                                                                                                           | pt Enable b   | oit                             |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables<br>0 = Disable            |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

| bit 1     | TMR2IE: T                             | MR2 to PR2                                                                                                            | 2 Match Inte  | errupt Enable                   | e bit          |           |               |        |  |  |  |  |  |

|           |                                       |                                                                                                                       |               | itch interrupt<br>atch interrup |                |           |               |        |  |  |  |  |  |

| bit 0     | TMR1IE: T                             | MR1 Overfle                                                                                                           | ow Interrup   | t Enable bit                    |                |           |               |        |  |  |  |  |  |

|           | 1 = Enables                           | s the TMR1                                                                                                            | overflow in   | nterrupt                        |                |           |               |        |  |  |  |  |  |

|           | 0 = Disable                           | s the TMR1                                                                                                            | l overflow i  | nterrupt                        |                |           |               |        |  |  |  |  |  |

|           | Legend:                               |                                                                                                                       |               |                                 |                |           |               |        |  |  |  |  |  |

|           | R = Readat                            | ole bit                                                                                                               | VV = V        | Vritable bit                    | U = Unimple    | emented b | it, read as ' | D'     |  |  |  |  |  |

|           | -n = Value a                          | at POR                                                                                                                | '1' = E       | Bit is set                      | '0' = Bit is c | leared    | x = Bit is ur | nknown |  |  |  |  |  |

## REGISTER 3-4: PIE1 REGISTER (ADDRESS: 8Ch)

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000       | xxxu 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

| 1Fh     | CMCON | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 9Fh     | VRCON | VREN   | VROE   | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

TABLE 5-2:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTA<sup>(1)</sup>

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTA.

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

PORTB is multiplexed with the external interrupt, USART, CCP module and the TMR1 clock input/output. The standard port functions and the alternate port functions are shown in Table 5-3. Alternate port functions override TRIS setting when enabled.

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-onchange comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared. This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | when a read operation is being executed       |  |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |  |  |

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

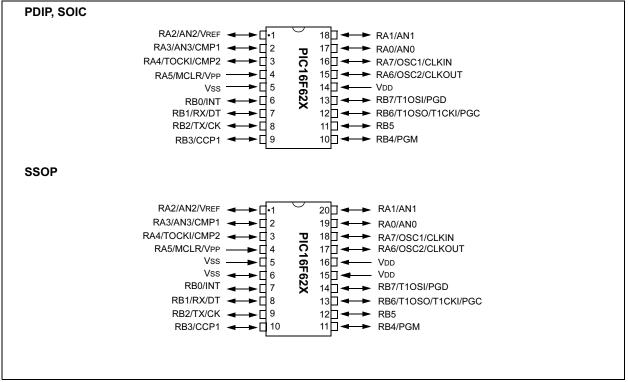

## 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

## 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

NOTES:

## 9.6 Comparator Interrupts

The Comparator Interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the Comparator Interrupt Flag. The CMIF bit must be RESET by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a                                       | change     | in  | the   | CMCON   | register |  |  |  |  |  |

|-------|--------------------------------------------|------------|-----|-------|---------|----------|--|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a       |            |     |       |         |          |  |  |  |  |  |

|       | read operation is being executed (start of |            |     |       |         |          |  |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR1<6>)     |            |     |       |         |          |  |  |  |  |  |

|       | interr                                     | upt flag m | nay | not g | et set. |          |  |  |  |  |  |

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any write or read of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 9.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher SLEEP currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering SLEEP. If the device wakes-up from SLEEP, the contents of the CMCON register are not affected.

## 9.8 Effects of a RESET

A device RESET forces the CMCON register to its RESET state. This forces the Comparator module to be in the comparator RESET mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at RESET time. The comparators will be powered-down during the RESET interval.

## 9.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latchup may occur. A source impedance of maximum 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### EXAMPLE 10-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; 4 Inputs Muxed |

|-------|-------------|------------------|

| MOVWF | CMCON       | ; to 2 comps.    |

| BSF   | STATUS, RPO | ; go to Bank 1   |

| MOVLW | 0x07        | ; RA3-RA0 are    |

| MOVWF | TRISA       | ; outputs        |

| MOVLW | 0xA6        | ; enable VREF    |

| MOVWF | VRCON       | ; low range      |

|       |             | ; set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; go to Bank 0   |

| CALL  | DELAY10     | ; 10µs delay     |

## 10.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 10-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The tested absolute accuracy of the Voltage Reference can be found in Table 17-2.

## 10.3 Operation During SLEEP

When the device wakes-up from SLEEP through an interrupt or a Watchdog Timer timeout, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

## 10.4 Effects of a RESET

A device RESET disables the Voltage Reference by clearing bit VREN (VRCON<7>). This RESET also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### **10.5** Connection Considerations

The Voltage Reference module operates independently of the Comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

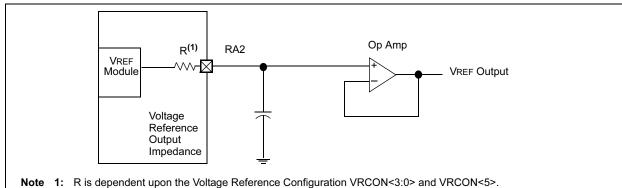

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 10-2 shows an example buffering technique.

### FIGURE 10-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 10-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR | Value On<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 9Fh     | VRCON | VREN   | VROE   | VRR    |        | VR3    | VR2    | VR1    | VR0    | 000- 0000       | 000- 0000                       |

| 1Fh     | CMCON | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| 85h     | TRISA | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

**Note 1:** — = Unimplemented, read as '0'.

| BAUD     | Fosc = 20 MHz |        |                    | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|---------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD         | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA            | _      | _                  | NA     | _      |                    | NA     | _      |                    |

| 1.2      | 1.221         | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404         | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469         | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53         | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13         | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2         | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5         | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA            | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5         | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221         | —      | 255                | 0.977  |        | 255                | 0.6104 |        | 255                |

| TABLE 12-4: | BAUD RATES FOR ASYNCHRONOUS MODE ( | BRGH=0) |

|-------------|------------------------------------|---------|

|-------------|------------------------------------|---------|

| BAUD     | Fosc = 7.15909 MHz |        | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|--------------------|--------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD              | ERROR  | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA                 | _      | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203              | +0.23% | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380              | -0.83% | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322              | -2.90% | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64              | -2.90% | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA                 | _      | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA                 | _      | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 500      | NA                 |        | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9              | _      | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437              | —      | 255                | 0.3094     |        | 255                | 3.906  |        | 255                |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |         | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3         | 0.301        | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2         | 1.190        | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4         | 2.432        | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6         | 9.322        | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2        | 18.64        | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8        | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96          | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH        | 55.93        | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW         | 0.2185       | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

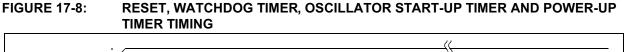

## 14.5 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Detect (BOD)

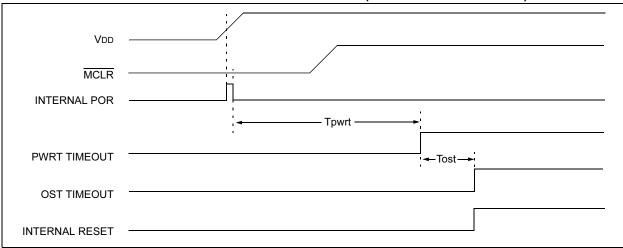

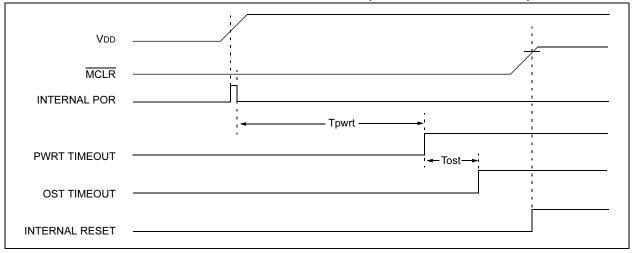

#### 14.5.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in RESET until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce an internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 14.5.2 POWER-UP TIMER (PWRT)

The PWRT provides a fixed 72 ms (nominal) timeout on power-up only, from POR or Brown-out Detect Reset. The PWRT operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the PWRT. The PWRT should always be enabled when Brown-out Detect Reset is enabled. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 14.5.3 OSCILLATOR START-UP TIMER (OST)

The OST provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

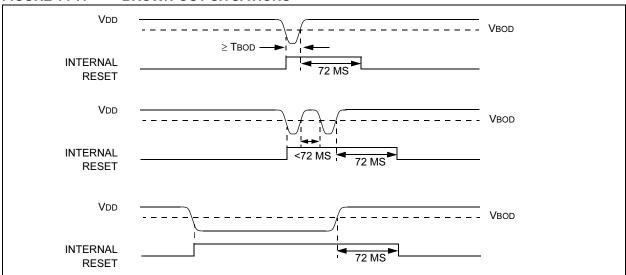

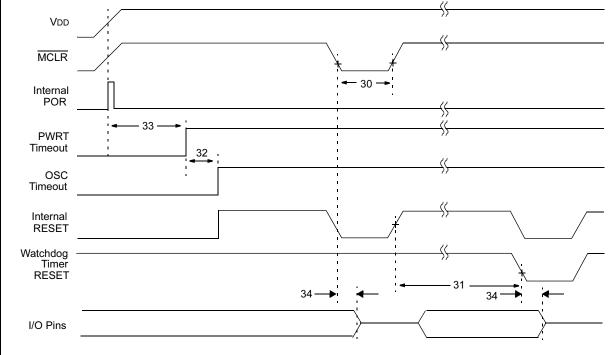

#### 14.5.4 BROWN-OUT DETECT (BOD) RESET

The PIC16F62X members have on-chip BOD circuitry. A configuration bit, BODEN, can disable (if clear/ programmed) or enable (if set) the BOD Reset circuitry. If VDD falls below VBOD for longer than TBOD, the brown-out situation will RESET the chip. A RESET is not guaranteed to occur if VDD falls below VBOD for shorter than TBOD. VBOD and TBOD are defined in Table 17-1 and Table 17-6, respectively.

On any RESET (Power-on, Brown-out, Watchdog, etc.) the chip will remain in RESET until VDD rises above VBOD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms.

If VDD drops below VBOD while the Power-up Timer is running, the chip will go back into a Brown-out Detect Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOD, the Power-Up Timer will execute a 72 ms RESET. The Power-up Timer should always be enabled when Brown-out Detect is enabled. Figure 14-7 shows typical Brown-out situations.

FIGURE 14-7: BROWN-OUT SITUATIONS

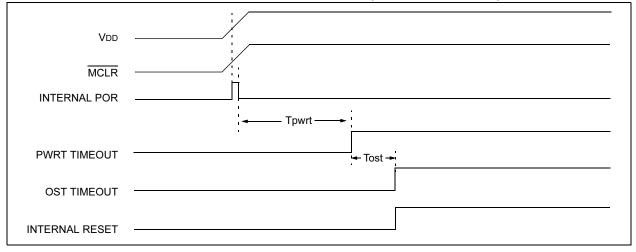

FIGURE 14-9: TIMEOUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 14-10: TIMEOUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

© 2003 Microchip Technology Inc.

| IORLW            | Inclusive OR Literal with W                                                                                              |    |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                 |    |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |    |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                             |    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                        |    |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kk                                                                                                          | ck |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |    |  |  |  |  |  |

| Words:           | 1                                                                                                                        |    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                        |    |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                               |    |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 0                                                 |    |  |  |  |  |  |

| MOVLW                         | Move Literal to W                                                                                |      |      |      |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|--|--|--|--|

| Syntax:                       | [ <i>label</i> ] MOVLW k                                                                         |      |      |      |  |  |  |  |

| Operands:                     | $0 \le k \le 255$                                                                                |      |      |      |  |  |  |  |

| Operation:                    | $k \rightarrow (W)$                                                                              | )    |      |      |  |  |  |  |

| Status Affected:              | None                                                                                             |      |      |      |  |  |  |  |

| Encoding:                     | 11                                                                                               | 00xx | kkkk | kkkk |  |  |  |  |

| Description:                  | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |      |      |      |  |  |  |  |

| Words:                        | 1                                                                                                |      |      |      |  |  |  |  |

| Cycles:                       | 1                                                                                                |      |      |      |  |  |  |  |

| Example                       | MOVLW                                                                                            | 0x5A |      |      |  |  |  |  |

| After Instruction<br>W = 0x5A |                                                                                                  |      |      |      |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                 |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                     |  |  |  |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                     |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is<br>1 the result is placed back in<br>register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                     |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                     |  |  |  |  |  |  |

| Example          | IORWF REG1, 0                                                                                                                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>REG1 = 0x13 $W = 0x91$ After Instruction<br>REG1 = 0x13 $W = 0x93$ $Z = 1$                                                                      |  |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  | moved to a destination depen-<br>dent upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file regis-<br>ter f itself. $d = 1$ is useful to test<br>a file register since status flag Z<br>is affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Example          | MOVF REG1, 0                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | After Instruction<br>W= value in REG1 register<br>Z = 1                                                                                                                                                                                           |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                               | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                           | Operation:       | $d \in [0,1]$<br>See description below                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                   | Status Affected: | С                                                                                                                                                                                                              |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                              |

| Description:     | The W register is loaded with<br>the eight bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0 the result<br>is placed in the W register. If 'd' is<br>1 the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      | Words:           | 1                                                                                                                                                                                                              |

| Example          | CALL TABLE;W contains table                                                                                                                                                            |                  | 1                                                                                                                                                                                                              |

|                  | <ul> <li>;offset value</li> <li>;W now has table</li> </ul>                                                                                                                            | Cycles:          |                                                                                                                                                                                                                |

|                  | value                                                                                                                                                                                  | Example          | RLF REG1, 0<br>Before Instruction                                                                                                                                                                              |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8             |                  | REG1 = 1110 0110 $C = 0$ After Instruction $REG1 = 1110 0110$ $W = 1100 1100$ $C = 1$                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

| Syntax:          | [label] RETURN                                                                                                                                                                         |                  |                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction.                             |                  |                                                                                                                                                                                                                |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Example          | RETURN                                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

|                  | After Interrupt<br>PC = TOS                                                                                                                                                            |                  |                                                                                                                                                                                                                |

## 17.1 DC Characteristics: PIC16F62X-04 (Commercial, Industrial, Extended) PIC16F62X-20 (Commercial, Industrial, Extended) PIC16LF62X-04 (Commercial, Industrial)

| PIC16LF62X-04<br>(Commercial, Industrial)                          |                                    |                                                                                                                                                                  | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq Ta \leq +85^\circ C \mbox{ for industrial and} \\ 0^\circ C \leq Ta \leq +70^\circ C \mbox{ for commercial} \end{array} $ |                                                                                                                                                                                                                                                     |                           |                      |                                                                                    |  |  |

|--------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|------------------------------------------------------------------------------------|--|--|

| PIC16F62X-04<br>PIC16F62X-20<br>(Commercial, Industrial, Extended) |                                    |                                                                                                                                                                  |                                                                                                                                                                                                                                                                 | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial and $0^{\circ}C \le Ta \le +70^{\circ}C$ for commercial and $-40^{\circ}C \le Ta \le +125^{\circ}C$ for extended |                           |                      |                                                                                    |  |  |

| Param<br>No.                                                       | Sym                                | Characteristic/Device                                                                                                                                            | Min                                                                                                                                                                                                                                                             | Тур†                                                                                                                                                                                                                                                | Мах                       | Units                | Conditions                                                                         |  |  |

|                                                                    | IPD                                | Power Down Current* <sup>(2), (3)</sup>                                                                                                                          |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |                           |                      |                                                                                    |  |  |

| D020                                                               |                                    | PIC16LF62X                                                                                                                                                       |                                                                                                                                                                                                                                                                 | 0.20<br>0.20                                                                                                                                                                                                                                        | 2.0<br>2.2                | μΑ<br>μΑ             | VDD = 2.0<br>VDD = 5.5                                                             |  |  |

| D020                                                               |                                    | PIC16F62X                                                                                                                                                        | <br>                                                                                                                                                                                                                                                            | 0.20<br>0.20<br>0.20<br>2.70                                                                                                                                                                                                                        | 2.2<br>5.0<br>9.0<br>15.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0<br>VDD = 4.5*<br>VDD = 5.5<br>VDD = 5.5 Extended                         |  |  |

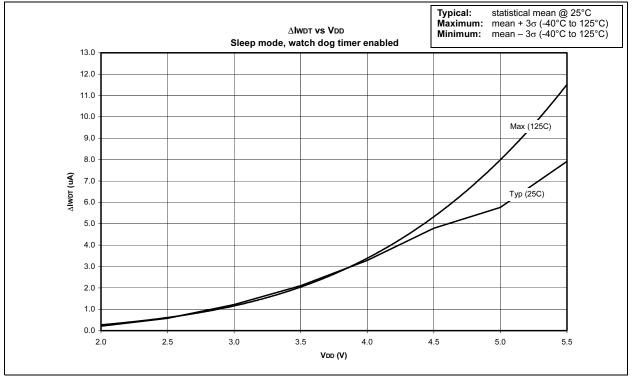

| D023                                                               | ΔIWDT<br>ΔIBOD<br>ΔICOMP<br>ΔIVREF | WDT Current <sup>(4)</sup><br>Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup><br>VREF Current <sup>(4)</sup> | <br>                                                                                                                                                                                                                                                            | 6.0<br>75<br>30                                                                                                                                                                                                                                     | 15<br>125<br>50<br>135    | μΑ<br>μΑ<br>μΑ       | $\frac{V_{DD}}{BOD} = 3.0V$<br>BOD enabled, VDD = 5.0V<br>VDD = 3.0V<br>VDD = 3.0V |  |  |

| Daga                                                               | ∆Iwdt                              | WDT Current <sup>(4)</sup>                                                                                                                                       | _                                                                                                                                                                                                                                                               | 6.0                                                                                                                                                                                                                                                 | 20<br>25                  | μΑ<br>μΑ             | VDD = 4.0V, Commercial,<br>Industrial<br>VDD = 4.0V, Extended                      |  |  |

| D023                                                               |                                    | Brown-out Detect Current <sup>(4)</sup><br>Comparator Current for each<br>Comparator <sup>(4)</sup>                                                              | _                                                                                                                                                                                                                                                               | 75<br>30                                                                                                                                                                                                                                            | 125<br>50                 | μΑ<br>μΑ             | BOD enabled, VDD = 5.0V<br>VDD = 4.0V                                              |  |  |

|                                                                    | $\Delta$ IVREF                     | VREF Current <sup>(4)</sup>                                                                                                                                      | —                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     | 135                       | μA                   | VDD = 4.0V                                                                         |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.