Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

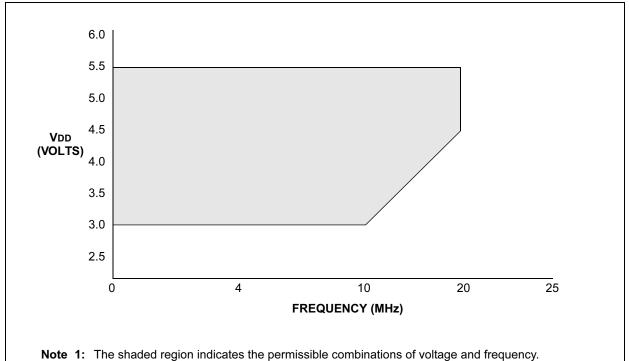

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7      | Bit 6                                                              | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1      | Bit 0   | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|--------------------------------------------------------------------|-----------------|----------------|---------------|----------------|------------|---------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                                                                    |                 |                |               |                |            |         |                                         |                    |

| 00h     | INDF    | Addressir  | ng this locatio                                                    | l register)     | xxxx xxxx      | 25            |                |            |         |                                         |                    |

| 01h     | TMR0    | Timer0 M   | odule's Regis                                                      | ter             |                |               |                |            | • /     | xxxx xxxx                               | 43                 |

| 02h     | PCL     | Program    | Counter's (PC                                                      | ) Least Sign    | ificant Byte   |               |                |            |         | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP        | RP1                                                                | RP0             | TO             | PD            | Z              | DC         | С       | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d | ata memory a                                                       | ddress point    | er             |               |                |            | -       | xxxx xxxx                               | 25                 |

| 05h     | PORTA   | RA7        | RA6                                                                | RA5             | RA4            | RA3           | RA2            | RA1        | RA0     | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7        | RB6                                                                | RB5             | RB4            | RB3           | RB2            | RB1        | RB0     | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | _                                       |                    |

| 08h     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | _                                       |                    |

| 09h     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | _                                       |                    |

| 0Ah     | PCLATH  | _          | _                                                                  | _               | Write buffer   | for upper 5 b | oits of progra | im counter |         | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE        | PEIE                                                               | T0IE            | INTE           | RBIE          | T0IF           | INTF       | RBIF    | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF       | CMIF                                                               | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF     | TMR1IF  | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen   | Unimplemented                                                      |                 |                |               |                |            |         |                                         | _                  |

| 0Eh     | TMR1L   | Holding r  | Holding register for the Least Significant Byte of the 16-bit TMR1 |                 |                |               |                |            |         |                                         | 46                 |

| 0Fh     | TMR1H   | Holding r  | egister for the                                                    | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |            |         | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _          | _                                                                  | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS     | TMR10N  | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo    | odule's registe                                                    | r               |                |               |                |            |         | 0000 0000                               | 50                 |

| 12h     | T2CON   | _          | TOUTPS3                                                            | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1    | T2CKPS0 | -000 0000                               | 50                 |

| 13h     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | —                                       | _                  |

| 14h     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0  | Compare/PWN                                                        | /I register (LS | SB)            |               |                |            |         | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0  | Compare/PWN                                                        | /I register (M  | SB)            |               |                |            |         | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _          | —                                                                  | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1     | CCP1M0  | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN       | RX9                                                                | SREN            | CREN           | ADEN          | FERR           | OERR       | RX9D    | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T    | ransmit data                                                       | register        |                |               |                |            |         | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART F    | Receive data r                                                     | egister         |                |               |                |            |         | 0000 0000                               | 77                 |

| 1Bh     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | —                                       | _                  |

| 1Ch     | _       | Unimplen   | nented                                                             |                 |                |               |                |            |         | —                                       | _                  |

| 1Dh     | —       | Unimplen   | nented                                                             |                 |                |               |                |            |         | _                                       | —                  |

| 1Eh     | —       | Unimplen   | nented                                                             |                 | 1              | 1             |                |            | 1       | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT      | C10UT                                                              | C2INV           | C1INV          | CIS           | CM2            | CM1        | CM0     | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

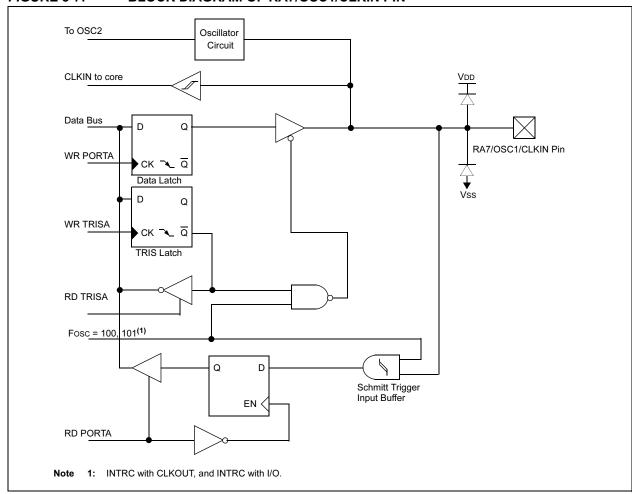

## FIGURE 5-7: BLOCK DIAGRAM OF RA7/OSC1/CLKIN PIN

## 11.3 PWM Mode

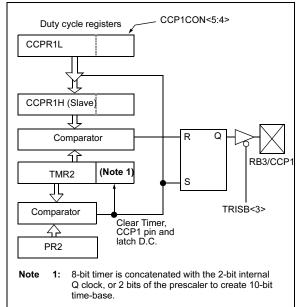

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<3> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTB I/O data |

|       | latch.                                    |

Figure 11-2 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 11.3.3.

#### FIGURE 11-2: SIMPLIFIED PWM BLOCK DIAGRAM

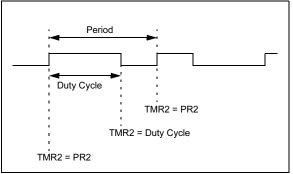

A PWM output (Figure 11-3) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 11-3: PWM OUTPUT

### 11.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • Tosc • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

**Note:** The Timer2 postscaler (see Section 8.0) is not used in the determination of the PWM frequency. The postscaler could be used to have an interrupt occur at a different frequency than the PWM output.

| TER 12-2: | RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                                                                                      |                                                                                                |                |                     |               |               |       |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|---------------------|---------------|---------------|-------|--|--|--|--|

|           | R/W-0 R/W-0                                                                                                                                                                    | R/W-0                                                                                          | R/W-0          | R/W-0               | R-0           | R-0           | R-x   |  |  |  |  |

|           | SPEN RX9                                                                                                                                                                       | SREN                                                                                           | CREN           | ADEN                | FERR          | OERR          | RX9D  |  |  |  |  |

|           | bit 7                                                                                                                                                                          |                                                                                                |                | ·                   |               |               | bit 0 |  |  |  |  |

| bit 7     | <b>SPEN</b> : Serial Port Ena<br>(Configures RB1/RX/D<br>1 = Serial port enabled<br>0 = Serial port disabled                                                                   | T and RB2/TX/                                                                                  | CK pins as se  | erial port pins whe | en bits TRISE | 3<2:17> are   | set)  |  |  |  |  |

| bit 6     | <ul> <li>RX9: 9-bit Receive Enable bit</li> <li>1 = Selects 9-bit reception</li> <li>0 = Selects 8-bit reception</li> </ul>                                                    |                                                                                                |                |                     |               |               |       |  |  |  |  |

| bit 5     | SREN: Single Receive<br>Asynchronous mode:<br>Don't care<br>Synchronous mode - r<br>1 = Enables single<br>0 = Disables single<br>This bit is cleared a<br>Synchronous mode - s | n <u>aster</u> :<br>receive<br>receive<br>fter reception is                                    | complete.      |                     |               |               |       |  |  |  |  |

|           | Unused in this mod                                                                                                                                                             |                                                                                                |                |                     |               |               |       |  |  |  |  |

| bit 4     | CREN: Continuous Re<br><u>Asynchronous mode</u> :<br>1 = Enables continu<br>0 = Disables continu<br><u>Synchronous mode</u> :<br>1 = Enables continu<br>0 = Disables continu   | uous receive<br>uous receive<br>uous receive un                                                |                | CREN is cleared (   | CREN overr    | ides SREN)    |       |  |  |  |  |

| bit 3     | ADEN: Address Detect<br>Asynchronous mode 9<br>1 = Enables address<br>0 = Disables address<br>Asynchronous mode 8<br>Unused in this mode<br>Unused in this mode                | <u>-bit (RX9 = 1)</u> :<br>s detection, ena<br>ss detection, all<br><u>-bit (RX9=0)</u> :<br>e |                |                     |               |               |       |  |  |  |  |

| bit 2     | FERR: Framing Error I<br>1 = Framing error (Car<br>0 = No framing error                                                                                                        | oit                                                                                            | reading RCF    | REG register and    | receive next  | valid byte)   |       |  |  |  |  |

| bit 1     | OERR: Overrun Error<br>1 = Overrun error (Car<br>0 = No overrun error                                                                                                          |                                                                                                | clearing bit C | REN)                |               |               |       |  |  |  |  |

| bit 0     | RX9D: 9th bit of receiv                                                                                                                                                        | ed data (Can b                                                                                 | e PARITY bit)  |                     |               |               |       |  |  |  |  |

|           | Legend:<br>R = Readable bit                                                                                                                                                    | W = V                                                                                          | Vritable bit   | U = Unimpl          | emented b     | it, read as ' | 0'    |  |  |  |  |

| REGISTER 12-2: | RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h) |

|----------------|-----------------------------------------------------------|

|                |                                                           |

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 12.2.2 ADEN USART ASYNCHRONOUS RECEIVER

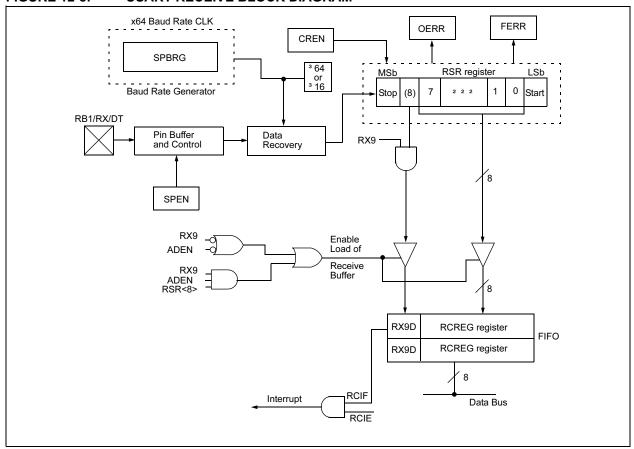

The receiver block diagram is shown in Figure 12-8. The data is received on the RB1/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register ( i.e., it is a two-deep FIFO).

It is possible for two bytes of data to be received and transferred to the RCREG FIFO, and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

## 12.3 USART Function

The USART function is similar to that on the PIC16C74B, which includes the BRGH = 1 fix.

#### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed so when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer. The ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if, and only, if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (='1'), all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = '1'). When ADEN is disabled (='0'), all data bytes are received and the 9th bit can be used as the PARITY bit.

The USART Receive Block Diagram is shown in Figure 12-8.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Steps to follow when setting up an Asynchronous or Synchronous Reception with Address Detect Enabled:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable asynchronous or synchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. Set bit RX9 to enable 9-bit reception.

- 5. Set ADEN to enable address detect.

- 6. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 9. If any error occurred, clear the error by clearing enable bit CREN if it was already set.

- If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name                               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Valu<br>PC |      |      | e on<br>other<br>ETS |

|---------|------------------------------------|-------|-------|-------|-------|-------|--------|--------|--------|------------|------|------|----------------------|

| 0Ch     | PIR1                               | EEIF  | CMIF  | RCIF  | TXIF  | —     | CCP1IF | TMR2IF | TMR1IF | 0000       | -000 | 0000 | -000                 |

| 18h     | RCSTA                              | SPEN  | RX9   | SREN  | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000       | -00x | 0000 | -00x                 |

| 1Ah     | RCREG                              | RX7   | RX6   | RX5   | RX4   | RX3   | RX2    | RX1    | RX0    | 0000       | 0000 | 0000 | 0000                 |

| 8Ch     | PIE1                               | EEIE  | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000       | -000 | 0000 | -000                 |

| 98h     | TXSTA                              | CSRC  | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000       | -010 | 0000 | -010                 |

| 99h     | SPBRG Baud Rate Generator Register |       |       |       |       |       |        | 0000   | 0000   | 0000       | 0000 |      |                      |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

| Address | Name  | Bit 7                        | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|-------|------------------------------|-----------|----------|-------|-------|--------|--------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1  | EEIF                         | CMIF      | RCIF     | TXIF  |       | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA | SPEN                         | RX9       | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG | USART T                      | ransmit I | Register |       |       |        |        |           | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1  | EEIE                         | CMIE      | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA | CSRC                         | TX9       | TXEN     | SYNC  |       | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG | Baud Rate Generator Register |           |          |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

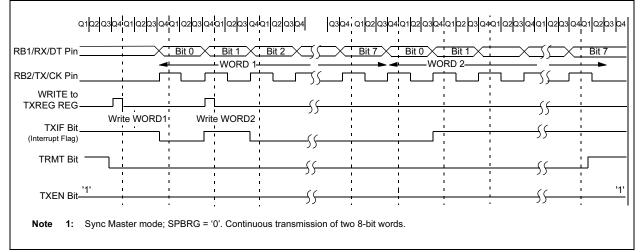

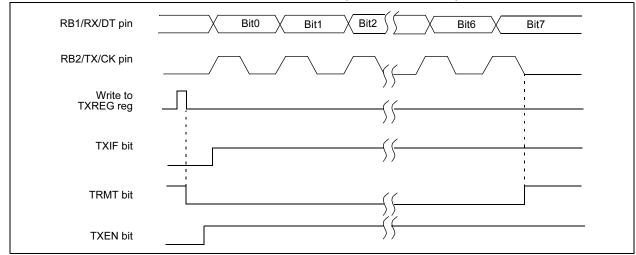

### FIGURE 12-13: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in Slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

1. Enable the synchronous master serial port by

setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

| Address | Name                               | Bit 7    | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|------------------------------------|----------|-----------|----------|-------|-------|--------|-----------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF     | CMIF      | RCIF     | TXIF  |       | CCP1IF | TMR2IF    | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN     | RX9       | SREN     | CREN  | ADEN  | FERR   | OERR      | RX9D      | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG                              | USART TI | ransmit I | Register |       |       |        |           |           | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE     | CMIE      | RCIE     | TXIE  | _     | CCP1IE | TMR2IE    | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC     | TX9       | TXEN     | SYNC  |       | BRGH   | TRMT      | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |          |           |          |       |       |        | 0000 0000 | 0000 0000 |                 |                                 |

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

#### TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                          | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|-------|--------------------------------|----------|----------|-------|-------|--------|--------|-----------|-----------------|---------------------------------|

| 0Ch     | PIR1  | EEIF                           | CMIF     | RCIF     | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF    | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA | SPEN                           | RX9      | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D      | 0000 -00x       | 0000 -00x                       |

| 1Ah     | RCREG | USART R                        | eceive F | Register |       |       |        |        |           | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1  | EEIE                           | CMIE     | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE    | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA | CSRC                           | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG | G Baud Rate Generator Register |          |          |       |       |        |        | 0000 0000 | 0000 0000       |                                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

#### 14.9.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on  $\overline{MCLR}$  pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up is cleared when SLEEP is invoked. TO bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the

corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes-up from SLEEP, regardless of the source of wake-up.

#### FIGURE 14-17: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                                                                         |                              | Q1  Q2  Q3  Q4;    | Q1  Q2  Q3  Q4; (   | Q1  Q2  Q3  Q4;     |

|-----------------------------------------------------------------------------------------|------------------------------|--------------------|---------------------|---------------------|

|                                                                                         |                              |                    |                     |                     |

|                                                                                         | <u>it</u> / /                |                    |                     | / i                 |

| INT pin                                                                                 | · · ·                        | I                  |                     | I                   |

|                                                                                         | Interrupt Latenc             | :V                 |                     |                     |

|                                                                                         | (Note 2)                     | <u>,</u>           | <b>→</b>            |                     |

| GIE bit<br>(INTCON<7>) Processor in                                                     | I I                          | <u>'</u>           | <u> </u>            | !                   |

| SLEEP                                                                                   |                              |                    | i                   |                     |

| INSTRUCTION FLOW                                                                        |                              | 1                  | 1                   | 1                   |

| PC X PC X PC+1 X PC+2                                                                   | X PC+2                       | PC + 2             | <u>(0004h X</u>     | 0005h               |

| Instruction { Inst(PC) = SLEEP Inst(PC + 1)                                             | Inst(PC + 2)                 | 1<br>1<br>1        | Inst(0004h)         | Inst(0005h)         |

| Instruction { Inst(PC - 1) SLEEP                                                        | Inst(PC + 1)                 | Dummy cycle        | Dummy cycle         | Inst(0004h)         |

| Note 1: XT, HS or LP Oscillator mode assumed.                                           |                              |                    |                     |                     |

| 2: TOST = 1024TOSC (drawing not to scale). Approximation                                | tely 1 $\mu$ s delay will be | there for ER Os    | c mode.             |                     |

| <ol> <li>GIE = '1' assumed. In this case after wake- up, the pr<br/>in-line.</li> </ol> | rocessor jumps to the        | interrupt routine. | If GIE = '0', execu | ution will continue |

| 4: CLKOUT is not available in these Osc modes, but sl                                   | hown here for timing r       | eference.          |                     |                     |

### 14.10 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and FLASH program memory will be erased when the code protection is turned off. The INTRC calibration data is not erased.

## 14.11 User ID Locations

Four memory locations (2000h-2003h) are designated as user ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the Least Significant 4 bits of the user ID locations are used.

|                  | •                                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |

| ANDLW                                                                                                    | AND Literal with W                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> ] ANDLW k                                                                                                                                                                                                                                                                                                                                                                                |

| Operands:                                                                                                | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                                                                     |

| Operation:                                                                                               | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                                                                         |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                       |

| Description:                                                                                             | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                                                                  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example                                                                                                  | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                          | W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                          | W = 0x03                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                         |

| ANDWF                                                                                                    | AND W with f                                                                                                                                                                                                                                                                                                                                                                                            |

| ANDWF<br>Syntax:                                                                                         | AND W with f [ label ] ANDWF f,d                                                                                                                                                                                                                                                                                                                                                                        |

| Syntax:                                                                                                  | [ <i>label</i> ] ANDWF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                                                                                                                               |

| Syntax:<br>Operands:                                                                                     | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                                                                                                                   |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} ANDWF  f,d$ $0 \le f \le 127$ $d \in [0,1]$ $(W) .AND. (f) \rightarrow (dest)$ $Z$ $00 \qquad 0101  dfff \qquad ffff$                                                                                                                                                                                                                                              |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 \qquad 0101  dfff \qquad ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register \\ \hline \end{tabular}$                                                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .AND. (f) $\rightarrow$ (dest) Z $00 \qquad 0101  dfff  ffff$ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. \\ 1 \\ \end{bmatrix}$                                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} ANDWF  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                        |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF & REG1, 1 \\ Before Instruction \\ W &= 0x17 \\ \end{bmatrix}$ |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ \hline AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 1 1 ANDWF REG1, 1 Before Instruction W = 0x17 REG1 = 0xC2$          |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |  |  |  |  |

| Operation:       | $(W) + (f) \rightarrow (dest)$                                                                                                                                                 |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |

| Description:     | Add the contents of the W regis-<br>ter with register 'f'. If 'd' is 0 the<br>result is stored in the W register.<br>If 'd' is 1 the result is stored back<br>in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                              |  |  |  |  |

| Example          | ADDWF REG1, 0                                                                                                                                                                  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>REG1 = 0xC2<br>After Instruction<br>W = 0xD9<br>REG1 = 0xC2<br>Z = 0<br>C = 0<br>DC = 0                                                      |  |  |  |  |

| BCF              | Bit Clear f                                                         | BTFSC            | Bit Test f, Skip if Clear                                                            |

|------------------|---------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             | Syntax:          | [ <i>label</i> ]BTFSC f,b                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                  |

| Operation:       | $0 \rightarrow (f \le b >)$                                         | Operation:       | skip if (f <b>) = 0</b>                                                              |

| Status Affected: | None                                                                | Status Affected: | None                                                                                 |

| Encoding:        | 01 00bb bfff ffff                                                   | Encoding:        | 01 10bb bfff ffff                                                                    |

| Description:     | Bit 'b' in register 'f' is cleared.                                 | Description:     | If bit 'b' in register 'f' is '0' then the                                           |

| Words:           | 1                                                                   |                  | next instruction is skipped.<br>If bit 'b' is '0' then the next                      |

| Cycles:          | 1                                                                   |                  | instruction fetched during the                                                       |

| Example          | BCF REG1, 7                                                         |                  | current instruction execution is                                                     |

|                  | Before Instruction<br>REG1 = 0xC7<br>After Instruction              |                  | discarded, and a NOP is executed<br>instead, making this a two-cycle<br>instruction. |

|                  | REG1 = 0x47                                                         | Words:           | 1                                                                                    |

|                  |                                                                     | Cycles:          | 1 <sup>(2)</sup>                                                                     |

| BSF              | Bit Set f                                                           | Example          | HERE BTFSC REG1<br>FALSE GOTO PROCESS_CODE                                           |

| Syntax:          | [ label ] BSF f,b                                                   |                  | TRUE •                                                                               |

| Operands:        | $0 \le f \le 127$                                                   |                  | •                                                                                    |

|                  | $0 \le b \le 7$                                                     |                  | Before Instruction                                                                   |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |                  | PC = address HERE                                                                    |

| Status Affected: | None                                                                |                  | After Instruction<br>if REG<1> = 0,                                                  |

| Encoding:        | 01 01bb bfff ffff                                                   |                  | PC = address TRUE                                                                    |

| Description:     | Bit 'b' in register 'f' is set.                                     |                  | if REG<1>=1,                                                                         |

| Words:           | 1                                                                   |                  | PC = address FALSE                                                                   |

| Cycles:          | 1                                                                   |                  |                                                                                      |

Example

BSF

REG1, 7

REG1 = 0x0A

REG1 = 0x8A

Before Instruction

After Instruction

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                      | CALL             | Call Subroutine                                                                                                                                                                                                                |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ]BTFSS f,b                                                                                                                                                                                                                                                    | Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                        |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                                                                          | Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                             |  |  |

|                  | 0 ≤ b < 7                                                                                                                                                                                                                                                                    | Operation:       | (PC)+ 1 $\rightarrow$ TOS,                                                                                                                                                                                                     |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                      |                  | $k \rightarrow PC<10:0>$ ,<br>(PCLATH<4:3>) $\rightarrow PC<12:11>$                                                                                                                                                            |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                         | Status Affected: | $(\text{FCLATH} < 4.3^{\circ}) \rightarrow \text{FC} < 12.11^{\circ}$ None                                                                                                                                                     |  |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                                                            | Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                              |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next<br>instruction fetched during the<br>current instruction execution, is<br>discarded and a NOP is executed<br>instead, making this a two-cycle<br>instruction. | Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven bit<br>immediate address is loaded<br>into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                            |                  | instruction.                                                                                                                                                                                                                   |  |  |

| Cycles:          | 1 <sup>(2)</sup>                                                                                                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                              |  |  |

| Example          | HERE BTFSS REG1                                                                                                                                                                                                                                                              | Cycles:          | 2                                                                                                                                                                                                                              |  |  |

|                  | FALSE GOTO PROCESS_CODE<br>TRUE •                                                                                                                                                                                                                                            | Example          | HERE CALL THERE                                                                                                                                                                                                                |  |  |

|                  | •                                                                                                                                                                                                                                                                            |                  | Before Instruction<br>PC = Address HERE                                                                                                                                                                                        |  |  |

|                  | •<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,                                                                                                                                                                                         |                  | After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                                                |  |  |

|                  | PC = address FALSE<br>if FLAG<1> = 1,                                                                                                                                                                                                                                        |                  | Clear f                                                                                                                                                                                                                        |  |  |

|                  | PC = address TRUE                                                                                                                                                                                                                                                            | Syntax:          | [label] CLRF f                                                                                                                                                                                                                 |  |  |

|                  |                                                                                                                                                                                                                                                                              | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                            |  |  |

|                  |                                                                                                                                                                                                                                                                              | Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                                                                                                          |  |  |