Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |  |  |  |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |  |  |  |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |  |  |  |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |  |  |  |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |  |  |  |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |  |  |  |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |  |  |  |

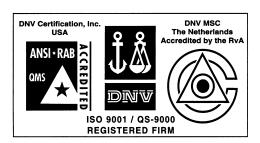

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |  |  |  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |  |  |  |

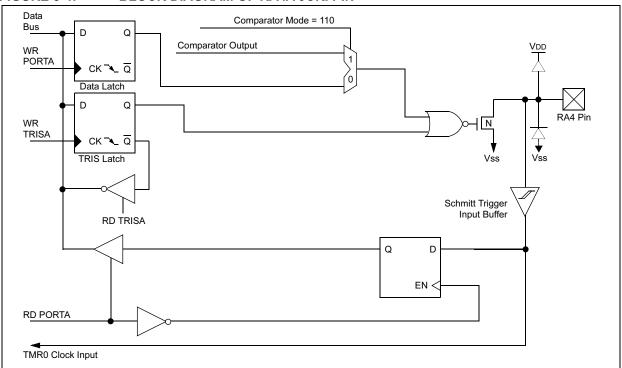

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |  |  |  |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |  |  |  |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |  |  |  |

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |  |  |  |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |  |  |  |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |  |  |  |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |  |  |  |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |  |  |  |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |  |  |  |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |  |  |  |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |  |  |  |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |  |  |  |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |  |  |  |

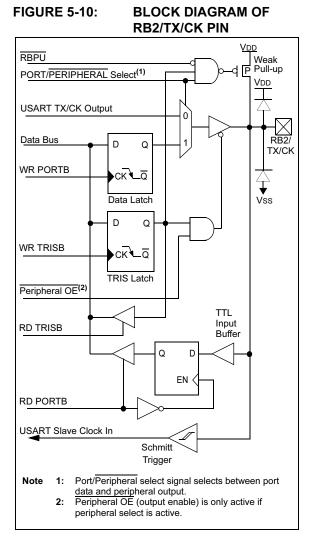

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |  |  |  |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |  |  |  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |  |  |  |

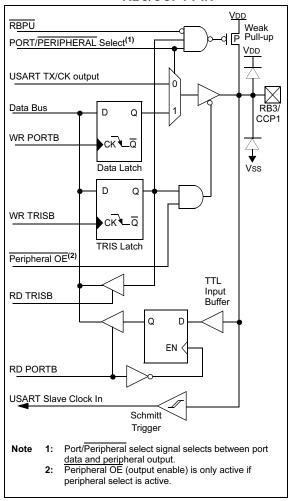

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |  |  |  |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |  |  |  |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |  |  |  |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

### 3.2.2.1 STATUS Register

The STATUS register, shown in Register 3-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory (SRAM).

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect any STATUS bit. For other instructions, not affecting any STATUS bits, see the "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

|         | R/W-0                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                         | R/W-0        | R-1                        | R-1                                             | R/W-x | R/W-x                          | R/W-x        |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------|----------------------------|-------------------------------------------------|-------|--------------------------------|--------------|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                                                                               | RP1                                                                                                           | RP0          | TO                         | PD                                              | Z     | DC                             | С            |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                             |                                                                                                               |              |                            |                                                 |       |                                | bit 0        |  |  |  |  |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                          |                                                                                                               |              |                            |                                                 |       |                                |              |  |  |  |  |

| bit 6-5 | <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)<br>00 = Bank 0 (00h - 7Fh)<br>01 = Bank 1 (80h - FFh)<br>10 = Bank 2 (100h - 17Fh)<br>11 = Bank 3 (180h - 1FFh)                                                                                                                           |                                                                                                               |              |                            |                                                 |       |                                |              |  |  |  |  |

| bit 4   | 1 = After p                                                                                                                                                                                                                                                                                                       | TO: Timeout bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT timeout occurred |              |                            |                                                 |       |                                |              |  |  |  |  |

| bit 3   |                                                                                                                                                                                                                                                                                                                   | -down bit<br>ower-up or t<br>cution of the                                                                    | •            |                            | on                                              |       |                                |              |  |  |  |  |

| bit 2   |                                                                                                                                                                                                                                                                                                                   | sult of an ari<br>sult of an ari                                                                              |              | • •                        | on is zero<br>on is not zero                    |       |                                |              |  |  |  |  |

| bit 1   | is reversed<br>1 = A carry                                                                                                                                                                                                                                                                                        | l)<br>/-out from th                                                                                           | e 4th low or | rder bit of th             | BLW, SUBWF ins<br>e result occurre<br>he result |       | for borrow t                   | the polarity |  |  |  |  |

| bit 0   | <ul> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                                                                                                               |              |                            |                                                 |       |                                |              |  |  |  |  |

|         | <b>Note 1:</b> For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.                                                          |                                                                                                               |              |                            |                                                 |       |                                |              |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                           |                                                                                                               |              |                            |                                                 |       |                                |              |  |  |  |  |

|         | R = Reada<br>-n = Value                                                                                                                                                                                                                                                                                           |                                                                                                               |              | Vritable bit<br>Bit is set | U = Unimple<br>'0' = Bit is c                   |       | it, read as '<br>x = Bit is ui |              |  |  |  |  |

NOTES:

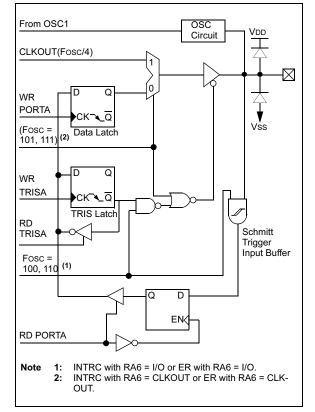

# BLOCK DIAGRAM OF THE RA5/MCLR/VPP PIN

FIGURE 5-6:

BLOCK DIAGRAM OF RA6/OSC2/CLKOUT PIN

#### FIGURE 5-11: BLOCK DIAGRAM OF RB3/CCP1 PIN

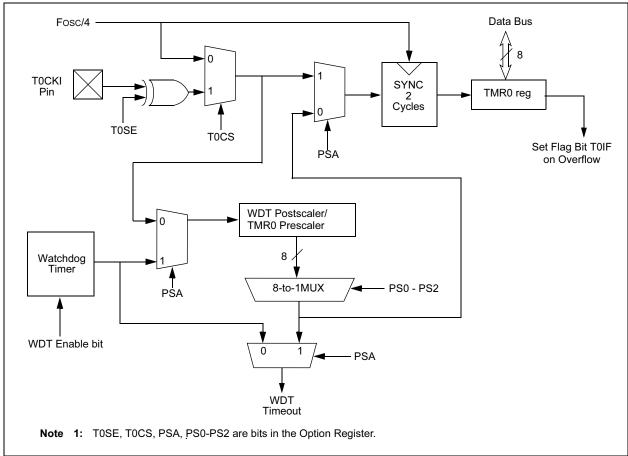

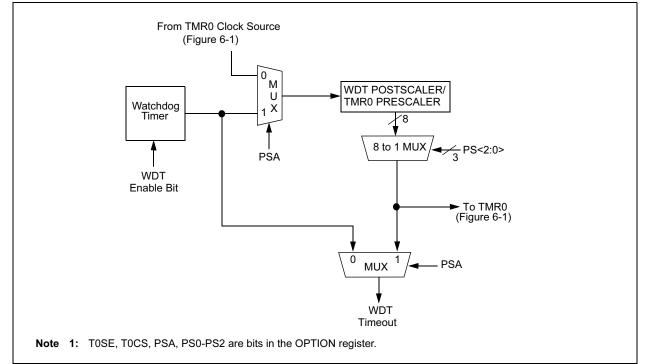

# 6.3 Timer0 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. A prescaler assignment for the Timer0 module means that there is no postscaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). Use the instruction sequences, shown in Example 6-1, when changing the prescaler assignment from Timer0 to WDT, to avoid an unintended device RESET.

### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF    | STATUS, RPO | ;Skip if already in<br>;Bank 0 |

|--------|-------------|--------------------------------|

| CLRWDT |             | ;Clear WDT                     |

|        |             | •                              |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler        |

| BSF    | STATUS, RPO | ;Bank 1                        |

| MOVLW  | '00101111'b | ;These 3 lines                 |

|        |             | ;(5, 6, 7)                     |

| MOVWF  | OPTION_REG  | ;are required only             |

|        |             | ;if desired PS<2:0>            |

|        |             | ;are                           |

| CLRWDT |             | ;000 or 001                    |

| MOVLW  | '00101xxx'b | ;Set Postscaler to             |

| MOVWF  | OPTION_REG  | ;desired WDT rate              |

| BCF    | STATUS, RPO | ;Return to Bank 0              |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                           | ;Clear WDT and<br>;prescaler                              |

|--------------|---------------------------|-----------------------------------------------------------|

| BSF          | STATUS, RPO               |                                                           |

| MOVLW        | b'xxxx0xxx'               | ;Select TMR0, new<br>;prescale value and<br>;clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS, RP0 |                                                           |

| Address               | Name                  | Bit 7    | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------------------|-----------------------|----------|-------------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h                   | TMR0                  | Timer0 m | odule regis | ster   |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE      | PEIE        | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 81h, 181h             | OPTION <sup>(2)</sup> | RBPU     | INTEDG      | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h                   | TRISA                 | TRISA7   | TRISA6      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111       | 1111 1111                       |

Legend: — = Unimplemented locations, read as '0', u = unchanged, x = unknown

**REGISTERS ASSOCIATED WITH TIMER0**

**Note 1:** Shaded bits are not used by TMR0 module.

**TABLE 6-1**:

2: Option is referred by OPTION REG in MPLAB.

| <b>REGISTER 8-1:</b> | T2CO       | N: TIMER C    |              | REGISTER     | (ADDRESS:   | 12h)   |         |         |

|----------------------|------------|---------------|--------------|--------------|-------------|--------|---------|---------|

|                      | U-0        | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |

|                      | _          | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |

|                      | bit 7      |               |              |              |             |        |         | bit 0   |

|                      |            |               |              |              |             |        |         |         |

| bit 7                | Unimplem   | ented: Read   | as '0'       |              |             |        |         |         |

| bit 6-3              | TOUTPS3:   | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |

|                      | 0000 = 1:1 | Postscale V   | alue         |              |             |        |         |         |

|                      | 0001 = 1:2 | Postscale V   | alue         |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | •          |               |              |              |             |        |         |         |

|                      | 1111 = 1:1 | 6 Postscale   |              |              |             |        |         |         |

|                      |            |               |              |              |             |        |         |         |

| bit 2                | TMR2ON:    | Timer2 On bi  | it           |              |             |        |         |         |

|                      | 1 = Timer2 | is on         |              |              |             |        |         |         |

|                      | 0 = Timer2 | is off        |              |              |             |        |         |         |

| bit 1-0              | T2CKPS1:   | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |

|                      | 00 = 1:1 P | rescaler Valu | е            |              |             |        |         |         |

|                      |            | rescaler Valu | -            |              |             |        |         |         |

|                      | 1x = 1:16  | Prescaler Val | ue           |              |             |        |         |         |

|                      | <b></b>    |               |              |              |             |        |         | 1       |

|                      | Legend:    |               |              |              |             |        |         |         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

# TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|-------------|----------------|---------|---------|---------|--------|---------|---------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE         | PEIE           | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF        | CMIF           | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF  | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE        | CMIE           | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod  | lule's registe | r       |         |         |        |         |         | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _           | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri | od Register    |         |         |         |        |         |         | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

The code example in Example 9-1 depicts the steps required to configure the Comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

### EXAMPLE 9-1: INITIALIZING COMPARATOR MODULE

| FLAG REG | FOI         | 0X20                              |

|----------|-------------|-----------------------------------|

| CLRF     | FLAG REG    | 01120                             |

| CLRF     | PORTA       | ;Init PORTA                       |

| MOVE     | CMCON, W    | ;Load comparator bits             |

|          | ,           | -                                 |

| ANDLW    | 0xC0        | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F  | ;Store bits in flag register      |

| MOVLW    | 0x03        | ;Init comparator mode             |

| MOVWF    | CMCON       | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO | ;Select Bank1                     |

| MOVLW    | 0x07        | ;Initialize data direction        |

| MOVWF    | TRISA       | ;Set RA<2:0> as inputs            |

|          |             | ;RA<4:3> as outputs               |

|          |             | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO | ;Select Bank 0                    |

| CALL     | DELAY10     | ;10µs delay                       |

| MOVF     | CMCON, F    | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF   | ;Clear pending interrupts         |

| BSF      | STATUS, RPO | ;Select Bank 1                    |

| BSF      | PIE1,CMIE   | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO | ;Select Bank 0                    |

| BSF      |             | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE | ;Global interrupt enable          |

| 101      | INICON, GIE | , Grobar incerrupt enable         |

# 9.2 Comparator Operation

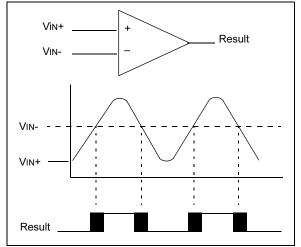

A single comparator is shown in Figure 9-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 9-2 represent the uncertainty due to input offsets and response time.

# 9.3 Comparator Reference

An external or internal reference signal may be used depending on the Comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 9-2).

SINGLE COMPARATOR

## 9.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSs and VDD, and can be applied to either pin of the comparator(s).

# 9.3.2 INTERNAL REFERENCE SIGNAL

The Comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 10.0, Voltage Reference Manual, contains a detailed description of the Voltage Reference module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 9-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 9.4 Comparator Response Time

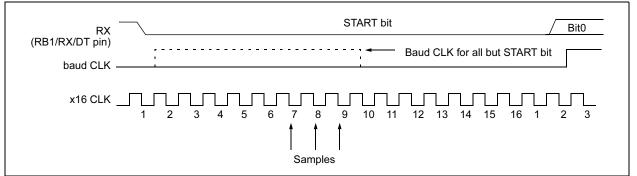

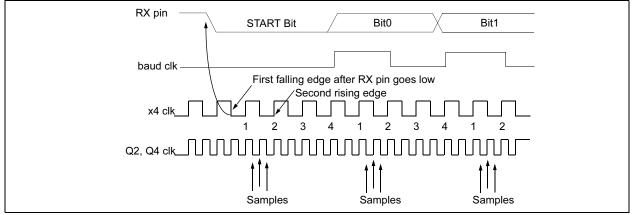

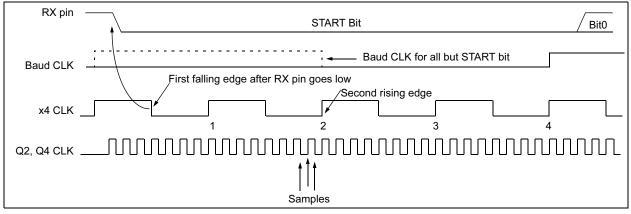

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise the maximum delay of the comparators should be used (Table 17-1). The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

# FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

# FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

# FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

# 12.3 USART Function

The USART function is similar to that on the PIC16C74B, which includes the BRGH = 1 fix.

### 12.3.1 USART 9-BIT RECEIVER WITH ADDRESS DETECT

When the RX9 bit is set in the RCSTA register, 9 bits are received and the ninth bit is placed in the RX9D bit of the RCSTA register. The USART module has a special provision for multiprocessor communication. Multiprocessor communication is enabled by setting the ADEN bit (RCSTA<3>) along with the RX9 bit. The port is now programmed so when the last bit is received, the contents of the Receive Shift Register (RSR) are transferred to the receive buffer. The ninth bit of the RSR (RSR<8>) is transferred to RX9D, and the receive interrupt is set if, and only, if RSR<8> = 1. This feature can be used in a multiprocessor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by setting the ninth bit (RSR<8>) to a '1' (instead of a '0' for a data byte). If the ADEN and RX9 bits are set in the slave's RCSTA register, enabling multiprocessor communication, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is being addressed. The addressed slave will then clear its ADEN bit and prepare to receive data bytes from the master.

When ADEN is enabled (='1'), all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost. The ADEN bit will only take effect when the receiver is configured in 9-bit mode (RX9 = '1'). When ADEN is disabled (='0'), all data bytes are received and the 9th bit can be used as the PARITY bit.

The USART Receive Block Diagram is shown in Figure 12-8.

Reception is enabled by setting bit CREN (RCSTA<4>).

#### 12.3.1.1 Setting up 9-bit mode with Address Detect

Steps to follow when setting up an Asynchronous or Synchronous Reception with Address Detect Enabled:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable asynchronous or synchronous communication by setting or clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. Set bit RX9 to enable 9-bit reception.

- 5. Set ADEN to enable address detect.

- 6. Enable the reception by setting enable bit CREN or SREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- 9. If any error occurred, clear the error by clearing enable bit CREN if it was already set.

- If the device has been addressed (RSR<8> = 1 with address match enabled), clear the ADEN and RCIF bits to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address | Name  | Bit 7                          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 2 Bit 1 Bit 0 PC |        | Value on<br>POR |      |      | e on<br>other<br>ETS |

|---------|-------|--------------------------------|-------|-------|-------|-------|--------|----------------------|--------|-----------------|------|------|----------------------|

| 0Ch     | PIR1  | EEIF                           | CMIF  | RCIF  | TXIF  | —     | CCP1IF | TMR2IF               | TMR1IF | 0000            | -000 | 0000 | -000                 |

| 18h     | RCSTA | SPEN                           | RX9   | SREN  | CREN  | ADEN  | FERR   | OERR                 | RX9D   | 0000            | -00x | 0000 | -00x                 |

| 1Ah     | RCREG | RX7                            | RX6   | RX5   | RX4   | RX3   | RX2    | RX1                  | RX0    | 0000            | 0000 | 0000 | 0000                 |

| 8Ch     | PIE1  | EEIE                           | CMIE  | RCIE  | TXIE  | _     | CCP1IE | TMR2IE               | TMR1IE | 0000            | -000 | 0000 | -000                 |

| 98h     | TXSTA | CSRC                           | TX9   | TXEN  | SYNC  | _     | BRGH   | TRMT                 | TX9D   | 0000            | -010 | 0000 | -010                 |

| 99h     | SPBRG | G Baud Rate Generator Register |       |       |       |       |        |                      |        |                 |      | 0000 | 0000                 |

### TABLE 12-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

# PIC16F62X

| REGISTER 13-2: | EECON1 F                                                                                                                                                                                                | REGISTER                                    | (ADDRES        | SS: 9Ch)     |                       |              |                |           |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------|--------------|-----------------------|--------------|----------------|-----------|--|--|

|                | U-0                                                                                                                                                                                                     | U-0                                         | U-0            | U-0          | R/W-x                 | R/W-0        | R/S-0          | R/S-x     |  |  |

|                | —                                                                                                                                                                                                       | _                                           | _              | —            | WRERR                 | WREN         | WR             | RD        |  |  |

|                | bit 7                                                                                                                                                                                                   |                                             |                |              |                       |              |                | bit 0     |  |  |

| bit 7-4        | Unimpleme                                                                                                                                                                                               | Unimplemented: Read as '0'                  |                |              |                       |              |                |           |  |  |

| bit 3          | WRERR: E                                                                                                                                                                                                | EPROM Er                                    | ror Flag bit   |              |                       |              |                |           |  |  |

|                | normal                                                                                                                                                                                                  | operation is<br>operation o<br>te operatior | r BOD Res      | et)          | d (any MCLR R         | eset, any \  | WDT Reset      | during    |  |  |

| bit 2          | WREN: EE                                                                                                                                                                                                | PROM Write                                  | e Enable bi    | t            |                       |              |                |           |  |  |

|                | 1 = Allows<br>0 = Inhibits                                                                                                                                                                              |                                             |                | ROM          |                       |              |                |           |  |  |

| bit 1          | WR: Write                                                                                                                                                                                               | Control bit                                 |                |              |                       |              |                |           |  |  |

|                | can onl                                                                                                                                                                                                 | y be set (no                                | ot cleared) ii |              | y hardware onc<br>ete | e write is c | complete. T    | he WR bit |  |  |

| bit 0          | RD: Read (                                                                                                                                                                                              | Control bit                                 |                |              |                       |              |                |           |  |  |

|                | <ul> <li>1 = Initiates an EEPROM read (read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software).</li> <li>0 = Does not initiate an EEPROM read</li> </ul> |                                             |                |              |                       |              |                |           |  |  |

|                | Legend:                                                                                                                                                                                                 |                                             |                |              |                       |              |                |           |  |  |

|                | R = Readal                                                                                                                                                                                              | ole bit                                     | W = V          | Vritable bit | U = Unimple           | emented bi   | it, read as '( | D'        |  |  |

|                | -n = Value a                                                                                                                                                                                            | at POR                                      | '1' = B        | lit is set   | '0' = Bit is c        | leared       | x = Bit is ur  | nknown    |  |  |

# 14.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16F62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Brown-out Reset (BOD)

- 7. Interrupts

- 8. Watchdog Timer (WDT)

- 9. SLEEP

- 10. Code protection

- 11. ID Locations

- 12. In-circuit Serial Programming

The PIC16F62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a Brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The ER oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

# 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special configuration memory space (2000h – 3FFFh), which can be accessed only during programming. See Programming Specification.

# **REGISTER 14-1: CONFIGURATION WORD**

| CP1                         | CP0                                                          | CP1                                                                                                                                                                                                                                                     | CP0                                                                                                                                                          | _                                                                                                           | CPD                                                                         | LVP                                                                       | BODEN                                                                               | MCLRE                                                                          | FOSC2                                                        | PWRTE                      | WDTE | F0SC1 | F0SC0 |

|-----------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------|------|-------|-------|

| bit 13                      |                                                              |                                                                                                                                                                                                                                                         | ·                                                                                                                                                            |                                                                                                             |                                                                             |                                                                           | -                                                                                   |                                                                                |                                                              |                            |      |       | bit 0 |

| bit 13-10:                  | Code<br>11 =<br>01 =<br>00 =<br>Code<br>11 =<br>10 =<br>01 = | protection<br>Program<br>0400h-07<br>0200h-07<br>0000h-07<br>protection<br>Program<br>Program<br>0200h-03                                                                                                                                               | le Protection<br>n for 2K prog<br>memory cod<br>7FFh code p<br>7FFh code p<br>7FFh code p<br>n for 1K prog<br>memory cod<br>3FFh code p<br>3FFh code p       | gram memore<br>rotected<br>rotected<br>otected<br>gram memore<br>de protection<br>de protection<br>rotected | on off<br>ory<br>on off                                                     |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 9:                      |                                                              |                                                                                                                                                                                                                                                         | ed: Read as                                                                                                                                                  |                                                                                                             |                                                                             |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 8:                      | <b>CPD:</b><br>1 = Da                                        | Data Coo<br>ata memo                                                                                                                                                                                                                                    | de Protectior<br>ory code pro                                                                                                                                | n bit <sup>(3)</sup><br>tection off                                                                         |                                                                             |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 7:                      | 1 = R                                                        | <ul> <li>0 = Data memory code protected</li> <li>LVP: Low Voltage Programming Enable</li> <li>1 = RB4/PGM pin has PGM function, low voltage programming enabled</li> <li>0 = RB4/PGM is digital I/O, HV on MCLR must be used for programming</li> </ul> |                                                                                                                                                              |                                                                                                             |                                                                             |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 6:                      | 1 = B(                                                       | BODEN: Brown-out Detect Reset Enable bit <sup>(1)</sup><br>1 = BOD Reset enabled<br>0 = BOD Reset disabled                                                                                                                                              |                                                                                                                                                              |                                                                                                             |                                                                             |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 5:                      | 1 = R                                                        | A5/MCLF                                                                                                                                                                                                                                                 | MCLR pin fu<br>pin functior<br>pin functior                                                                                                                  | is MCLR                                                                                                     |                                                                             | R internally                                                              | tied to VDD                                                                         | )                                                                              |                                                              |                            |      |       |       |

| bit 3:                      | 1 = P                                                        | <b>TEN</b> : Pow<br>WRT disa<br>WRT ena                                                                                                                                                                                                                 |                                                                                                                                                              | Enable bit                                                                                                  | (1)                                                                         |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 2:                      | 1 = W                                                        | <b>EN</b> : Watcl<br>DT enab                                                                                                                                                                                                                            |                                                                                                                                                              | Enable bit                                                                                                  |                                                                             |                                                                           |                                                                                     |                                                                                |                                                              |                            |      |       |       |

| bit 4, 1-0:                 | 111 =<br>110 =<br>101 =<br>011 =<br>010 =<br>010 =           | ER osci<br>ER osci<br>INTRC<br>INTRC<br>EC: I/O<br>HS osci<br>XT osci                                                                                                                                                                                   | 0: Oscillator<br>illator: CLKC<br>illator: I/O fui<br>oscillator: Cl<br>oscillator: I/C<br>function on<br>illator: High s<br>llator: Crysta<br>llator: Low p | UT function<br>nction on R<br>LKOUT fun<br>D function of<br>RA6/OSC2<br>speed cryst<br>Il/resonato          | n on RA6/0<br>A6/OSC2/<br>ction on R<br>on RA6/OS<br>/CLKOUT<br>al/resonate | CLKOUT p<br>A6/OSC2/C<br>C2/CLKOL<br>pin, CLKIN<br>or on RA6/<br>SC2/CLKC | in, Resistor<br>CLKOUT pir<br>JT pin, I/O f<br>I on RA7/O<br>OSC2/CLK<br>OUT and RA | on RA7/O<br>n, I/O funct<br>function on<br>SC1/CLKIN<br>OUT and R<br>A7/OSC1/C | SC1/CLKII<br>ion on RA7<br>RA7/OSC<br>N<br>A7/OSC1/<br>SLKIN | N<br>7/OSC1/CLł<br>1/CLKIN | KIN  |       |       |

|                             | Note                                                         | Er<br>2: Al<br>3: Th                                                                                                                                                                                                                                    | nabling Brow<br>nsure the Po<br>I of the CP1:<br>ne entire data<br>hen MCLR i                                                                                | wer-up Tim<br>CP0 pairs<br>a EEPROM                                                                         | er is enab<br>have to be<br>I will be era                                   | led anytime<br>given the s<br>ased when                                   | e Brown-ou<br>same value<br>the code p                                              | t Detect Re<br>to enable to<br>rotection is                                    | eset is enab<br>the code pr<br>turned off.                   | oled.<br>rotection sc      |      |       | WRTE. |

| <b>Legend</b><br>R = Readat |                                                              |                                                                                                                                                                                                                                                         |                                                                                                                                                              |                                                                                                             | itable bit                                                                  |                                                                           |                                                                                     |                                                                                | ited bit, rea                                                |                            |      |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0 | )'                 |

|-------------------|------------------|-----------------------------------|--------------------|

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared                | x = bit is unknown |

-

# 14.5.5 TIMEOUT SEQUENCE

On power-up the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired. Then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in ER mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 14-8, Figure 14-9 and Figure 14-10 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 14-9). This is useful for testing purposes or to synchronize more than one PIC16F62X device operating in parallel.

Table 14-7 shows the RESET conditions for some special registers, while Table 14-8 shows the RESET conditions for all the registers.

## 14.5.6 POWER CONTROL (PCON) STATUS REGISTER

The Power Control/STATUS register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{BOD}$  (Brown-out).  $\overline{BOD}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent RESETS to see if  $\overline{BOD} = 0$  indicating that a brown-out has occurred. The  $\overline{BOD}$  STATUS bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Power-on Reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Detect  | Wake-up    |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | Reset             | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| ER, INTRC, EC            | 72 ms             | _         | 72 ms             | —          |  |

# TABLE 14-4: TIMEOUT IN VARIOUS SITUATIONS

| IABLE 14 | 4-5: SI/ | 4105/PC |    | AND THEIR SIGNIFICANCE             |

|----------|----------|---------|----|------------------------------------|

| POR      | BOD      | то      | PD |                                    |

| 0        | Х        | 1       | 1  | Power-on Reset                     |

| 0        | х        | 0       | х  | Illegal, TO is set on POR          |

| 0        | х        | х       | 0  | Illegal, PD is set on POR          |

| 1        | 0        | Х       | Х  | Brown-out Detect Reset             |

| 1        | 1        | 0       | u  | WDT Reset                          |

| 1        | 1        | 0       | 0  | WDT Wake-up                        |

| 1        | 1        | u       | u  | MCLR Reset during normal operation |

| 1        | 1        | 1       | 0  | MCLR Reset during SLEEP            |

## TABLE 14-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Legend: u = unchanged, x = unknown.

### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx             | 000q quuu                                      |

| 8Eh     | PCON   | _     | _     | _     | -     | OSCF  | Reset | POR   | BOD   | 1-0x                  | u-uq                                           |

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect Reset and Watchdog Timer Reset during normal operation.

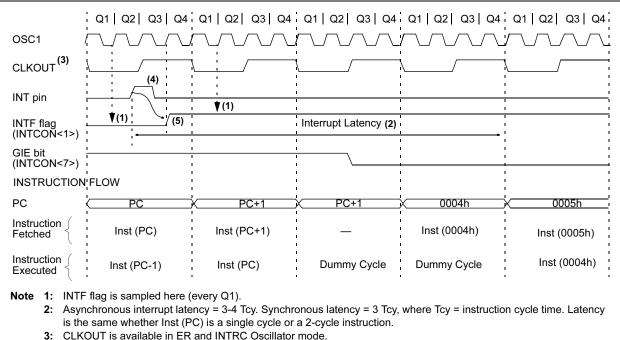

#### 14.6.1 **RB0/INT INTERRUPT**

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.9 for details on SLEEP, and Figure 14-17 for timing of wake-up from SLEEP through RB0/INT interrupt.

#### 14.6.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can enabled/disabled by setting/clearing T0IE he (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 14.6.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

#### 14.6.4 COMPARATOR INTERRUPT

See Section 9.6 for complete description of comparator interrupts.

#### **FIGURE 14-15:** INT PIN INTERRUPT TIMING

4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 14-10: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name            | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|-----------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config.<br>bits | LVP   | BODEN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |

| 81h     | OPTION          | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: -= Unimplemented location, read as "0", + = Reserved for future use

**Note 1:** Shaded cells are not used by the Watchdog Timer.

### 14.9 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |

|-------|-------------------------------------------|

|       | by a WDT timeout does not drive MCLR      |

|       | pin low.                                  |

# PIC16F62X

| CLRW             | Clear W                                                               |                                       |           |       |   | COMF   |

|------------------|-----------------------------------------------------------------------|---------------------------------------|-----------|-------|---|--------|

| Syntax:          | [ label ]                                                             | CLRW                                  |           |       | I | Syntax |

| Operands:        | None                                                                  |                                       |           |       |   | Opera  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (V) \\ 1 \rightarrow Z \end{array}$ | W)                                    |           |       |   | Operat |