# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

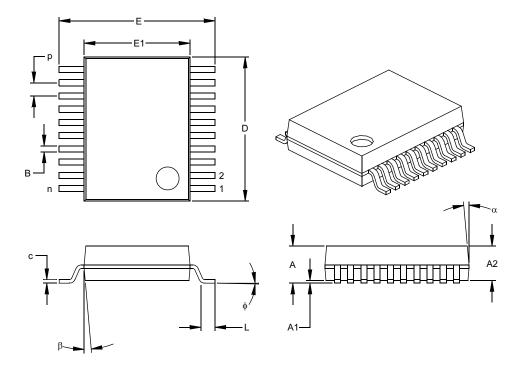

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628-04i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

# 3.0 MEMORY ORGANIZATION

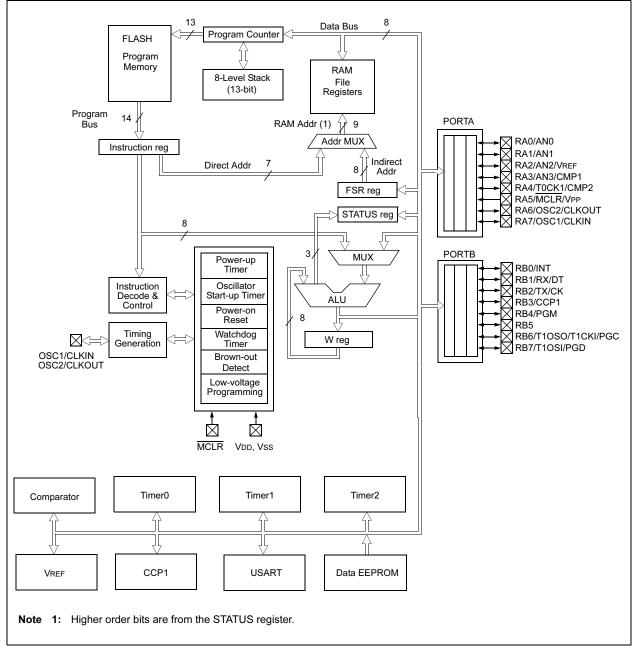

### 3.1 Program Memory Organization

The PIC16F62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) for the PIC16F627 and 2K x 14 (0000h - 07FFh) for the PIC16F628 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space (PIC16F627) or 2K x 14 space (PIC16F628). The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 3-1).

FIGURE 3-1: PROGRAM MEMORY MAP AND STACK

# 3.2 Data Memory Organization

The data memory (Figure 3-2) is partitioned into four banks, which contain the general purpose registers and the Special Function Registers (SFR). The SFR's are located in the first 32 locations of each Bank. Register locations 20-7Fh, A0h-FFh, 120h-14Fh, 170h-17Fh and 1F0h-1FFh are general purpose registers implemented as static RAM.

The Table below lists how to access the four banks of registers:

|       | RP1 | RP0 |

|-------|-----|-----|

| Bank0 | 0   | 0   |

| Bank1 | 0   | 1   |

| Bank2 | 1   | 0   |

| Bank3 | 1   | 1   |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

#### 3.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $224 \times 8$  in the PIC16F62X. Each is accessed either directly or indirectly through the File Select Register FSR (See Section 3.4).

| Address | Name   | Bit 7            | Bit 6           | Bit 5       | Bit 4        | Bit 3        | Bit 2         | Bit 1         | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|-----------------|-------------|--------------|--------------|---------------|---------------|--------------|-----------------------------------------|--------------------|

| Bank 2  |        |                  |                 |             |              |              |               |               |              |                                         |                    |

| 100h    | INDF   | Addressin ister) | g this locatior | n uses cont | ents of FSF  | to address   | s data mem    | ory (not a pl | hysical reg- | XXXX XXXX                               | 25                 |

| 101h    | TMR0   | RBPU             | INTEDG          | TOCS        | TOSE         | PSA          | PS2           | PS1           | PS0          | 1111 1111                               | 43                 |

| 102h    | PCL    | Program 0        | Counter's (PC   | ) Least Sig | nificant Byt | e            |               |               |              | 0000 0000                               | 25                 |

| 103h    | STATUS | IRP              | RP1             | RP0         | TO           | PD           | Z             | DC            | С            | 0001 1xxx                               | 19                 |

| 104h    | FSR    | Indirect da      | ata memory a    | ddress poir | nter         | 1            | 1             |               |              | xxxx xxxx                               | 25                 |

| 105h    | _      | Unimplem         | iented          |             |              |              |               |               |              | _                                       | _                  |

| 106h    | PORTB  | RB7              | RB6             | RB5         | RB4          | RB3          | RB2           | RB1           | RB0          | xxxx xxxx                               | 34                 |

| 107h    | _      | Unimplem         | ented           |             | •            |              | •             |               |              | _                                       | _                  |

| 108h    | _      | Unimplem         | ented           |             |              |              |               |               |              |                                         | _                  |

| 109h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 10Ah    | PCLATH |                  | _               | _           | Write        | buffer for u | pper 5 bits o | of program of | counter      | 0 0000                                  | 25                 |

| 10Bh    | INTCON | GIE              | PEIE            | T0IE        | INTE         | RBIE         | T0IF          | INTF          | RBIF         | 0000 000x                               | 21                 |

| 10Ch    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 10Dh    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 10Eh    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 10Fh    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 110h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 111h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 112h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 113h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 114h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 115h    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

| 116h    | _      | Unimplem         | ented           |             |              |              |               |               |              |                                         | _                  |

| 117h    | —      | Unimplem         | ented           |             |              |              |               |               |              |                                         | _                  |

| 118h    | —      | Unimplem         | ented           |             |              |              |               |               |              |                                         | _                  |

| 119h    | —      | Unimplem         | ented           |             |              |              |               |               |              |                                         | _                  |

| 11Ah    | _      | Unimplem         | ented           |             |              |              |               |               |              |                                         | —                  |

| 11Bh    | _      | Unimplem         | ented           |             |              |              |               |               |              |                                         | —                  |

| 11Ch    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | —                  |

| 11Dh    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | —                  |

| 11Eh    | _      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | —                  |

| 11Fh    | —      | Unimplem         | ented           |             |              |              |               |               |              | _                                       | _                  |

TABLE 3-3: SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

#### 3.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0, and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for |

|-------|-------------------------------------------|

|       | TMR0, assign the prescaler to the WDT     |

|       | (PSA = 1). See Section 6.3.1              |

#### **REGISTER 3-2:** OPTION REGISTER (ADDRESS: 81h, 181h)

101

110 111

Legend:

R = Readable bit

-n = Value at POR

1:64

1:128

1:256

|         |                                                                                                                                             |                                 | UBBILL                    | <i></i> ,,         | ,,                         |       |       |       |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------|--------------------|----------------------------|-------|-------|-------|--|--|--|--|

|         | R/W-1                                                                                                                                       | R/W-1                           | R/W-1                     | R/W-1              | R/W-1                      | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|         | RBPU                                                                                                                                        | INTEDG                          | TOCS                      | TOSE               | PSA                        | PS2   | PS1   | PS0   |  |  |  |  |

|         | bit 7                                                                                                                                       |                                 | •                         |                    |                            |       |       | bit 0 |  |  |  |  |

| bit 7   | <b>RBPU</b> : PO                                                                                                                            | RTB Pull-ur                     | o Enable bit              | :                  |                            |       |       |       |  |  |  |  |

|         | <b>RBPU</b> : PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual port latch values |                                 |                           |                    |                            |       |       |       |  |  |  |  |

| bit 6   | INTEDG: In                                                                                                                                  | nterrupt Edg                    | je Select bi              | t                  |                            |       |       |       |  |  |  |  |

|         |                                                                                                                                             | pt on rising o<br>pt on falling | 0                         |                    |                            |       |       |       |  |  |  |  |

| bit 5   | TOCS: TM                                                                                                                                    | R0 Clock Sc                     | ource Selec               | t bit              |                            |       |       |       |  |  |  |  |

|         | 1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                                            |                                 |                           |                    |                            |       |       |       |  |  |  |  |

| bit 4   | TOSE: TMF                                                                                                                                   | R0 Source E                     | Edge Select               | bit                |                            |       |       |       |  |  |  |  |

|         |                                                                                                                                             | -                               |                           |                    | 4/T0CKI pin<br>4/T0CKI pin |       |       |       |  |  |  |  |

| bit 3   | PSA: Pres                                                                                                                                   | caler Assigr                    | ment bit                  |                    |                            |       |       |       |  |  |  |  |

|         | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                            |                                 |                           |                    |                            |       |       |       |  |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                                                    | Prescaler R                     | ate Select k              | oits               |                            |       |       |       |  |  |  |  |

|         | E                                                                                                                                           | Bit Value T                     | MR0 Rate                  | WDT Rate           |                            |       |       |       |  |  |  |  |

|         | -                                                                                                                                           | 000<br>001                      | 1:2<br>1:4                | 1:1<br>1:2         |                            |       |       |       |  |  |  |  |

|         |                                                                                                                                             | 010<br>011<br>100               | 1 : 8<br>1 : 16<br>1 : 32 | 1:4<br>1:8<br>1:16 |                            |       |       |       |  |  |  |  |

1:32 1:64

1:128

W = Writable bit

'1' = Bit is set

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

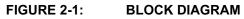

# 4.0 GENERAL DESCRIPTION

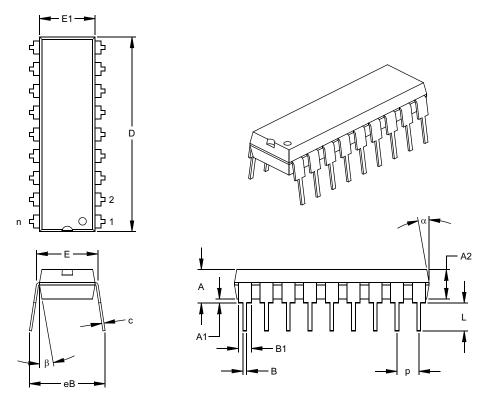

The PIC16F62X are 18-Pin FLASH-based members of the versatile PIC16CXX family of low cost, high performance, CMOS, fully static, 8-bit microcontrollers.

All PICmicro<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16F62X have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16F62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC16F62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption.

The PIC16F62X has eight oscillator configurations. The single pin ER oscillator provides a low cost solution. The LP oscillator minimizes power consumption, XT is a standard crystal, INTRC is a self-contained internal oscillator. The HS is for High Speed crystals. The EC mode is for an external clock source. The SLEEP (Power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external interrupts, internal interrupts, and RESETS.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

Table 4-1 shows the features of the PIC16F62X midrange microcontroller families.

A simplified block diagram of the PIC16F62X is shown in Figure 2.1.

The PIC16F62X series fits in applications ranging from battery chargers to low power remote sensors. The FLASH technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series ideal for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F62X very versatile.

# 4.1 Development Support

The PIC16F62X family is supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer. A Third Party "C" compiler support tool is also available.

|             |                                      | PIC16F627                        | PIC16F628                        | PIC16LF627                       | PIC16LF628                       |

|-------------|--------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 4                                | 4                                |

|             | FLASH Program Memory (words)         | 1024                             | 2048                             | 1024                             | 2048                             |

| Memory      | RAM Data Memory (bytes)              | 224                              | 224                              | 224                              | 224                              |

|             | EEPROM Data Memory (bytes)           | 128                              | 128                              | 128                              | 128                              |

|             | Timer Module(s)                      | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 | TMR0, TMR1, TMR2                 |

|             | Comparator(s)                        | 2                                | 2                                | 2                                | 2                                |

| Peripherals | Capture/Compare/PWM modules          | 1                                | 1                                | 1                                | 1                                |

|             | Serial Communications                | USART                            | USART                            | USART                            | USART                            |

|             | Internal Voltage Reference           | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Interrupt Sources                    | 10                               | 10                               | 10                               | 10                               |

|             | I/O Pins                             | 16                               | 16                               | 16                               | 16                               |

| Features    | Voltage Range (Volts)                | 3.0-5.5                          | 3.0-5.5                          | 2.0-5.5                          | 2.0-5.5                          |

|             | Brown-out Detect                     | Yes                              | Yes                              | Yes                              | Yes                              |

|             | Packages                             | 18-pin DIP, SOIC,<br>20-pin SSOP |

## TABLE 4-1:PIC16F62X FAMILY OF DEVICES

All PICmicro® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16F62X Family devices use serial programming with clock pin RB6 and data pin RB7.

# 5.0 I/O PORTS

The PIC16F62X have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

## 5.1 PORTA and TRISA Registers

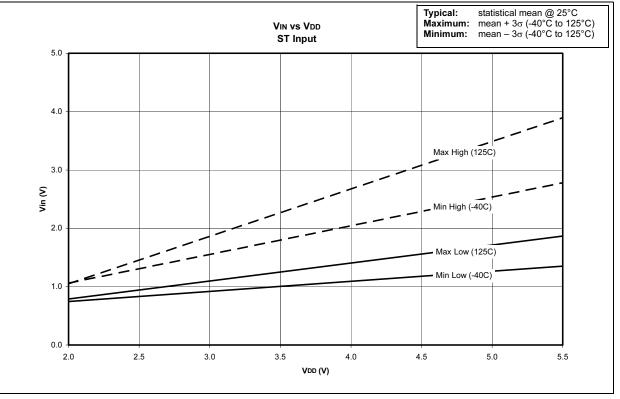

PORTA is an 8-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the T0CKI clock input. RA5 is a Schmitt Trigger input only and has no output drivers. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control register) register. When selected as a comparator input, these pins will read as '0's.

Note: RA5 shares function with VPP. When VPP voltage levels are applied to RA5, the device will enter Programming mode.

- **Note 1:** On RESET, the TRISA register is set to all inputs. The digital inputs are disabled and the comparator inputs are forced to ground to reduce current consumption.

- 2: TRISA<6:7> is overridden by oscillator configuration. When PORTA<6:7> is overridden, the data reads '0' and the TRISA<6:7> bits are ignored.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the Comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### EXAMPLE 5-1: Initializing PORTA

| CLRF  | PORTA   | ;Initialize PORTA by<br>;setting output data latches                                                     |

|-------|---------|----------------------------------------------------------------------------------------------------------|

| MOVLW |         | ;Turn comparators off and                                                                                |

| MOVWF | CMCON   | ;enable pins for I/O<br>;functions                                                                       |

| BCF   | STATUS, | RP1                                                                                                      |

| BSF   | STATUS, | RP0;Select Bank1                                                                                         |

| MOVLW | 0x1F    | ;Value used to initialize<br>;data direction                                                             |

| MOVWF | TRISA   | ;Set RA<4:0> as inputs<br>;TRISA<5> always<br>;read as `1'.<br>;TRISA<7:6><br>;depend on oscillator mode |

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module. Additional information available in the PICmicro™ Mid Pange MCLL Eamily Reference

PICmicro™ Mid-Range MCU Family Reference Manual, DS31010A.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles. The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4,..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

# 6.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP.

# 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-1). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

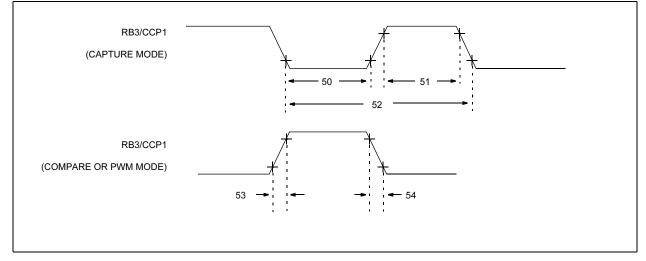

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device. See Table 17-7.

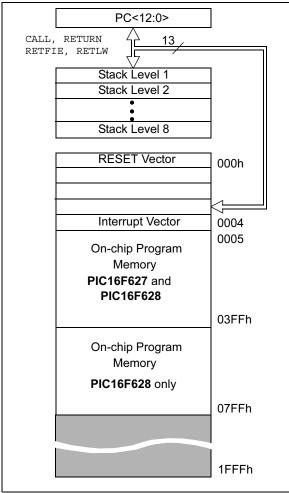

## 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

#### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

| <b>REGISTER 8-1:</b> | T2CO                     | N: TIMER C    |              | REGISTER     | (ADDRESS:   | 12h)   |         |         |  |  |

|----------------------|--------------------------|---------------|--------------|--------------|-------------|--------|---------|---------|--|--|

|                      | U-0                      | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/W-0  | R/W-0   | R/W-0   |  |  |

|                      | _                        | TOUTPS3       | TOUTPS2      | TOUTPS1      | TOUTPS0     | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |

|                      | bit 7                    |               |              |              |             |        |         | bit 0   |  |  |

|                      |                          |               |              |              |             |        |         |         |  |  |

| bit 7                | Unimplem                 | ented: Read   | as '0'       |              |             |        |         |         |  |  |

| bit 6-3              | TOUTPS3:                 | TOUTPS0: 1    | Timer2 Outpu | ut Postscale | Select bits |        |         |         |  |  |

|                      | 0000 = 1:1               | Postscale V   | alue         |              |             |        |         |         |  |  |

|                      | 0001 = 1:2               | Postscale V   | alue         |              |             |        |         |         |  |  |

|                      | •                        |               |              |              |             |        |         |         |  |  |

|                      | •                        |               |              |              |             |        |         |         |  |  |

|                      | 1111 = 1:1               | 6 Postscale   |              |              |             |        |         |         |  |  |

|                      |                          |               |              |              |             |        |         |         |  |  |

| bit 2                | TMR2ON:                  | Timer2 On bi  | it           |              |             |        |         |         |  |  |

|                      | 1 = Timer2               | is on         |              |              |             |        |         |         |  |  |

|                      | 0 = Timer2               | is off        |              |              |             |        |         |         |  |  |

| bit 1-0              | T2CKPS1:                 | T2CKPS0: T    | imer2 Clock  | Prescale Se  | lect bits   |        |         |         |  |  |

|                      | 00 = 1:1 Prescaler Value |               |              |              |             |        |         |         |  |  |

|                      |                          | rescaler Valu | -            |              |             |        |         |         |  |  |

|                      | 1x = 1:16                | Prescaler Val | ue           |              |             |        |         |         |  |  |

|                      | <b></b>                  |               |              |              |             |        |         |         |  |  |

|                      | Legend:                  |               |              |              |             |        |         |         |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

W = Writable bit

U = Unimplemented bit, read as '0'

#### TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

R = Readable bit

| Address               | Name   | Bit 7       | Bit 6                    | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|-------------|--------------------------|---------|---------|---------|--------|---------|-----------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE         | PEIE                     | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF      | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF        | CMIF                     | RCIF    | TXIF    |         | CCP1IF | TMR2IF  | TMR1IF    | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE        | CMIE                     | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE    | 0000 -000       | 0000 -000                       |

| 11h                   | TMR2   | Timer2 mod  | Fimer2 module's register |         |         |         |        |         |           | 0000 0000       | 0000 0000                       |

| 12h                   | T2CON  | _           | TOUTPS3                  | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000       | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri | imer2 Period Register    |         |         |         |        |         | 1111 1111 | 1111 1111       |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

NOTES:

| TER 12-2: | RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h)                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                  |              |               |       |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------|---------------|-------|--|--|--|--|--|--|

|           | R/W-0 R/W-0                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0          | R/W-0            | R-0          | R-0           | R-x   |  |  |  |  |  |  |

|           | SPEN RX9                                                                                                             | SREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CREN           | ADEN             | FERR         | OERR          | RX9D  |  |  |  |  |  |  |

|           | bit 7                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | ·                |              |               | bit 0 |  |  |  |  |  |  |

| bit 7     | (Configures RB1/RX/D<br>1 = Serial port enabled                                                                      | <b>SPEN</b> : Serial Port Enable bit<br>(Configures RB1/RX/DT and RB2/TX/CK pins as serial port pins when bits TRISB<2:17> are set)<br>1 = Serial port enabled<br>0 = Serial port disabled                                                                                                                                                                                                                                                                          |                |                  |              |               |       |  |  |  |  |  |  |

| bit 6     | <b>RX9</b> : 9-bit Receive En<br>1 = Selects 9-bit recep                                                             | <b>RX9</b> : 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>0 = Selects 8-bit reception                                                                                                                                                                                                                                                                                                                                                                 |                |                  |              |               |       |  |  |  |  |  |  |

| bit 5     | Asynchronous mode:<br>Don't care<br>Synchronous mode - r<br>1 = Enables single<br>0 = Disables single                | SREN: Single Receive Enable bit<br><u>Asynchronous mode:</u><br>Don't care<br><u>Synchronous mode - master:</u><br>1 = Enables single receive<br>0 = Disables single receive<br>This bit is cleared after reception is complete.                                                                                                                                                                                                                                    |                |                  |              |               |       |  |  |  |  |  |  |

|           | Unused in this mod                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                  |              |               |       |  |  |  |  |  |  |

| bit 4     | Asynchronous mode:<br>1 = Enables continu<br>0 = Disables contin<br><u>Synchronous mode</u> :<br>1 = Enables continu | <ul> <li>1 = Enables continuous receive</li> <li>0 = Disables continuous receive</li> <li><u>Synchronous mode</u>:</li> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> </ul>                                                                                                                                                                                                                                        |                |                  |              |               |       |  |  |  |  |  |  |

| bit 3     | Asynchronous mode 9<br>1 = Enables addres<br>0 = Disables addres<br>Asynchronous mode 8                              | <ul> <li>0 = Disables continuous receive</li> <li>ADEN: Address Detect Enable bit</li> <li>Asynchronous mode 9-bit (RX9 = 1):</li> <li>1 = Enables address detection, enable interrupt and load of the receive buffer when RSR&lt;8&gt; is set</li> <li>0 = Disables address detection, all bytes are received, and ninth bit can be used as PARITY bit</li> <li>Asynchronous mode 8-bit (RX9=0):</li> <li>Unused in this mode</li> <li>Synchronous mode</li> </ul> |                |                  |              |               |       |  |  |  |  |  |  |

| bit 2     | FERR: Framing Error I<br>1 = Framing error (Car<br>0 = No framing error                                              | oit                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | reading RCF    | REG register and | receive next | valid byte)   |       |  |  |  |  |  |  |

| bit 1     | OERR: Overrun Error<br>1 = Overrun error (Car<br>0 = No overrun error                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | clearing bit C | REN)             |              |               |       |  |  |  |  |  |  |

| bit 0     | <b>RX9D</b> : 9th bit of received data (Can be PARITY bit)                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                  |              |               |       |  |  |  |  |  |  |

|           | Legend:<br>R = Readable bit                                                                                          | W = V                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Vritable bit   | U = Unimpl       | emented b    | it, read as ' | 0'    |  |  |  |  |  |  |

| REGISTER 12-2: | RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS: 18h) |

|----------------|-----------------------------------------------------------|

|                |                                                           |

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

# 13.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead it is indirectly addressed through the Special Function Registers (SFRs). There are four SFRs used to read and write this memory. These registers are:

- EECON1

- EECON2 (Not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F62X devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The writetime will vary with voltage and temperature as well as from chip to chip. Please refer to AC specifications for exact limits.

When the device is code protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the Data EEPROM is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### REGISTER 13-1: EEADR REGISTER (ADDRESS: 9Bh)

|   | R/W      | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

|---|----------|-------|-------|-------|-------|-------|-------|-------|

|   | Reserved | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| _ | bit 7    |       |       |       |       |       |       | bit 0 |

#### bit 7 Unimplemented Address: Must be set to '0'

bit 6-0 **EEADR**: Specifies one of 128 locations of EEPROM Read/Write Operation

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 13.1 EEADR

The EEADR register can address up to a maximum of 256 bytes of data EEPROM. Only the first 128 bytes of data EEPROM are implemented and only seven of the eight bits in the register (EEADR<6:0>) are required.

The upper bit is address decoded. This means that this bit should always be '0' to ensure that the address is in the 128 byte memory space.

#### 13.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with five low order bits physically implemented. The upper-three bits are nonexistent and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRER<u>R bit is</u> set when a write operation is interrupted by a MCLR Reset or a WDT Timeout Reset during normal operation. In these situations, following RESET, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit EEIF in the PIR1 register is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the Data EEPROM write sequence.

|                  | •                                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal<br>'k' and the result is placed in the<br>W register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                          |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                            |  |  |  |  |  |  |

| ANDLW                                                                                                    | AND Literal with W                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> ] ANDLW k                                                                                                                                                                                                                                                                                                                                                                                                  |

| Operands:                                                                                                | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operation:                                                                                               | (W) .AND. (k) $\rightarrow$ (W)                                                                                                                                                                                                                                                                                                                                                                                           |

| Status Affected:                                                                                         | Z                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Encoding:                                                                                                | 11 1001 kkkk kkkk                                                                                                                                                                                                                                                                                                                                                                                                         |

| Description:                                                                                             | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register.                                                                                                                                                                                                                                                                                                    |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example                                                                                                  | ANDLW 0x5F                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                          | W = 0xA3<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                          | W = 0x03                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ANDWF                                                                                                    | AND W with f                                                                                                                                                                                                                                                                                                                                                                                                              |

| ANDWF<br>Syntax:                                                                                         | AND W with f [ label ] ANDWF f,d                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:                                                                                                  | [ <i>label</i> ] ANDWF f,d<br>0 ≤ f ≤ 127                                                                                                                                                                                                                                                                                                                                                                                 |

| Syntax:<br>Operands:                                                                                     | $ \begin{bmatrix} \textit{label} \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] $                                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:<br>Operation:                                                                       | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                    |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                                                                                                                               |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} ANDWF  f,d$ $0 \le f \le 127$ $d \in [0,1]$ $(W) .AND. (f) \rightarrow (dest)$ $Z$ $00 \qquad 0101  dfff \qquad ffff$                                                                                                                                                                                                                                                                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | [ <i>label</i> ] ANDWF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(W) .AND. (f) $\rightarrow$ (dest)<br>Z<br>00 0101 dfff ffff<br>AND the W register with register                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 \qquad 0101  dfff \qquad ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register \\ \hline \end{tabular}$                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d$ $0 \le f \le 127$ $d \in [0,1]$ (W) .AND. (f) $\rightarrow$ (dest) Z $00 \qquad 0101  dfff  ffff$ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                                                                               |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register \\ 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. \\ 1 \\ \end{bmatrix}$                                                                        |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} ANDWF  f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF & REG1, 1 \\ Before Instruction \\ W &= 0x17 \\ \end{bmatrix}$                   |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF } f,d \\ 0 \le f \le 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 \\ 1 \\ ANDWF REG1, 1 \\ Before Instruction \\ \end{bmatrix}$                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $\begin{bmatrix} label \end{bmatrix} \text{ ANDWF}  f,d \\ 0 \leq f \leq 127 \\ d \in [0,1] \\ (W) .AND. (f) \rightarrow (dest) \\ Z \\ \hline 00 & 0101 & dfff & ffff \\ \hline AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. 1 1 1 ANDWF REG1, 1 Before Instruction W = 0x17 \\ REG1 = 0xC2 \\ \hline \end{tabular}$ |

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |  |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                         |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | Add the contents of the W regis-<br>ter with register 'f'. If 'd' is 0 the<br>result is stored in the W register.<br>If 'd' is 1 the result is stored back<br>in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                              |  |  |  |  |  |  |

| Cycles:          | <b>1</b><br>ADDWF REG1, 0                                                                                                                                                      |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>REG1 = 0xC2<br>After Instruction<br>W = 0xD9<br>REG1 = 0xC2<br>Z = 0<br>C = 0<br>DC = 0                                                      |  |  |  |  |  |  |

## 16.14 PICDEM 1 PICmicro Demonstration Board

The PICDEM 1 demonstration board demonstrates the capabilities of the PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The sample microcontrollers provided with the PICDEM 1 demonstration board can be programmed with a PRO MATE II device programmer, or a PICSTART Plus development programmer. The PICDEM 1 demonstration board can be connected to the MPLAB ICE in-circuit emulator for testing. A prototype area extends the circuitry for additional application components. Features include analog input, push button switches and eight LEDs.

#### 16.15 PICDEM.net Internet/Ethernet Demonstration Board

The PICDEM.net demonstration board is an Internet/ Ethernet demonstration board using the PIC18F452 microcontroller and TCP/IP firmware. The board supports any 40-pin DIP device that conforms to the standard pinout used by the PIC16F877 or PIC18C452. This kit features a user friendly TCP/IP stack, web server with HTML, a 24L256 Serial EEPROM for Xmodem download to web pages into Serial EEPROM, ICSP/MPLAB ICD 2 interface connector, an Ethernet interface, RS-232 interface, and a 16 x 2 LCD display. Also included is the book and CD-ROM *"TCP/IP Lean, Web Servers for Embedded Systems,"* by Jeremy Bentham

### 16.16 PICDEM 2 Plus Demonstration Board

The PICDEM 2 Plus demonstration board supports many 18-, 28-, and 40-pin microcontrollers, including PIC16F87X and PIC18FXX2 devices. All the necessary hardware and software is included to run the demonstration programs. The sample microcontrollers provided with the PICDEM 2 demonstration board can be programmed with a PRO MATE II device programmer, PICSTART Plus development programmer, or MPLAB ICD 2 with a Universal Programmer Adapter. The MPLAB ICD 2 and MPLAB ICE in-circuit emulators may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area extends the circuitry for additional application components. Some of the features include an RS-232 interface, a 2 x 16 LCD display, a piezo speaker, an on-board temperature sensor, four LEDs, and sample PIC18F452 and PIC16F877 FLASH microcontrollers.

# 16.17 PICDEM 3 PIC16C92X Demonstration Board

The PICDEM 3 demonstration board supports the PIC16C923 and PIC16C924 in the PLCC package. All the necessary hardware and software is included to run the demonstration programs.

# 16.18 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. A programmed sample is included. The PRO MATE II device programmer, or the PICSTART Plus development programmer, can be used to reprogram the device for user tailored application development. The PICDEM 17 demonstration board supports program download and execution from external on-board FLASH memory. A generous prototype area is available for user hardware expansion.