Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 224 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628a-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16F62X

## **FLASH-Based 8-Bit CMOS Microcontrollers**

## **Devices Included in this Data Sheet:**

- PIC16F627

- PIC16F628

Referred to collectively as PIC16F62X

#### **High Performance RISC CPU:**

- · Only 35 instructions to learn

- All single cycle instructions (200 ns), except for program branches which are two-cycle

- · Operating speed:

- DC 20 MHz clock input

- DC 200 ns instruction cycle

|           |                  | Memory      |                |  |  |

|-----------|------------------|-------------|----------------|--|--|

| Device    | FLASH<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |

| PIC16F627 | 1024 x 14        | 224 x 8     | 128 x 8        |  |  |

| PIC16F628 | 2048 x 14        | 224 x 8     | 128 x 8        |  |  |

• Interrupt capability

- 16 special function hardware registers

- 8-level deep hardware stack

- Direct, Indirect and Relative addressing modes

## **Peripheral Features:**

- 16 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs are externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Timer1: 16-bit timer/counter with external crystal/ clock capability

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM (CCP) module

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- Universal Synchronous/Asynchronous Receiver/ Transmitter USART/SCI

- · 16 Bytes of common RAM

## **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Multiplexed MCLR-pin

- · Programmable weak pull-ups on PORTB

- · Programmable code protection

- Low voltage programming

- Power saving SLEEP mode

- · Selectable oscillator options

- FLASH configuration bits for oscillator options

- ER (External Resistor) oscillator

- · Reduced part count

- Dual speed INTRC

- Lower current consumption

- EC External Clock input

- XT Oscillator mode

- HS Oscillator mode

- LP Oscillator mode

- In-circuit Serial Programming<sup>™</sup> (via two pins)

- · Four user programmable ID locations

## **CMOS Technology:**

- Low power, high speed CMOS FLASH technology

- Fully static design

- · Wide operating voltage range

- PIC16F627 3.0V to 5.5V

- PIC16F628 3.0V to 5.5V

- PIC16LF627 2.0V to 5.5V

- PIC16LF628 2.0V to 5.5V

- Commercial, industrial and extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical @ 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

NOTES:

## 1.0 PIC16F62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F62X Product Identification System section (Page 167) at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 1.1 FLASH Devices

FLASH devices can be erased and reprogrammed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically-erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus, or PRO MATE<sup>®</sup> II programmers.

## 1.2 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 1.3 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 3.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 3.2.2.4 and Section 3.2.2.5 for a description of the comparator enable and flag bits.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 3-3: |            | REGISTER                      | (ADDRES       | S: 0Bh, 8  | Bh, 10Bh, 18             | Bh)          |               |       |

|---------------|------------|-------------------------------|---------------|------------|--------------------------|--------------|---------------|-------|

|               | R/W-0      | R/W-0                         | R/W-0         | R/W-0      | R/W-0                    | R/W-0        | R/W-0         | R/W-x |

|               | GIE        | PEIE                          | T0IE          | INTE       | RBIE                     | T0IF         | INTF          | RBIF  |

|               | bit 7      |                               |               |            |                          |              |               | bit 0 |

| bit 7         | GIE: Globa | al Interrupt E                | nable bit     |            |                          |              |               |       |

|               |            | s all unmas<br>es all interru | •             | ots        |                          |              |               |       |

| bit 6         | PEIE: Peri | oheral Interr                 | upt Enable    | bit        |                          |              |               |       |

|               |            | s all unmas<br>es all periph  |               |            | S                        |              |               |       |

| bit 5         | TOIE: TMR  | 0 Overflow                    | Interrupt En  | able bit   |                          |              |               |       |

|               |            | s the TMR0<br>es the TMR0     |               |            |                          |              |               |       |

| bit 4         | INTE: RB0  | /INT Externa                  | al Interrupt  | Enable bit |                          |              |               |       |

|               |            | s the RB0/II<br>es the RB0/I  |               |            |                          |              |               |       |

| bit 3         | RBIE: RB I | Port Change                   | e Interrupt E | nable bit  |                          |              |               |       |

|               |            | s the RB po<br>es the RB po   |               |            |                          |              |               |       |

| bit 2         | TOIF: TMR  | 0 Overflow                    | nterrupt Fla  | ag bit     |                          |              |               |       |

|               |            | register has<br>register did  |               |            | eared in softwa          | are)         |               |       |

| bit 1         | INTF: RB0  | /INT Externa                  | al Interrupt  | Flag bit   |                          |              |               |       |

|               |            | 30/INT exter<br>30/INT exter  |               | •          | must be cleare           | d in softwaı | e)            |       |

| bit 0         | RBIF: RB I | Port Change                   | Interrupt F   | lag bit    |                          |              |               |       |

|               |            | at least one<br>of the RB7:R  |               |            | nanged state (n<br>state | nust be clea | ared in softw | vare) |

|               | Levendu    |                               |               |            |                          |              |               | 1     |

| Legend:           |                  |                      |                                    |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | J = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

## 5.3 I/O Programming Considerations

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on Bit 5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on Bit 5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., Bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if Bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading a port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings:PORTB<7:4> Inputs

;

;

; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-up and are not ;connected to other circuitry ;

| BCF STATUS, RPO ;                                                                                              |                                                 | PORT latchPORT Pins |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|

| BCF PORTB, /;01pp pppp 11pp pppBSF STATUS, RP0;BCF TRISB, 7;10pp pppp 11pp pppBCF TRISB, 6;10pp pppp 10pp pppp | BCF PORTB, 7<br>BSF STATUS, RP0<br>BCF TRISB, 7 |                     |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

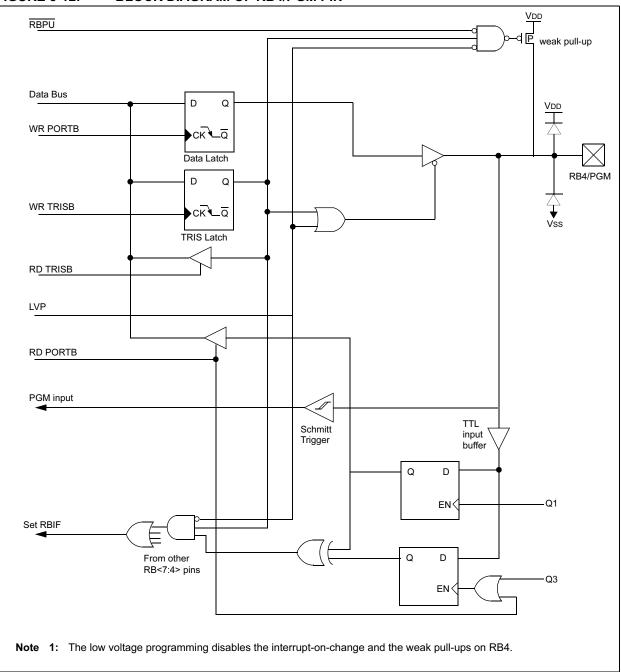

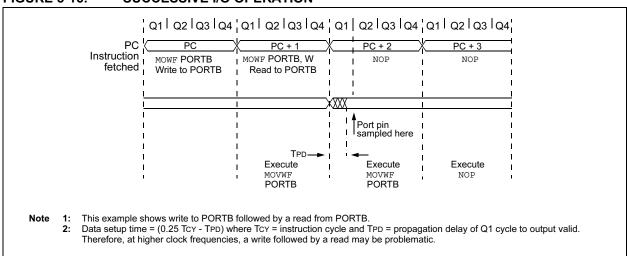

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-16). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-16: SUCCESSIVE I/O OPERATION

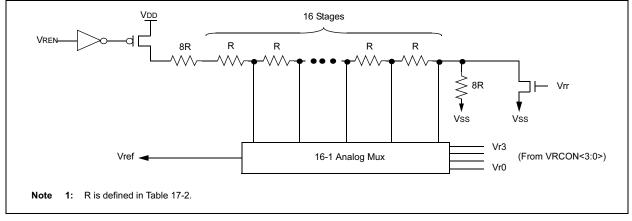

## 10.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 10-1. The block diagram is given in Figure 10-1.

## 10.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

voltage of 1.25V with VDD = 5.0V.

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 17-2). Example 10-1 shows an example of how to configure the Voltage Reference for an output

| REGISTER 10-1: | VRCON R                   | EGISTER                      | (ADDRES   | S: 9Fh)                                      |       |       |       |       |

|----------------|---------------------------|------------------------------|-----------|----------------------------------------------|-------|-------|-------|-------|

|                | R/W-0                     | R/W-0                        | R/W-0     | U-0                                          | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                | VREN                      | Vroe                         | Vrr       | _                                            | VR3   | VR2   | VR1   | VR0   |

|                | bit 7                     |                              |           |                                              |       |       |       | bit   |

| bit 7          | VREN: VREF                | Enable                       |           |                                              |       |       |       |       |

|                |                           | rcuit powere<br>rcuit powere |           | o Idd drain                                  |       |       |       |       |

| bit 6          | VROE: VRE                 | - Output En                  | able      |                                              |       |       |       |       |

|                |                           | output on F<br>disconnect    |           | 2 pin                                        |       |       |       |       |

| bit 5          | VRR: VREF                 | Range sele                   | ction     |                                              |       |       |       |       |

|                | 1 = Low Ra<br>0 = High Ra | 0                            |           |                                              |       |       |       |       |

| bit 4          | Unimplem                  | ented: Rea                   | d as '0'  |                                              |       |       |       |       |

| bit 3-0        | When VRR                  | = 1: Vref =                  | (VR<3:0>/ | ≦ VR [3:0] ≤ 1<br>24) * VDD<br>⊦ (VR<3:0>/ 3 |       |       |       |       |

| Legend:           |                  |                      |                    |  |  |

|-------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | d bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

## FIGURE 10-1: VOLTAGE REFERENCE BLOCK DIAGRAM

## 12.0 UNIVERSAL SYNCHRONOUS/ ASYNCHRONOUS RECEIVER/ TRANSMITTER (USART) MODULE

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/ A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISB<2:1>, have to be set in order to configure pins RB2/TX/CK and RB1/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

## REGISTER 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

|       | R/W-0                                               | R/W-0                                                                                                 | R/W-0                         | R/W-0           | U-0          | <b>R</b> /W-0 | R-1            | ,<br>R/W-0 |  |  |  |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|--------------|---------------|----------------|------------|--|--|--|

|       | CSRC                                                | TX9                                                                                                   | TXEN                          | SYNC            | —            | BRGH          | TRMT           | TX9D       |  |  |  |

|       | bit 7                                               |                                                                                                       |                               |                 |              |               |                | bit 0      |  |  |  |

| bit 7 | CSRC: Cloc                                          | k Source Sel                                                                                          | ect bit                       |                 |              |               |                |            |  |  |  |

|       | Asynchronou<br>Don't car                            |                                                                                                       |                               |                 |              |               |                |            |  |  |  |

|       |                                                     | er mode (Clo                                                                                          | ck generated<br>k from extern | internally from | m BRG)       |               |                |            |  |  |  |

| bit 6 | 1 = Selects 9                                       | <b>(9</b> : 9-bit Transmit Enable bit<br>= Selects 9-bit transmission<br>= Selects 8-bit transmission |                               |                 |              |               |                |            |  |  |  |

| bit 5 | <b>TXEN</b> : Trans<br>1 = Transmit<br>0 = Transmit |                                                                                                       | <sub>oit</sub> (1)            |                 |              |               |                |            |  |  |  |

| bit 4 | SYNC: USA<br>1 = Synchro<br>0 = Asynchro            |                                                                                                       | ect bit                       |                 |              |               |                |            |  |  |  |

| bit 3 | Unimpleme                                           | nted: Read a                                                                                          | is '0'                        |                 |              |               |                |            |  |  |  |

| bit 2 | BRGH: High                                          | Baud Rate S                                                                                           | Select bit                    |                 |              |               |                |            |  |  |  |

|       | Asynchronou<br>1 = High s<br>0 = Low s              | speed                                                                                                 |                               |                 |              |               |                |            |  |  |  |

|       | <u>Synchronou</u>                                   | •                                                                                                     |                               |                 |              |               |                |            |  |  |  |

| bit 1 | <b>TRMT</b> : Trans<br>1 = TSR em<br>0 = TSR full   |                                                                                                       | gister STATU                  | S bit           |              |               |                |            |  |  |  |

| bit 0 | <b>TX9D</b> : 9th bi                                | t of transmit                                                                                         | data. Can be                  | PARITY bit.     |              |               |                |            |  |  |  |

|       | Note 1: S                                           | REN/CREN                                                                                              | overrides TX                  | EN in SYNC      | node.        |               |                |            |  |  |  |

|       | Legend:                                             |                                                                                                       |                               |                 |              |               |                |            |  |  |  |

|       | R = Reada                                           | ble bit                                                                                               | VV = V                        | Vritable bit    | U = Unimp    | lemented b    | oit, read as ' | )'         |  |  |  |

|       | -n = Value                                          | at POR                                                                                                | '1' = E                       | Bit is set      | '0' = Bit is | cleared       | x = Bit is ur  | nknown     |  |  |  |

| BAUD     | Fosc = 20 M | Hz     |                    | 16 MHz |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|-------------|--------|--------------------|--------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _      | _                  | NA     | _      |                    | NA     | _      | _                  |

| 1.2      | 1.221       | +1.73% | 255                | 1.202  | +0.16% | 207                | 1.202  | +0.16% | 129                |

| 2.4      | 2.404       | +0.16% | 129                | 2.404  | +0.16% | 103                | 2.404  | +0.16% | 64                 |

| 9.6      | 9.469       | -1.36% | 32                 | 9.615  | +0.16% | 25                 | 9.766  | +1.73% | 15                 |

| 19.2     | 19.53       | +1.73% | 15                 | 19.23  | +0.16% | 12                 | 19.53  | +1.73V | 7                  |

| 76.8     | 78.13       | +1.73% | 3                  | 83.33  | +8.51% | 2                  | 78.13  | +1.73% | 1                  |

| 96       | 104.2       | +8.51% | 2                  | NA     | _      | _                  | NA     | _      | _                  |

| 300      | 312.5       | +4.17% | 0                  | NA     | _      | _                  | NA     | _      | _                  |

| 500      | NA          | _      | _                  | NA     | _      | _                  | NA     | _      | _                  |

| HIGH     | 312.5       | _      | 0                  | 250    | _      | 0                  | 156.3  | _      | 0                  |

| LOW      | 1.221       | —      | 255                | 0.977  |        | 255                | 0.6104 |        | 255                |

| TABLE 12-4: | BAUD RATES FOR ASYNCHRONOUS MODE ( | BRGH=0) |

|-------------|------------------------------------|---------|

|-------------|------------------------------------|---------|

| BAUD     | Fosc = 7.15 | 909 MHz | SPBRG              | 5.0688 MHz |        | SPBRG              | 4 MHz  |        | SPBRG              |

|----------|-------------|---------|--------------------|------------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD       | ERROR   | value<br>(decimal) | KBAUD      | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 0.3      | NA          | _       | _                  | 0.31       | +3.13% | 255                | 0.3005 | -0.17% | 207                |

| 1.2      | 1.203       | +0.23%  | 92                 | 1.2        | 0      | 65                 | 1.202  | +1.67% | 51                 |

| 2.4      | 2.380       | -0.83%  | 46                 | 2.4        | 0      | 32                 | 2.404  | +1.67% | 25                 |

| 9.6      | 9.322       | -2.90%  | 11                 | 9.9        | +3.13% | 7                  | NA     | _      | _                  |

| 19.2     | 18.64       | -2.90%  | 5                  | 19.8       | +3.13% | 3                  | NA     | _      | _                  |

| 76.8     | NA          | _       | _                  | 79.2       | +3.13% | 0                  | NA     | _      | _                  |

| 96       | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 300      | NA          | _       | _                  | NA         | _      | _                  | NA     | _      | _                  |

| 500      | NA          |         | _                  | NA         | _      | _                  | NA     | _      | _                  |

| HIGH     | 111.9       | _       | 0                  | 79.2       | _      | 0                  | 62.500 | _      | 0                  |

| LOW      | 0.437       | _       | 255                | 0.3094     |        | 255                | 3.906  |        | 255                |

| BAUD        | Fosc = 3.579 | 9545 MHz | SPBRG              | 1 MHz  |        | SPBRG              | 32.768 MHz |         | SPBRG              |

|-------------|--------------|----------|--------------------|--------|--------|--------------------|------------|---------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) | KBAUD      | ERROR   | value<br>(decimal) |

| 0.3         | 0.301        | +0.23%   | 185                | 0.300  | +0.16% | 51                 | 0.256      | -14.67% | 1                  |

| 1.2         | 1.190        | -0.83%   | 46                 | 1.202  | +0.16% | 12                 | NA         | _       | _                  |

| 2.4         | 2.432        | +1.32%   | 22                 | 2.232  | -6.99% | 6                  | NA         | _       | _                  |

| 9.6         | 9.322        | -2.90%   | 5                  | NA     | _      | _                  | NA         | _       | _                  |

| 19.2        | 18.64        | -2.90%   | 2                  | NA     | _      | _                  | NA         | _       | _                  |

| 76.8        | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 96          | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 300         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| 500         | NA           | _        | _                  | NA     | _      | _                  | NA         | _       | _                  |

| HIGH        | 55.93        | _        | 0                  | 15.63  | _      | 0                  | 0.512      | _       | 0                  |

| LOW         | 0.2185       | _        | 255                | 0.0610 | _      | 255                | 0.0020     | _       | 255                |

| BAUD     | Fosc = 20 MHz |        | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|---------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD ERRO    |        | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615         | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230        | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878        | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818        | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636       | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250           | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625           | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250          | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     |         |        | 5.068 MHz          |          | SPBRG   | 4 MHz              |          | SPBRG   |                    |

|----------|---------|--------|--------------------|----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520   | -0.83% | 46                 | 9598.485 | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454  | +1.32% | 22                 | 18632.35 | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286  | -2.90% | 11                 | 39593.75 | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930  | -2.90% | 7                  | 52791.67 | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860 | -2.90% | 3                  | 105583.3 | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA      | _      | _                  | 316750   | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA      | _      | _                  | NA       | _       | _                  | NA       | _       | _                  |

| 1250000  | NA      |        | —                  | NA       | —       | _                  | NA       | —       |                    |

| BAUD        | Fosc = 3.579 | 9 MHz    | SPBRG              | 1 MHz   |          | SPBRG              | 32.768 MHz |       | SPBRG              |

|-------------|--------------|----------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600        | 9725.543     | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200       | 18640.63     | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400       | 37281.25     | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600       | 55921.88     | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200      | 111243.8     | -2.913%  | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000      | 223687.5     | -10.525% | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000      | NA           | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000     | NA           | —        | —                  | NA      | —        | —                  | NA         | NA    | NA                 |

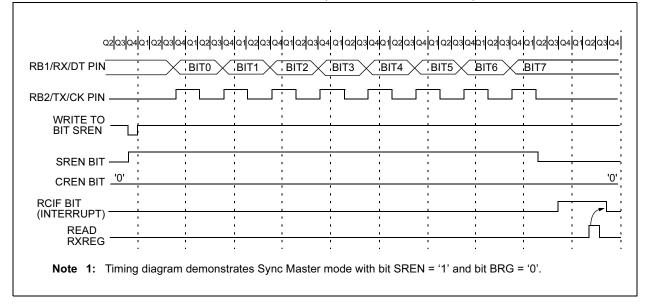

## FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

## **REGISTER 14-1: CONFIGURATION WORD**

| CP1                         | CP0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CP1                                                                                                       | CP0                                                                                                                                                    | _                                                                                                           | CPD                                       | LVP                                     | BODEN                                | MCLRE                                       | FOSC2                                      | PWRTE                 | WDTE | F0SC1 | F0SC0 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|--------------------------------------|---------------------------------------------|--------------------------------------------|-----------------------|------|-------|-------|

| bit 13                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           | ·                                                                                                                                                      |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       | bit 0 |

| bit 13-10:                  | Code<br>11 =<br>01 =<br>00 =<br>Code<br>11 =<br>10 =<br>01 =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | protection<br>Program<br>0400h-07<br>0200h-07<br>0000h-07<br>protection<br>Program<br>Program<br>0200h-03 | le Protection<br>n for 2K prog<br>memory cod<br>7FFh code p<br>7FFh code p<br>7FFh code p<br>n for 1K prog<br>memory cod<br>3FFh code p<br>3FFh code p | gram memore<br>rotected<br>rotected<br>otected<br>gram memore<br>de protection<br>de protection<br>rotected | on off<br>ory<br>on off                   |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 9:                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           | ed: Read as                                                                                                                                            |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 8:                      | <b>CPD:</b><br>1 = Da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Coo<br>ata memo                                                                                      | de Protection<br>bry code pro<br>bry code pro                                                                                                          | n bit <sup>(3)</sup><br>tection off                                                                         |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 7:                      | 1 = R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | B4/PGM                                                                                                    | age Program<br>pin has PGN<br>is digital I/O,                                                                                                          | 1 function,                                                                                                 | ow voltage                                |                                         | •                                    |                                             |                                            |                       |      |       |       |

| bit 6:                      | 1 = B(                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OD Rese                                                                                                   | n-out Detect<br>t enabled<br>t disabled                                                                                                                | Reset Ena                                                                                                   | ble bit <sup>(1)</sup>                    |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 5:                      | 1 = R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A5/MCLF                                                                                                   | MCLR pin fu<br>pin functior<br>pin functior                                                                                                            | is MCLR                                                                                                     |                                           | R internally                            | tied to VDD                          | )                                           |                                            |                       |      |       |       |

| bit 3:                      | 1 = P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>TEN</b> : Pow<br>WRT disa<br>WRT ena                                                                   |                                                                                                                                                        | Enable bit                                                                                                  | (1)                                       |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 2:                      | 1 = W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>EN</b> : Watcl<br>DT enab                                                                              |                                                                                                                                                        | Enable bit                                                                                                  |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

| bit 4, 1-0:                 | FOSC2:FOSC0: Oscillator Selection bits <sup>(4)</sup><br>111 = ER oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, Resistor on RA7/OSC1/CLKIN<br>110 = ER oscillator: I/O function on RA6/OSC2/CLKOUT pin, Resistor on RA7/OSC1/CLKIN<br>101 = INTRC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>100 = INTRC oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN<br>101 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN<br>102 = HS oscillator: High speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>103 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>104 = KD oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN<br>105 = KD oscillator: Low power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN |                                                                                                           |                                                                                                                                                        |                                                                                                             |                                           |                                         |                                      |                                             |                                            |                       |      |       |       |

|                             | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Er<br>2: Al<br>3: Th                                                                                      | nabling Brow<br>nsure the Po<br>I of the CP1:<br>ne entire data<br>hen MCLR i                                                                          | wer-up Tim<br>CP0 pairs<br>a EEPROM                                                                         | er is enab<br>have to be<br>I will be era | led anytime<br>given the s<br>ased when | Brown-ou<br>same value<br>the code p | t Detect Re<br>to enable to<br>rotection is | eset is enab<br>the code pr<br>turned off. | oled.<br>rotection sc |      |       | WRTE. |

| <b>Legend</b><br>R = Readat |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |                                                                                                                                                        |                                                                                                             | itable bit                                |                                         |                                      |                                             | ited bit, rea                              |                       |      |       |       |

| R = Readable bit W = Writable bit |                | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|----------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | 1 = bit is set | 0 = bit is cleared                 | x = bit is unknown |  |  |  |

-

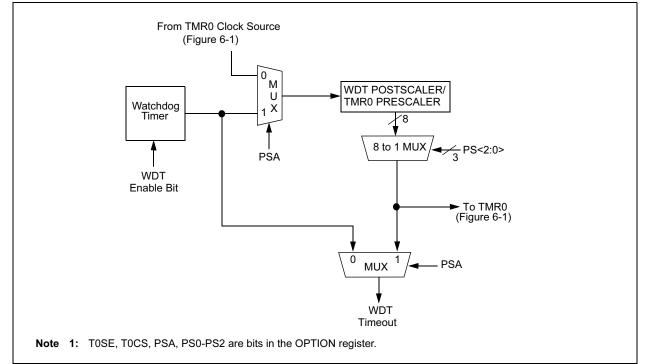

#### FIGURE 14-16: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-10: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name            | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR Reset | Value on all<br>other<br>RESETS |

|---------|-----------------|-------|--------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 2007h   | Config.<br>bits | LVP   | BODEN  | MCLRE | FOSC2 | PWRTE | WDTE  | FOSC1 | FOSC0 | uuuu uuuu             | uuuu uuuu                       |

| 81h     | OPTION          | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111             | 1111 1111                       |

Legend: -= Unimplemented location, read as "0", + = Reserved for future use

**Note 1:** Shaded cells are not used by the Watchdog Timer.

#### 14.9 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators, and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | by a WDT timeout does not drive MCLR      |  |  |  |  |  |  |

|       | pin low.                                  |  |  |  |  |  |  |

#### 14.9.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up is cleared when SLEEP is invoked. TO bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the

corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

**Note:** If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes-up from SLEEP, regardless of the source of wake-up.

#### FIGURE 14-17: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                                                                         |                              | Q1  Q2  Q3  Q4;    | Q1  Q2  Q3  Q4; (   | Q1  Q2  Q3  Q4;     |

|-----------------------------------------------------------------------------------------|------------------------------|--------------------|---------------------|---------------------|

|                                                                                         |                              |                    |                     |                     |

|                                                                                         | <u>it</u> / /                |                    |                     | / i                 |

| INT pin                                                                                 | · · ·                        | I                  |                     | I                   |

|                                                                                         | Interrupt Latenc             | :V                 |                     |                     |

|                                                                                         | (Note 2)                     | <u>,</u>           | <b>→</b>            |                     |

| GIE bit<br>(INTCON<7>) Processor in                                                     | I I                          | <u>'</u>           | <u> </u>            | !                   |

| SLEEP                                                                                   |                              |                    | i                   |                     |

| INSTRUCTION FLOW                                                                        |                              | 1                  | 1                   | 1                   |

| PC X PC X PC+1 X PC+2                                                                   | X PC+2                       | PC + 2             | <u>(0004h X</u>     | 0005h               |

| Instruction { Inst(PC) = SLEEP Inst(PC + 1)                                             | Inst(PC + 2)                 | 1<br>1<br>1        | Inst(0004h)         | Inst(0005h)         |

| Instruction { Inst(PC - 1) SLEEP                                                        | Inst(PC + 1)                 | Dummy cycle        | Dummy cycle         | Inst(0004h)         |

| Note 1: XT, HS or LP Oscillator mode assumed.                                           |                              |                    |                     |                     |

| 2: TOST = 1024TOSC (drawing not to scale). Approximation                                | tely 1 $\mu$ s delay will be | there for ER Os    | c mode.             |                     |

| <ol> <li>GIE = '1' assumed. In this case after wake- up, the pr<br/>in-line.</li> </ol> | rocessor jumps to the        | interrupt routine. | If GIE = '0', execu | ution will continue |

| 4: CLKOUT is not available in these Osc modes, but sl                                   | hown here for timing r       | eference.          |                     |                     |

## 14.10 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and FLASH program memory will be erased when the code protection is turned off. The INTRC calibration data is not erased.

## 14.11 User ID Locations

Four memory locations (2000h-2003h) are designated as user ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the Least Significant 4 bits of the user ID locations are used.

| RETLW            | Return with Literal in W                                                                                                                                                               | RLF              | Rotate Left f through Carry                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                               | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                              |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                           | Operation:       | $d \in [0,1]$<br>See description below                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                   | Status Affected: | С                                                                                                                                                                                                              |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                      | Encoding:        | 00 1101 dfff ffff                                                                                                                                                                                              |

| Description:     | The W register is loaded with<br>the eight bit literal 'k'. The<br>program counter is loaded from<br>the top of the stack (the return<br>address). This is a two-cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0 the result<br>is placed in the W register. If 'd' is<br>1 the result is stored back in<br>register 'f'. |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      | Words:           | 1                                                                                                                                                                                                              |

| Example          | CALL TABLE;W contains table                                                                                                                                                            | Cycles:          | 1                                                                                                                                                                                                              |

|                  | <ul> <li>;offset value</li> <li>;W now has table</li> </ul>                                                                                                                            | -                |                                                                                                                                                                                                                |

|                  | value                                                                                                                                                                                  | Example          | RLF REG1, 0<br>Before Instruction                                                                                                                                                                              |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8             |                  | REG1 = 1110 0110 $C = 0$ After Instruction $REG1 = 1110 0110$ $W = 1100 1100$ $C = 1$                                                                                                                          |

| RETURN           | Return from Subroutine                                                                                                                                                                 |                  |                                                                                                                                                                                                                |

| Syntax:          | [label] RETURN                                                                                                                                                                         |                  |                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                   |                  |                                                                                                                                                                                                                |

| Encoding:        | 00 0000 0000 1000                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Description:     | Return from subroutine. The<br>stack is POPed and the top of<br>the stack (TOS) is loaded into<br>the program counter. This is a<br>two-cycle instruction.                             |                  |                                                                                                                                                                                                                |

| Words:           | 1                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                      |                  |                                                                                                                                                                                                                |