Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 224 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628at-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, KEELOQ, MPLAB, PIC, PICmicro, PICSTART and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

dsPIC, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## 1.0 PIC16F62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16F62X Product Identification System section (Page 167) at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 1.1 FLASH Devices

FLASH devices can be erased and reprogrammed electrically. This allows the same device to be used for prototype development, pilot programs and production.

A further advantage of the electrically-erasable FLASH is that it can be erased and reprogrammed in-circuit, or by device programmers, such as Microchip's PICSTART<sup>®</sup> Plus, or PRO MATE<sup>®</sup> II programmers.

## 1.2 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are standard FLASH devices but with all program locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 1.3 Serialized Quick-Turnaround Production (SQTP<sup>sm</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

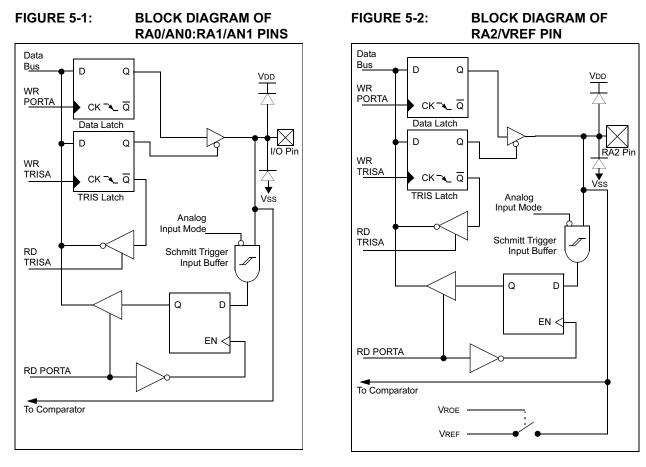

#### FIGURE 5-3: BLOCK DIAGRAM OF THE RA3/AN3 PIN

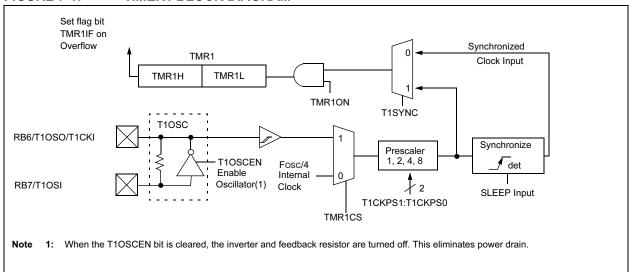

## 7.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

#### 7.2 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RB7/T1OSI when bit T1OSCEN is set or pin RB6/T1OSO/T1CKI when bit T1OSCEN is cleared.

If TISYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 7.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in Synchronized Counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifications, parameters 40, 42, 45, 46, and 47.

#### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

© 2003 Microchip Technology Inc.

## 7.4 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq    | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

**Note 1:** These values are for design guidance only. Consult AN826 (DS00826A) for further information on Crystal/Capacitor Selection.

## 7.5 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The spe | cial e | event | trigg | ers from tl | he CC | CP1 |

|-------|---------|--------|-------|-------|-------------|-------|-----|

|       | module  | will   | not   | set   | interrupt   | flag  | bit |

|       | TMR1IF  | (PIR   | 1<0>  | ).    |             |       |     |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

## 7.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR or any other RESET except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

## 7.7 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

#### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7      | Bit 6       | Bit 5         | Bit 4          | Bit 3           | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>RESETS |

|-----------------------|--------|------------|-------------|---------------|----------------|-----------------|-------------|--------|--------|-----------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON | GIE        | PEIE        | TOIE          | INTE           | RBIE            | T0IF        | INTF   | RBIF   | 0000 000x       | 0000 000u                       |

| 0Ch                   | PIR1   | EEIF       | CMIF        | RCIF          | TXIF           | l               | CCP1IF      | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 8Ch                   | PIE1   | EEIE       | CMIE        | RCIE          | TXIE           | l               | CCP1IE      | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 0Eh                   | TMR1L  | Holding re | egister for | the Least Sig | gnificant Byte | of the 16-bit   | TMR1 regist | er     |        | xxxx xxxx       | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding re | gister for  | the Most Sig  | nificant Byte  | of the 16-bit T | MR1 registe | er     |        | xxxx xxxx       | uuuu uuuu                       |

| 10h                   | T1CON  | _          | _           | T1CKPS1       | T1CKPS0        | T1OSCEN         | T1SYNC      | TMR1CS | TMR10N | 00 0000         | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

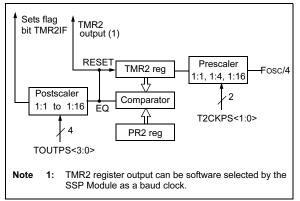

## 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit Period Register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- · A write to the TMR2 register

- · A write to the T2CON register

- Any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

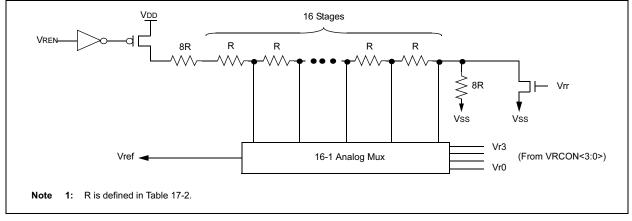

## 10.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Figure 10-1. The block diagram is given in Figure 10-1.

## 10.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

voltage of 1.25V with VDD = 5.0V.

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 17-2). Example 10-1 shows an example of how to configure the Voltage Reference for an output

| REGISTER 10-1: | VRCON R                                                                | EGISTER                                                                    | (ADDRES   | S: 9Fh)                                      |       |       |       |       |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------|----------------------------------------------|-------|-------|-------|-------|--|--|--|

|                | R/W-0                                                                  | R/W-0                                                                      | R/W-0     | U-0                                          | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                | VREN                                                                   | Vroe                                                                       | Vrr       | _                                            | VR3   | VR2   | VR1   | VR0   |  |  |  |

|                | bit 7                                                                  |                                                                            |           |                                              |       |       |       | bit   |  |  |  |

| bit 7          | VREN: VREF                                                             | Enable                                                                     |           |                                              |       |       |       |       |  |  |  |

|                |                                                                        | 1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain |           |                                              |       |       |       |       |  |  |  |

| bit 6          | VROE: VREF Output Enable                                               |                                                                            |           |                                              |       |       |       |       |  |  |  |

|                | 1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |                                                                            |           |                                              |       |       |       |       |  |  |  |

| bit 5          | VRR: VREF Range selection                                              |                                                                            |           |                                              |       |       |       |       |  |  |  |

|                | 1 = Low Ra<br>0 = High Ra                                              | 0                                                                          |           |                                              |       |       |       |       |  |  |  |

| bit 4          | Unimplem                                                               | ented: Rea                                                                 | d as '0'  |                                              |       |       |       |       |  |  |  |

| bit 3-0        | When VRR                                                               | = 1: Vref =                                                                | (VR<3:0>/ | ≦ VR [3:0] ≤ 1<br>24) * VDD<br>⊦ (VR<3:0>/ 3 |       |       |       |       |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### FIGURE 10-1: VOLTAGE REFERENCE BLOCK DIAGRAM

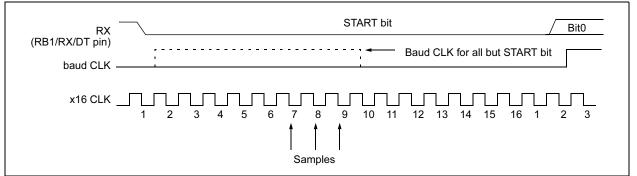

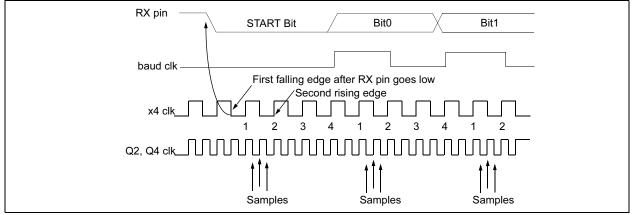

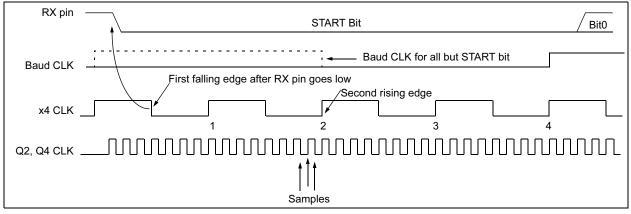

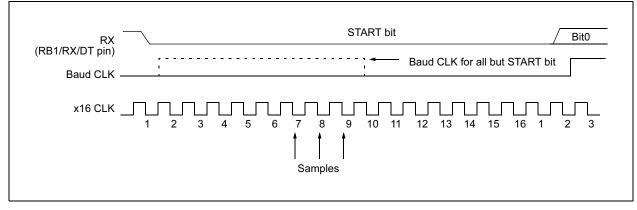

The data on the RB1/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

#### FIGURE 12-1: RX PIN SAMPLING SCHEME. BRGH = 0

## FIGURE 12-2: RX PIN SAMPLING SCHEME, BRGH = 1

#### FIGURE 12-3: RX PIN SAMPLING SCHEME, BRGH = 1

#### 12.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return to zero (NRZ) format (one START bit, eight or nine data bits and one STOP bit). The most common data format is 8 bits. A dedicated 8-bit baud rate generator is used to derive baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

#### 12.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 12-5. The heart of the transmitter is the transmitt (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in

software. It will RESET only when new data is loaded into the TXREG register. While flag bit TXIF indicated the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. STATUS bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 12-5). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 12-7). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will RESET the transmitter. As a result the RB2/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

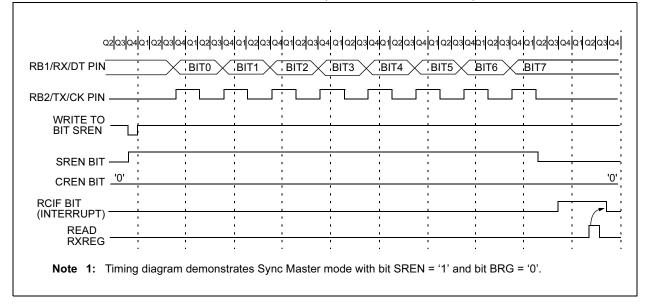

#### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.5.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in Slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

1. Enable the synchronous master serial port by

setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

| Address | Name                               | Bit 7    | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|------------------------------------|----------|-----------|----------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF     | CMIF      | RCIF     | TXIF  |       | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN     | RX9       | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 -00x       | 0000 -00x                       |

| 19h     | TXREG                              | USART TI | ransmit I | Register |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE     | CMIE      | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC     | TX9       | TXEN     | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |          |           |          |       |       |        |        |        | 0000 0000       | 0000 0000                       |

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

#### TABLE 12-12: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name                               | Bit 7   | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on all<br>other<br>RESETS |

|---------|------------------------------------|---------|----------|----------|-------|-------|--------|--------|--------|-----------------|---------------------------------|

| 0Ch     | PIR1                               | EEIF    | CMIF     | RCIF     | TXIF  | _     | CCP1IF | TMR2IF | TMR1IF | 0000 -000       | 0000 -000                       |

| 18h     | RCSTA                              | SPEN    | RX9      | SREN     | CREN  | ADEN  | FERR   | OERR   | RX9D   | 0000 -00x       | 0000 -00x                       |

| 1Ah     | RCREG                              | USART R | eceive F | Register |       |       |        |        |        | 0000 0000       | 0000 0000                       |

| 8Ch     | PIE1                               | EEIE    | CMIE     | RCIE     | TXIE  | _     | CCP1IE | TMR2IE | TMR1IE | 0000 -000       | 0000 -000                       |

| 98h     | TXSTA                              | CSRC    | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010       | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |         |          |          |       |       |        |        |        | 0000 0000       | 0000 0000                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

## 14.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real-time applications are what sets a microcontroller apart from other processors. The PIC16F62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Brown-out Reset (BOD)

- 7. Interrupts

- 8. Watchdog Timer (WDT)

- 9. SLEEP

- 10. Code protection

- 11. ID Locations

- 12. In-circuit Serial Programming

The PIC16F62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to RESET the device if a Brown-out occurs, which provides at least a 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The ER oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special configuration memory space (2000h – 3FFFh), which can be accessed only during programming. See Programming Specification.

# FIGURE 14-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- **2:**  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3: R1 =  $100\Omega$  to  $1 k\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

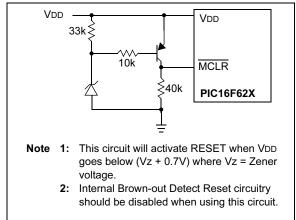

#### FIGURE 14-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

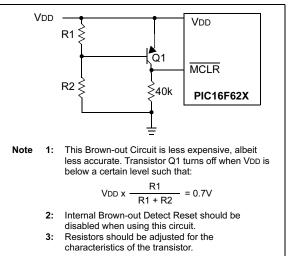

#### FIGURE 14-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

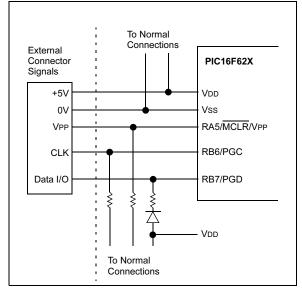

## 14.12 In-Circuit Serial Programming

The PIC16F62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 14-18.

#### FIGURE 14-18: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 14.13 Low Voltage Programming

The LVP bit of the configuration word, enables the low voltage programming. This mode allows the microcontroller to be programmed via ICSP using only a 5V source. This mode removes the requirement of VIHH to be placed on the MCLR pin. The LVP bit is normally erased to '1', which enables the low voltage programming. In this mode, the RB4/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. The device will enter Programming mode when a '1' is placed on the RB4/PGM pin. The HV Programming mode is still available by placing VIHH on the MCLR pin.

- Note 1: While in this mode, the RB4 pin can no longer be used as a general purpose I/O pin.

- 2: VDD must be 5.0V <u>+</u>10% during erase/ program operations while in low voltage Programming mode.

If Low voltage Programming mode is not used, the LVP bit can be programmed to a '0', and RB4/PGM becomes a digital I/O pin. To program the device, VIHH must be placed onto MCLR during programming. The LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit cannot be programmed when programming is entered with RB4/PGM.

It should be noted, that once the LVP bit is programmed to 0, High voltage Programming mode can be used to program the device.

## PIC16F62X

| RRF              | Rotate                                                                                                                                                                                                          | Right f t | hrough ( | Carry |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                       | RRF       | f,d      |       |  |  |

| Operands:        | 0 ≤ f ≤ 1<br>d ∈ [0,1                                                                                                                                                                                           |           |          |       |  |  |

| Operation:       | See des                                                                                                                                                                                                         | scription | below    |       |  |  |

| Status Affected: | С                                                                                                                                                                                                               |           |          |       |  |  |

| Encoding:        | 00                                                                                                                                                                                                              | 1100      | dfff     | ffff  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right<br>through the Carry Flag. If 'd' is 0<br>the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in register 'f'. |           |          |       |  |  |

|                  |                                                                                                                                                                                                                 |           | GISTER   |       |  |  |

| Words:           | 1                                                                                                                                                                                                               |           |          |       |  |  |

| Tronao.          |                                                                                                                                                                                                                 |           |          |       |  |  |

| Cycles:          | 1                                                                                                                                                                                                               |           |          |       |  |  |

|                  | <b>1</b><br>rrf                                                                                                                                                                                                 | REG1,     | 0        |       |  |  |

#### SLEEP

| •===:                                                                                                                                                                                                                                                               |                                                                                                                                       |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                             | [label] SLEEP                                                                                                                         |  |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                           | None                                                                                                                                  |  |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                          | $00h \rightarrow WDT,$<br>$0 \rightarrow \underline{W}DT \text{ prescaler,}$<br>$1 \rightarrow \underline{TO},$<br>$0 \rightarrow PD$ |  |  |  |  |  |

| Status Affected: TO, PD                                                                                                                                                                                                                                             |                                                                                                                                       |  |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                           | 00 0000 0110 0011                                                                                                                     |  |  |  |  |  |

| Description:<br>The power-down STATUS bit,<br>PD is cleared. Timeout<br>STATUS bit, TO is set.<br>Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into<br>SLEEP mode with the<br>oscillator stopped. See<br>Section 14.9 for more details. |                                                                                                                                       |  |  |  |  |  |

| Words:                                                                                                                                                                                                                                                              | 1                                                                                                                                     |  |  |  |  |  |

| Cycles:                                                                                                                                                                                                                                                             | 1                                                                                                                                     |  |  |  |  |  |

| Example:                                                                                                                                                                                                                                                            | SLEEP                                                                                                                                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                     |                                                                                                                                       |  |  |  |  |  |

| SUBLW               | Subtract W from Literal                                                                                                      |  |  |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |  |  |

| Operands:           | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |  |  |

| Operation:          | $k - (W) \rightarrow (W)$                                                                                                    |  |  |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |  |  |

| Encoding:           | 11 110x kkkk kkkk                                                                                                            |  |  |  |  |  |  |  |

| Description:        | The W register is subtracted (2's complement method) from the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |  |

| Words:              | 1                                                                                                                            |  |  |  |  |  |  |  |

| Cycles:             | 1                                                                                                                            |  |  |  |  |  |  |  |

| Example 1:          | SUBLW 0x02                                                                                                                   |  |  |  |  |  |  |  |

|                     | Before Instruction                                                                                                           |  |  |  |  |  |  |  |

|                     | W = 1<br>C = ?                                                                                                               |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                            |  |  |  |  |  |  |  |

|                     | W = 1<br>C = 1; result is positive                                                                                           |  |  |  |  |  |  |  |

| Example 2:          | Before Instruction                                                                                                           |  |  |  |  |  |  |  |

|                     | W = 2<br>C = ?                                                                                                               |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                            |  |  |  |  |  |  |  |

|                     | W = 0<br>C = 1; result is zero                                                                                               |  |  |  |  |  |  |  |

| Example 3:          | Before Instruction                                                                                                           |  |  |  |  |  |  |  |

|                     | W = 3<br>C = ?                                                                                                               |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                            |  |  |  |  |  |  |  |

|                     | W = 0xFF<br>C = 0; result is negative                                                                                        |  |  |  |  |  |  |  |

| Param<br>No. | Sym       |                                         | Characteristic                      |                | Min                                 | Тур† | Max                                | Units | Conditions                         |

|--------------|-----------|-----------------------------------------|-------------------------------------|----------------|-------------------------------------|------|------------------------------------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Puls                         | e Width                             | No Prescaler   | 0.5Tcy + 20                         | —    |                                    | ns    |                                    |

|              |           |                                         |                                     | With Prescaler | 10                                  | —    | _                                  | ns    |                                    |

| 41*          | TtOL      | T0CKI Low Pulse                         | e Width                             | No Prescaler   | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |           |                                         |                                     | With Prescaler | 10                                  | -    | —                                  | ns    |                                    |

| 42*          | Tt0P      | T0CKI Period                            | Greater of:<br><u>Tcy + 40</u><br>N | _              | —                                   | ns   | N = prescale value<br>(2, 4,, 256) |       |                                    |

| 45*          | Tt1H      | T1CKI High                              | Synchronous, N                      | lo Prescaler   | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |           | Time                                    | Synchronous,                        | 16F62X         | 15                                  | -    | —                                  | ns    |                                    |

|              |           | with Prescaler                          | 16LF62X                             | 25             | —                                   | —    | ns                                 |       |                                    |

|              |           | Asynchronous                            | 16F62X                              | 30             | _                                   | -    | ns                                 |       |                                    |

|              |           |                                         |                                     | 16LF62X        | 50                                  | —    | _                                  | ns    |                                    |

| 46* Tt1L     | Tt1L      | T1CKI Low Time                          | Synchronous, N                      | lo Prescaler   | 0.5Tcy + 20                         | —    | —                                  | ns    |                                    |

|              |           |                                         | Synchronous,                        | 16F62X         | 15                                  | —    | —                                  | ns    |                                    |

|              |           |                                         | with Prescaler                      | 16LF62X        | 25                                  | —    | —                                  | ns    |                                    |

|              |           |                                         | Asynchronous                        | 16F62X         | 30                                  | -    | Ι                                  | ns    |                                    |

|              |           |                                         |                                     | 16LF62X        | 50                                  | —    | —                                  | ns    |                                    |

| 47*          | Tt1P      | T1CKI input<br>period                   | Synchronous                         | 16F62X         | Greater of:<br><u>Tcy + 40</u><br>N | —    | —                                  | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                         |                                     | 16LF62X        | Greater of:<br><u>Tcy + 40</u><br>N | _    | —                                  | —     |                                    |

|              |           |                                         | Asynchronous                        | 16F62X         | 60                                  | _    | -                                  | ns    |                                    |

|              |           |                                         |                                     | 16LF62X        | 100                                 | —    | —                                  | ns    |                                    |

|              | Ft1       | Timer1 oscillator<br>(oscillator enable |                                     |                | DC                                  | -    | 200                                | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from exter<br>increment           | nal clock edge to                   | o timer        | 2Tosc                               | -    | 7Tosc                              | _     |                                    |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

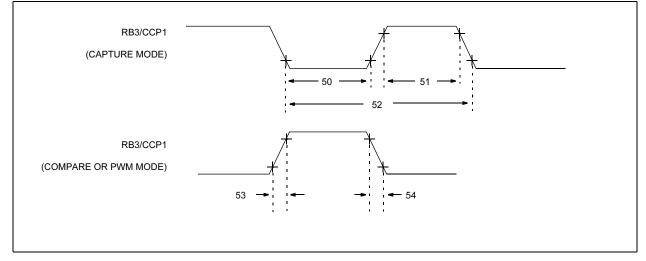

#### FIGURE 17-11: **CAPTURE/COMPARE/PWM TIMINGS**

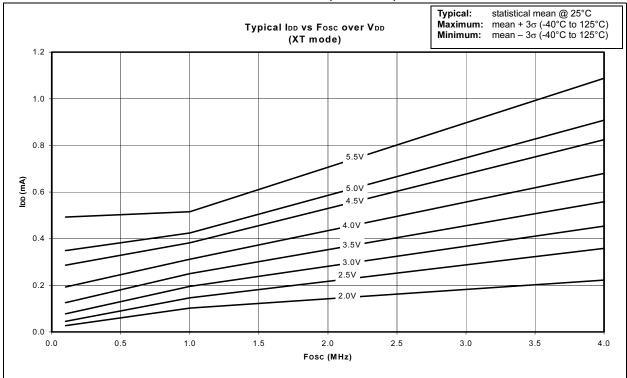

#### FIGURE 18-4: TYPICAL IDD vs Fosc OVER VDD (XT MODE)

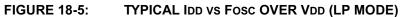

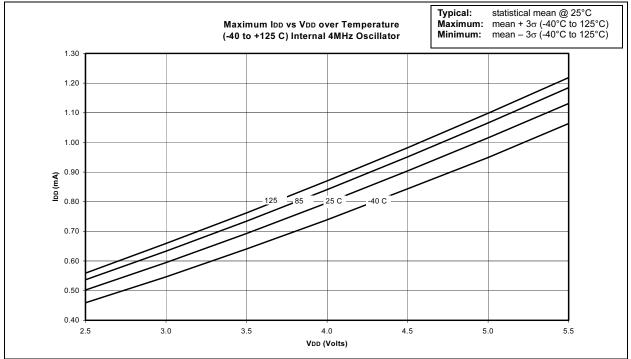

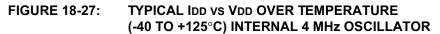

Note: The graphs and tables provided in this section are for design guidance and are not tested.

#### FIGURE 18-26: MAXIMUM IDD vs VDD OVER TEMPERATURE (-40 TO +125°C) INTERNAL 4 MHz OSCILLATOR

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### Rocky Mountain

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-4338

#### Atlanta

3780 Mansell Road, Suite 130 Alpharetta, GA 30022 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

#### Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

#### Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

#### Kokomo

2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387

#### Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401-2402, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-86766200 Fax: 86-28-86766599

#### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521

#### China - Hong Kong SAR

Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 **China - Shenzhen** Microchip Technology Consulting (Shanghai)

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1812, 18/F, Building A, United Plaza No. 5022 Binhe Road, Futian District Shenzhen 518033, China Tel: 86-755-82901380 Fax: 86-755-82966626 **China - Qingdao**

Rm. B503, Fullhope Plaza, No. 12 Hong Kong Central Rd. Qingdao 266071, China Tel: 86-532-5027355 Fax: 86-532-5027205 **India** Microchip Technology Inc. India Liaison Office Divyasree Chambers 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-6334-8870 Fax: 65-6334-8850 Taiwan Microchip Technology (Barbados) Inc., Taiwan Branch 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139 **EUROPE** Austria Microchip Technology Austria GmbH Durisolstrasse 2

Durisolstrasse 2 A-4600 Wels Austria Tel: 43-7242-2244-399 Fax: 43-7242-2244-393

#### Denmark

Microchip Technology Nordic ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH Steinheilstrasse 10 D-85737 Ismaning, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883 United Kingdom Microchip Ltd.

Microchip Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

12/05/02